文献标识码: A

文章编号: 0258-7998(2014)11-0085-03

0 引言

近年来,随着航天航空事业的不断进步,新型的航天产品(如新一代航天器、运载火箭、卫星及航天飞机等)已逐渐问世并向着自动化、智能化的方向发展,其系统构成也变得多元化,对于研究和探索这些先进的技术所需要采集的参数不断增加,因而对于数据存储设备的存储容量、速度、质量、便携性及抗冲击能力的要求也在不断提高[1]。高速数据存储设备不仅在航天产品中扮演重要的角色,在民用航空飞机上也是必不可少的一部分,如飞行数据记录器等[2]。

为了满足飞行数据记录器的高速数据存储需求,本文采用FPGA与DSPIC30F6014A单片机相结合的方式对数据记录器进行了设计。这种记录器既充分发挥了FPGA并行读写大容量Flash数据的能力,也充分利用了DSP-IC30F6014A单片机的单指令周期和并口读写方式等优越性能,通过结合高速文件管理芯片CH378和大容量Flash芯片,从而实现飞行数据的高速U盘存储功能。这种设计方法可以有效地提高U盘读写数据的速度,避免了数据丢失现象,并减小了设备的体积,对体积小、成本低、速度高的飞行数据记录系统设计具有十分重要的意义。

1 记录器总体设计方案

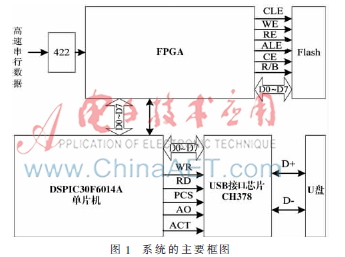

高速数据记录器的系统设计主要框图如图1所示,主要由现场可编程器件FPGA、DSPIC30F6014A单片机、USB接口控制芯片CH378、U盘、数据存储芯片Flash和高速串行数据总线422等模块组成。

整个系统工作过程:首先高速串行数据经过422总线传输给FPGA,然后FPGA对高速数据进行串并转换和编帧处理,通过控制Flash实现高速数据的大容量缓存功能,并将缓存的数据经过并口与DSPIC30F6014A进行通信,最后利用DSPIC30F6014A接收来自FPGA的数据并通过控制CH378将数据存储到U盘中。

2 系统硬件电路设计

2.1 FPGA控制模块

为了解决传统的高速数据记录系统直接由单片机作为主控制芯片造成的数据丢失问题,本设计选用FPGA作为高速数据的缓存控制芯片,以提高系统的可靠性。其中FPGA选用Xilinx公司Spartan-3E系列芯片XC3S500E,该芯片具有功耗低、资源丰富、高性能等特点,其I/O口兼容多种电平标准,有助于与单片机连接通信。内部多达360 Kbit的Block RAM,可配置为双端口RAM,添加必要的控制模块构成高速异步FIFO,为数据的写入及读取提供足够的缓冲空间。同时,它具有4个时钟管理单元,可方便对FPGA的主频分频或倍频,产生不同模块所需的时钟信号,并能够保证这些时钟信号精确稳定。

2.2 DSPIC30F6014A控制模块

系统选用了高性能的DSPIC30F6014A单片机作为U盘数据存储部分的主控制芯片,该单片机为单指令周期,采用哈佛双总线结构,功耗低,驱动能力强,并且I/O端口功能强大,其与外部接口交换数据的效率非常高[3]。内部有8 KB的片内RAM,能够作为高速数据的缓存区,其与FPGA和CH378之间的通信都是通过8位并口的方式进行数据传输的,能够很大程度地提高读写数据的速度。其中DSPIC30F6014A与FPGA的连接示意图如图2所示。

2.3 CH378模块

CH378能够成为U盘记录器首选的U盘接口芯片,是因为该芯片具有比CH376更高的通信速度[4],其可实现12 Mb/s全速通信和480 Mb/s高速通信;且在硬件连接方面,提供了高速8位被动并行接口,可直接挂接在单片机等处理器的数据总线上。其中CH378与DSPIC30F6014A单片机及U盘的部分引脚连接图如图3所示。将TXD引脚接GND,其余引脚悬空,使得CH378被配置为8位并口通信接口。8位并行数据线与单片机的RD口连接,CH378的WR#引脚、RD#引脚、PCS#引脚和A0引脚分别与单片机的RC4~RC1引脚相连,实现8位并口通信接口连接。

2.4 Flash模块

大容量Flash选取了三星公司的NAND Flash K9M-DG08U5M,其内部组织形式为16 G×8 bit,即容量为16 GB,与U盘的存储容量相当,足以满足海量数据缓冲所需的空间;供电电压与FPGA的供电电压相同,避免了为其单独设计电源的麻烦;有8位数据引脚(D7~D0)、片选引脚(CS#)、命令锁存引脚(CLE)、地址锁存引脚(ALE)、写控制引脚(WE)、读控制引脚(RE)、Flash状态引脚(R/B#)、电源及地引脚等,与FPGA的连接非常方便,只需FPGA分配相应的引脚与Flash连接即可。

3 记录器软件设计

系统的软件设计主要由FPGA和DSPIC30F6014A两大主控部分组成,其中采用VHDL语言对FPGA的程序进行编写,其主要实现串行数据的接收和处理、Flash数据读写控制以及与DSPIC30F6014A进行通信等功能;单片机的程序利用C语言进行描述,主要完成对CH378的控制、与FPGA的通信和数据传输的功能。

3.1 FPGA模块程序设计

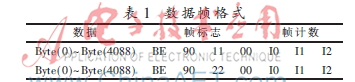

数据在存储时是按照一定的帧格式进行存储的,本系统设计的帧格式如表1所示,每一帧数据由4 089 B数据、4 B帧标志和3 B帧计数组成,其中帧标志分别为BEH、90H、数据流标识(第一路数据为11H,第二路数据为22H)和一个固定位00H。帧计数为3个字节表示,依次先为低位后为高位。

FPGA的主要工作流程图如图4所示,FPGA接收来自422总线接口的串行数据,并对两路数据进行串并转换以及按照一定的数据格式进行编帧处理,之后将编帧处理的数据存入写FIFO中,判断写FIFO半满标志位WR_FIFO_HF是否为高电平。若为高电平则开始往Flash中写入数据,等到写完一页数据后,开始检测单片机的读数据信号是否有效。若有效,将由Flash数据读写控制模块读取Flash中的数据,并暂存在读FIFO,由单片机读取读FIFO中的数据。

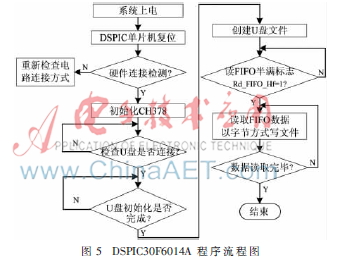

3.2 DSPIC30F6014A模块程序设计

DSPIC30F6014A程序流程图如图5所示。系统上电后,首先单片机复位。然后由单片机向CH378发送硬件连接测试命令CMD_CHECK_EXIST(06H),接着发送数据55H,若硬件连接正常,应由CH378返回数据AAH,否则说明硬件连接不正常或单片机不工作。测试到CH378连接正常后,初始化CH378,并设置工作模式为USB主机方式,然后检测U盘是否连接,如果U盘成功连接并已检测到,则对U盘进行初始化。初始化成功后,创建文件,检测FIFO读半满标志位是否为1,若为1则将FPGA的读FIFO中的数据通过DSPIC30F6014A的控制以字节方式写入U盘文件,数据读取完毕后结束操作。

4 系统调试结果及分析

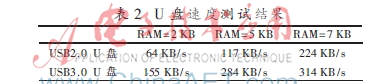

由于U盘的写数据速度会受到U盘的质量、单片机的性能等一些因素的影响,因此为了最大程度地提高数据记录器处理数据的速度,在具体应用之前,对一些性能进行了测试,通过分别往USB2.0和USB3.0的U盘中以字节方式一次性写入100 MB的数据(其中分别选用单片机的RAM的2 KB、5 KB和7 KB作为数据的缓存区),得到了表2的U盘写数据测试结果。结果表明,选用RAM为7 KB并结合USB3.0的U盘可以极大限度地提高数据记录器处理数据的速度。

实验及调试过程中,采用以FPGA为控制核心,产生波特率均为460.8 kb/s的422总线串行数据作为模拟数据源。为了便于分析,数据采用递减的锯齿波。数据存储完毕后,通过计算机读取U盘中的数据,由上位机软件对文件进行分析和绘图显示,图6为数据波形整体图,图7为波形拉伸放大后的波形,从图6和图7中可以看出波形稳定,并无明显丢数现象。

将读出的数据在UltraEdit中打开,如图8所示,并没有出现数据错误并且数据帧格式正确,说明本电路具有可靠的高速数据传输性能。

5 结论

为了满足目前飞行数据记录器对数据的大容量和高速存储的需求,文中提出了一种基于FPGA和DSPIC-30F6014A的数据记录器设计方法,并对数据写入U盘的速度进行了测试。结果表明,高速串行数据经过数据记录器的一系列处理后,最后以并行数据写入USB3.0 U盘的速度可达到314 KB/s,并且通过上位机分析得知数据存储可靠,并无数据丢失现象。该设备还具有设备体积小、成本低和便于携带等优点,很大程度缓解了数据存储的压力,具有很广阔的应用前景。

参考文献

[1] 王伟,费益.民用飞机飞行记录系统研究[J].电光与控制,2013,20(3):73-74.

[2] 卢艳军,牛闯,张晓东.新型通用飞机机载数据记录仪的研究[J].沈阳航空航天大学学报,2014,31(1):82-83.

[3] 王中华,郭改枝,王筱凯.基于DSPIC30F处理器的多路数据采集系统的设计[J].内蒙古师范大学学报,2012,41(6):620-621.

[4] 蔡雪佳,周征翰,伍郁韩.基于USB-Host的大容量数据采集方案研究[J].电子设计工程.2011,19(16):1-3.