摘 要: 介绍了一种新的实时工业以太网总线技术EtherCAT,该工业以太网技术的高度实时性、灵活的拓扑结构、简单的配置方法、技术的开放性等能有效缓解传统以太网总线技术传输数据量小、实时性不高、通信接口不统一带来的工业控制领域瓶颈问题。从EtherCAT的运行原理及其从站硬件电路设计所需芯片选型入手,对芯片的选择以及外围电路设计进行了详细的描述。通过对几种实时工业以太网通信技术的比较证明了该种实时工业以太网技术的数据传输的高速性。

关键词: EtherCAT;PHY芯片;从站控制器;硬件电路

0 引言

随着伺服控制系统日益复杂,传统的现场总线技术已经无法给伺服控制领域带来飞跃性的成就。因此,国内外公司纷纷提出其他工业以太网协议以改善这种情况,其中德国Beckhoff开发的EtherCAT以其卓越的性能及基于普通以太网标准的特点,逐渐成为伺服控制总线技术的主流。因此,深入研究EtherCAT并将其实际应用于伺服控制领域具有重要意义。

1 EtherCAT原理

EtherCAT采用主从式通信结构。主站向各个从站发送以太网数据帧,数据帧经过各个从站时经从站分析其中的指令进行数据的提取或插入从站自身的数据,并将工作计数器(Working Counter,WKC)更新。最终与主站事先设置的预期WKC值作比较,以判断是否经过了所有的从站并被正确处理。由于从站对数据帧的接收与编码及转发、数据的提取与插入都是通过硬件完成,所以数据帧在每个从站停留的时间极小,保证了EtherCAT的实时性。经过最后一个从站处理后的数据帧将返回主站,主站接收并处理后,一次通信完成[1]。这种通信方式不会引起通信通路的堵塞,可保证网络的实时性和正确性。整个通信过程如图1。

2 EtherCAT从站硬件设计

凡是能够发送和接收以太网数据帧的设备都可以作为主站,而且主站功能完全由软件实现[1]。从站的建设则需要专用的集成电路搭建,这也是本文研究的重点。

2.1 EtherCAT从站硬件结构

根据DSP是否支持EtherCAT,相应的设计方法也不同。

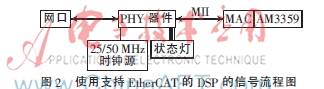

如果使用DSP支持EtherCAT,如TI的AM3359,则信号流程图如图2。

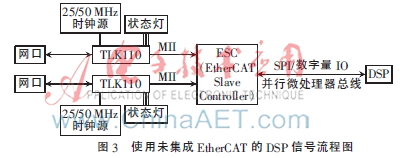

但是目前更多的芯片内部并没有集成EtherCAT模块,在这些芯片上实现性能更加优异的EtherCAT正是本文所要研究的重点。使用未集成EtherCAT模块的DSP建立从站硬件的信号流程图如图3所示[1]。

2.2 EtherCAT从站硬件芯片选择

目前常用的从站硬件建设方法是使用德国Beckhoff公司提供的从站控制器(EtherCAT Slave Controller,ESC),常用的两种从站控制专用芯片如表1所示[1]。

如果只有一个从站,则只需要一个MII端口。但是考虑到EtherCAT可以完成一个主站和多个从站的通信,为长远考虑,选择ET1100。ET1100使用MII接口时,对外接的PHY器件特别是其时钟源有如下要求:

(1)PHY芯片和ET1100使用同一个时钟源;

(2)PHY的TX_CLK信号和PHY的输入时钟之间的相位关系必须固定,最大允许5 ns的抖动;

(3)ET1100不使用PHY的TX_CLK信号,以省略ET1100内部的发送FIFO。

符合以上要求的PHY芯片很多,这里选择TI公司的TLK110。

TLK110是单口10M/100M以太网物理层信号收发器,它支持标准MII接口,供电灵活,3.3 V独立供电,也可以使用3.3 V/1.5 V联合供电。功耗低,小于205 mW,使用25 MHz时钟源。

2.3 EtherCAT从站硬件电路设计

采用的网口为普通网口,给TLK110传递的信号为两组差分信号RD+/RD-和TD+/TD-。另外C_YLW/C_GRN信号灯主要用来判别网口是否正确连接和是否正常工作。TLK110通过MII接口与ET1100通信,其外围电路设计如图4。

MII_RXD[3:0]要使用2.2 kΩ的电阻上拉到3.3 V,因为TLK110的RXD管脚发送网络信号给ET1100,使用上拉一方面可保证发送的信号不存在0或1以外的不确定状态,即信号的确定性;另一方面,管脚上拉提供驱动能力,确保信号能到达ET1100。该PHY芯片管脚所接信号既有模拟信号,又有数字信号,在做PCB设计时容易引起数模串扰。所以在设计原理图时将22号管脚经0 Ω电阻直接接到数字电源。同样的方法处理15、19的地信号,从而保证TLK110所接均为数字信号,便于PCB设计同时避免模数信号串扰引发问题。TLK110的时钟信号由ET1100提供,输入到TLK110的XI管脚,而复位信号则由FPGA提供。要实现EtherCAT的多从站通信,需要两块TLK110芯片,另一块芯片与该TLK110接线一致。

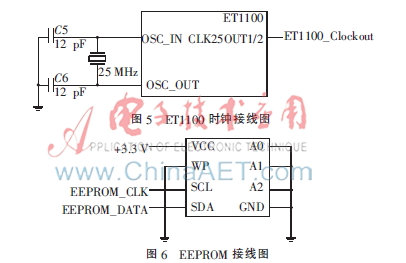

本设计中,ET1100通过SPI接口与FPGA相连,同时通过MII接口连接两个PHY芯片,并给PHY器件提供时钟信号。由于ET1100自身没有如EEPROM一类的存储器件,所以选择带I2C接口的EEPROM来存储设备的配置信息。图5、6为ET1100的时钟接线图以及外挂EEPROM接线图。

ET1100的I/O管脚可以使用3.3 V或5 V供电,并且该电压值决定所有输入输出信号的电压。一般选择 3.3 V电压供电。所有VCCIO和GNDIO之间都要接滤波电容。ET1100内核和PLL供电电压为2.5 V,既可由外部提供也可由芯片内部通过转换I/O口电压得到。同时,VCCcore和GNDcore之间也需要使用滤波电容连接。如图7。

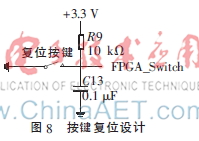

该芯片复位为低电平复位,复位信号来源为FPGA,按键复位设计如图8。

一般情况下FPGA_Switch置于高电平,需要复位时手动按下复位按键,FPGA_Switch变成低电平,此时FPGA经内部编程实现给其他芯片提供低平复位信号。

在本设计中,ET1100不直接与DSP相连,信号流程图如图9所示。

ESC与DSP之间可通过过程数据接口(Process Data Interface,PDI)连接,一般使用的有数字量I/O接口、SPI从站接口、并行微处理器总线接口。由于SPI接口占用的管脚比较少,其他的管脚可以作为普通的I/O口使用,包括16个通用数字输入引脚和16个通用数字输出引脚[1],所以采用SPI接口连接ESC与DSP。一般情况下,ET1100直接与DSP相连,但是这里在中间加入FPGA,虽然运行时间会因此增加几微秒,但是由于硬件电路的可变更性比较低,作为实验板卡的设计,要尽量考虑功能的丰富性以及使用的长远性,所以这里将网口数据通过FPGA,以便于日后需要作出更改时,不必更改硬件线路,只需改写FPGA程序。另外,加入FPGA便于引出测试点,可随时监测传输的数据。

3 实验性能分析

在表2的实验条件下,对各个以太网协议传输速率进行比较,得到如表3[2]所示数据。

表3中的数据显示各个实时工业以太网协议在同一实验条件下的数据传输时间。由表中数据明显可以看出,EtherCAT传输等量数据所用时间远远小于其他以太网协议,即EtherCAT的高速性相对突出。

4 结论

本文针对传统以太网总线技术存在的短板,介绍了一种新的实时工业以太网技术EtherCAT。通过对EtherCAT运行原理的分析,详细描述了如何利用不含EtherCAT控制模块的DSP搭建EtherCAT从站硬件,包括从站硬件设计中的芯片选型以及电路设计,并通过比较各个工业以太网协议的数据传输速率,最终证明了EtherCAT高速传输方面的卓越性能。但是由于时间、实验条件以及个人能力所限,对EtherCAT的探究目前仅限于实验室中。如何将这种优秀的工业以太网技术应用到实际工业控制领域中需要进行更加深入的研究。

参考文献

[1] 郇极,刘艳强.工业以太网现场总线EtherCAT驱动程序设计及应用[M].北京:北京航空航天大学出版社,2010.

[2] ETG. EtherCAT_Introduction_CN[EB/OL].(2012-09-20)[2014-02-26]. http://www.ethercat.org.cn.