张丽,徐妍,马丽珍

(中兴通讯股份有限公司 上海研发中心,上海 201203)

摘要:在微波通信系统中,受天气情况的影响,发送端的时钟频率可能随时变化。在接收端如何进行时钟恢复是微波通信的难点。本文给出了一种基于FPGA的微波无线口时钟恢复的设计。该设计使用FPGA内的PLL和FIFO,实时调整时钟频率,保证接收端恢复时钟的频率与发送端无线口的发射时钟信号频率一致,且减少了PLL个数,避免了PLL失锁及其引发的复位重新锁定过程。

关键词:微波通信;时钟恢复;FPGA;PLL

0引言

微波通信是一种重要的电磁波通信手段,广泛应用于地球与空间站之间、城市两个建筑物之间以及很大的无法实际布设电缆的开阔区域[1]。但是微波通信极易受天气影响,如风沙、雨雾等。微波通信系统需要在不同的天气情况下选择不同的工作带宽和时钟频率,以确保传输质量。对于这种时钟频率可能随时变化的通信系统,如何保证发送端和接收端时钟信号一致、稳定可靠,显得尤为重要。本文在介绍传统的微波时钟恢复方法的基础上,给出了一种基于FPGA的微波无线口时钟恢复的设计并对设计的逻辑控制过程进行了详细说明。

1现有的时钟恢复设计

微波通信系统在不同的环境条件下工作在不同的带宽和时钟频率,如时钟频率为7 MHz、14 MHz、28 MHz、49 MHz 等。现有的微波时钟恢复方法如图1所示。该设计中包含时钟提取模块、分频模块、PLL倍频模块、小数分频模块、时钟选择模块、时钟鉴相模块、时钟调整模块和监控模块。假设有N种不同的时钟频率,在每种时钟频率下,时钟提取模块从空中接收的数据信号帧中提取出的无线口时钟信号通常是不均匀的,会存在一定的脉冲缺失[2],然后N个时钟分频模块将其对应的不均匀的时钟信号分频,将不均匀程度弱化。N个时钟分频模块的分频系数可以不同。PLL 倍频模块将分频模块弱化不均匀程度后得到的时钟信号倍频,倍频系数也可以不同,接下来小数分频模块要根据实际应用环境,利用SigmaDelta 算法实现小数分频[3],将倍频后的时钟信号分频到一个统一的频率,如50 Hz。时钟选择模块从多路时钟信号中选择一路,如当前系统的时钟频率为7 MHz,则选择7 MHz 时钟对应分频得到的50 Hz信号输出到时钟鉴相模块,时钟鉴相模块将50 Hz信号作为参考时钟,与微波通信系统接收端产生的标准时钟分频得到的50 Hz信号比较,得到鉴相值,用鉴相值控制时钟调整模块对接收端产生的标准时钟进行调整,使其跟踪上接收的无线口时钟信号,即发送端的时钟。监控模块实时检测PLL倍频模块输出的时钟,一旦发现PLL 异常无时钟送出时,就复位PLL。

现有的时钟恢复设计通过PLL直接分频和倍频的操作,把不均匀的时钟信号整合成相对均匀的时钟。虽然不均匀的脉冲送入FPGA内部的PLL之后,可能会导致PLL失锁,但是只要不会导致PLL异常,从而出现无法恢复的情况,就能保证恢复出来的时钟信号质量。同时系统还需要一个监控机制,实时检测PLL发送出来的时钟,一旦发现PLL异常,无时钟送出时,就需要复位PLL,PLL从复位图1现有的时钟恢复设计到正常工作一般需要5 ms,这5 ms会导致软件得到的鉴相值跳变,软件也需要做相应的滤波机制。

2基于FPGA的时钟恢复设计

2.1设计组成及功能

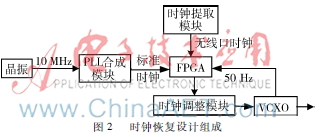

本时钟恢复设计主要由时钟提取模块、晶振、PLL合成模块、FPGA和时钟调整模块等构成,如图2所示。时钟提取模块从空中接收的数据信号帧中提取出无线口时钟信号;自由震荡的晶振输出10 MHz时钟;PLL合成模块根据接收到的无线口带宽模式,输出标准时钟信号;FPGA完成时钟恢复,并把恢复后的时钟分频到50 Hz,与本地VCXO分频得到的50 Hz信号进行鉴相,输出的鉴相值控制时钟调整模块,最终使本地时钟跟踪上接收的无线口时钟信号。

2.2FPGA控制

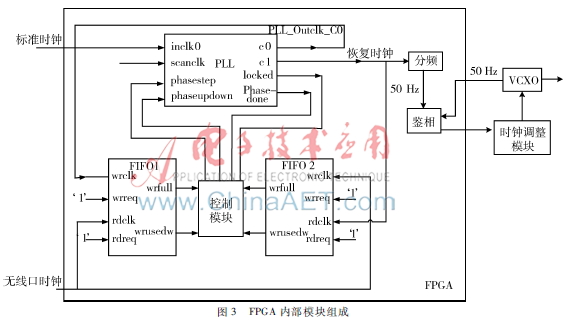

FPGA主要由FIFO模块、控制模块、可调相位PLL模块、分频模块和鉴相模块组成,如图3所示。其中,FIFO1的空/满决定了可调相位PLL的相位调整方向;FIFO2的空/满决定了可调相位PLL的相位调整时机;控制模块根据两个FIFO的空/满以及水位信息输出调整信息给可调相位PLL;可调相位PLL的输出即是与无线口时钟频率一致的恢复时钟;分频模块将恢复时钟分频到50 Hz。

这里FPGA选用ALTERA stratix IV 芯片,此系列芯片的可调相位PLL具有动态相移功能[4],使单个PLL输出的输出相位能够相对于参考时钟动态地被调整。每次相位调整只偏移VCO频率的1/8,并且输出时钟在该相位重配置过程中是有效的。PLL的控制端口:PHASESTEP为高电平时使能动态相移;

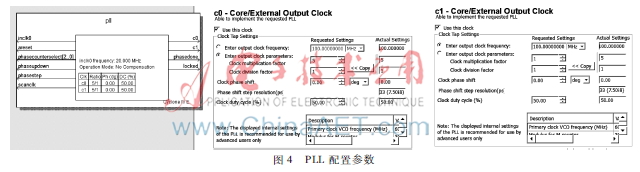

SCANCLK是与PHASESTEP相结合使用的内核自由时钟,最大100 MHz;PHASEUPDOWN选择动态相移方向,1为UP,0为DOWN,且在SCANCLK上升沿寄存在PLL中。 PLL的输出端口:PHASEDONE从低变高时表示相位调整完成,可以启动下一次动态相移;c0/c1为输出时钟端口。在相位可调PLL IPCORE生成过程中需要配置PLL具有动态相位配置功能,且c0端口为输入标准时钟信号的1倍频,而c1端口设置的输出频率要与c0端口一致,如图4所示。

2.3时钟恢复调整过程

可调相位PLL刚上电时,其输出就是输入标准时钟信号,也就是将标准时钟信号直接输出到FIFO1的写时钟端口WR_CLK和FIFO2的读时钟端口RD_CLK,时钟提取模块输出的无线口时钟信号则同时输入到FIFO1的读时图4PLL 配置参数

钟端口RD_CLK 以及FIFO2的写时钟端口WR_CLK。

假设此时FIFO1中保存的数据个数为n1,FIFO1的存储深度为m,即0<n1<m。FIFO1在标准时钟信号上升沿的控制下进行数据写操作,同时在无线口时钟信号上升沿的控制下进行数据读操作,如果标准时钟信号比无线口时钟信号频率低,则经过一段时间后,FIFO1中存储的数图5恢复时钟示意图

据个数会变少,甚至为0(即空);如果标准时钟信号比无线口时钟信号频率高,则经过一段时间后,FIFO1中存储的数据个数会变多,甚至为m(即满)。而FIFO1通过wrusedw[5]端口实时将其中保存的数据个数上报给相位调整控制模块,上报的数据个数就能够反映无线口时钟信号与标准时钟信号的频率(相位)差异信息。相位调整控制模块在收到FIFO1上报的数据个数变少时,据此判断出标准时钟信号比无线口时钟信号频率低,则需提高恢复时钟信号的频率;相位调整控制模块在收到FIFO1上报的数据个数变多时,据此判断出标准时钟信号比无线口时钟信号频率高,则需降低恢复时钟信号的频率,即确定了对恢复时钟信号的频率调整方向。

假设FIFO2中保存的数据个数为n2(n2<m),FIFO2在恢复时钟信号上升沿的控制下进行数据读操作,同时在无线口时钟信号上升沿的控制下进行写操作,FIFO2通过wrusedw端口实时将其中保存的数据个数上报给相位调整控制模块。当出现无线口时钟信号与恢复时钟信号的频率不同时,FIFO2上报的数据个数就会发生变化,此时需要调节。只要相位调整控制模块收到FIFO2上报的数据个数不是n2,即发生了变化,相位调整控制模块就会根据由FIFO1确定的频率调整方向对恢复时钟信号的周期、占空比等进行调整,使恢复时钟信号与无线口时钟信号频率一致。

例如:图5中,当无线口时钟信号出现脉冲连续空缺时,需降低恢复时钟信号的频率,假设恢复时钟信号原来的周期T=10 ns,一个周期内高脉冲持续5 ns,低脉冲持续5 ns,则每次调整时钟频率的1/8,直到FIFO2上报的数据个数不发生变化,则停止对恢复时钟信号的调节。恢复时钟信号在经过上述调节后会逐渐趋近于无线口时钟信号,如图5所示,虽然某些经过调整的周期长度与其他周期不同,但是能够保证在比较长的一段时间内,恢复时钟信号与无线口时钟信号的脉冲个数相同,即这两个信号的频率相同。实际中,该时间的具体数值与FIFO1、FIFO2的存储容量大小有关。此外,需要说明的是,标准时钟信号与无线口时钟信号输入FIFO1的读、写时钟端口可以交换,恢复时钟信号与无线口时钟信号输入FIFO2的读、写时钟端口也可以交换。

3结论

本文给出了一种基于FPGA的微波无线口时钟恢复的设计。该设计使用FPGA内的PLL和FIFO,实时调整时钟频率,减少了PLL个数,避免了PLL失锁及其引发的复位重新锁定过程,提高了微波通信系统的稳定性,降低了系统成本和复杂度。

参考文献

[1] 李兵.微波通信技术的发展与展望[J].电力系统通信,2011, 32(12):4043.

[2] Provigent Ltd. PVG610 Data Sheet PVG610_DSH_002_I [Z].2009.

[3] 李慧.基于VHDL的小数分频器设计[J].微计算机信息,2010, 26(10):192193.

[4] Altera Corporation. Stratix IV Device Handbook Volume 1 [Z]. 2015.

[5] Altera Corporation. SCFIFO and DCFIFO IP Cores User Guide [Z]. 2014.