李传辉,刘纯武,黄芝平

(国防科学技术大学 机电工程与自动化学院,湖南 长沙 410073)

摘要:在100G以太网媒体接入控制器(Media Access Control,MAC)的设计中,需要采用高位宽的并行数据来降低对时钟的要求。在使用并行循环冗余校验(Cyclical Redundancy Check,CRC)时会有一个问题,即需要计算CRC的数据域长度不一定是数据通道位宽的整数倍,导致最后一组数据无法使用数据通道的位宽对其进行CRC计算。为了解决这个问题,本文提出了在帧前填充0的处理方法。仿真和测试结果都验证了该方法的可行性。该处理方法也能应用到其他的通信系统中。

关键词:100G以太网;并行CRC;高位宽

0引言

IEEE在2010年发布了40/100G以太网标准[1],其中MAC层仍然沿用以前的规定未作大的改变,只是100 Gb/s的高速率使得无法沿用以前的方法完成CRC值的计算,为此,本文提出了一种简单有效的解决方法。

1循环冗余校验

在数字通信系统中,为了确保接收到的数据与发送端的数据一致,需要引入差错控制机制。循环冗余校验码由于其误码监测能力强,抗干扰能力优异,被广泛应用于线路检错。循环冗余检验是一种系统的缩短循环码,它采用多项式编码方法[2]。设被检验的信息码有n位,信息系列M={mn-1 mn-2…m0},用多项式M(x)可表示为:

M(x) = mn-1 xn-1 + mn-2 xn-2 + … + m1x1 +m0x0(1)

发送方和接收方使用同一个生成多项式G(x),其是一个k阶的二进制多项式,而且G(x)的首位和最后一位的系数都必须是1,其通用表达式为:

G(x)=xk+gk-1xk-1+gk-2xk-2+…+g1x+1(2)

CRC的计算规则为发送方以xk·M(x)除以生成多项式G(x),将得到的余数R(x)作为校验值,这里的计算规则都是使用二进制运算规则,R(x)可表示为:

R(x)=CRC(M(x))= xk·M(x)mod G(x)(3)

发送方将CRC值随数据一起发送给接收方,接收方对接收到的数据进行CRC值的计算,并将它与发送方的CRC值进行比较。如果数据传输过程中没有错误,两者的校验值就会是一致的,相反如果得到的校验值不一致,就可以判断出数据在传输过程中发生了错误,这时接收方就可以丢弃当前数据或要求发送方重传数据。CRC校验可以百分百地检测出所有的奇数个的随机错误和长度小于等于k的突发错误。

2100G以太网的CRC设计

在以太网通信中,CRC校验具有重要作用。依据IEEE802.3以太网的帧格式(如图1所示),CRC计算的数据区域包括目的地址、原地址、长度/类型和负载数据图1以太网帧格式区域。得到的CRC值作为帧校验序列(Frame Check Sequence,FCS)填充在数据帧尾。其中规定了以太网帧FCS字段的生成算法为CRC32,其生成的多项式表达式为:

G(x)=x32+x26+x22+x16+x12+x11+x10+x8+x7+x5+x4+x2+x+1(4)

在吉比特以上速率的通信系统中,传统的串行CRC校验方法已无法满足要求,所以现在有很多新型并行CRC计算方法[35]。因此在100G以太网中,其CRC也必须采用并行方法,CRC计算的并行位宽就是数据通道的位宽。提高数据位宽可以降低系统的时钟频率,但另一方面随着并行数据位宽的增加会使得CRC电路的延迟时间增加,影响系统的时序性能。经过综合考虑本文中设计的数据并行位宽为320。

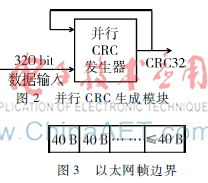

使用320位的高并行位宽会使得数据的处理变得复杂。比如在MAC层的发送方,上层客户每个时钟就会有一组320位40 B的数据送给MAC处理,CRC模块就会使用320位的并行算法对其计算。当前的CRC值只与上一次数据得到的CRC值及当前的数据有关,CRC值初始化为全0,如图2所示。

问题是数据并不一定是40 B的整数倍关系,最后一组数据可能结束于任意位置,如图3所示。

在10G以太网中,数据位宽为64 bit,在参考文献[6]中对这种情况的处理方法为同时设计从8 bit到64 bit的CRC生成模块,根据有效字节数选择使用其中一个。这一方法无疑会占用大量资源,而且利用率低。在100G以太网中数据位宽如果按320设计,需要多达40个不同的CRC模块,加上一个40路的多选一电路,这样的电路在资源使用和时序性能方面都是很糟糕的。所以这一方法无法用于100G以太网中。文献[7]中提到了一种级联结构可以计算任意字节的CRC,但此结构有个很明显的缺点,即级联越大,电路延迟线性增加,320位就需要级联40次,这样的电路无法满足时序要求。文献[2]中利用了CRC校验具有的Magic Number特性,在数据帧后面添加0,使得可以只用一个64 bit的CRC模块完成接收方的CRC校验,但无法在数据发送方完成CRC值的计算。

3帧前补0的并行CRC

上节提到的10G以太网CRC的处理方法都无法直接应用于100G以太网中。下面说明本文提出的方法:帧前补0后再进行CRC计算。

假设原始序列M有n位数据,n不是320位的整数倍。i是一个小于320的整数,且i+n为320的整数倍,在M前增加i个0构造为新序列M′:

M′(x)=0·xi+n-1+…+0·xn+M(x)=0+M(x)=M(x)(5)

可以看出新序列在数值上与原来的序列值是一样的。这个很好理解,就像在十进制中在最前面添加任意位数的0并不会改变这个数的数值一样,当然这在二进制数当中同样适用。新序列的数据长度成为了320的整数倍。

由CRC的计算公式(3)来看,CRC的结果只与序列的数值有关,所以用新序列计算CRC会得到与用原始数列同样的结果。所以依据此原理,只需要设计一个320位的并行CRC模块,计算时使用新的序列送给CRC模块,这个方法可以计算任意字节数据帧的CRC值。

假设有一帧数据负载字节长度为len,加上目的地址、源地址和数据/类型字段的长度14 B,则该帧需要参与CRC计算的数据总长为L=len+14。令n=ceil(L/40),ceil函数得到的是大于等于L/40的最小整数。令rem=mod(L,40)为L/40的余数,表示最后一组数据中有效数据的字节数,对应的com=40-rem表示无效的字节数,V=8*com则表示无效的比特数,也就是需要在帧前添加的0的比特个数。

在客户端向MAC发送数据时,每个时钟MAC层会收到一组数据Cur_data_in[319:0],设计一组初始化为全0的寄存器Last_data_in[319:0]用来保存上一时钟的数据。根据V值的大小将Cur_data_in和Last_data_in组合成一组新的数据Data_to_crc[319:0],其组合关系为:

Data_to_crc[319:0]=Last_data_in[V-1:0]&Cur_data_in[319:V](6)

“&”表示并置连接,处理过程如图4所示。新的序列就是送给CRC模块的数据,从图中可以看到在原始数据的前面添加了V个比特0。每组数据都可以使用320位的并行CRC进行处理,而且最后得到的结果与使用原始数据一样。

4测试及分析

使用硬件描述语言VHDL实现上述的处理过程,并将程序下载到FPGA中进行测试,综合出来的结果表明该方法在面积使用和运行速度方面的效果都很好。测试时客户端给出了一些不同长度的以太网帧,使用Quartus II中的SignalTap工具对数据流进行采样。图5是rem值为18的一帧数据的第一组数据,可以看到data_to_crc在cur_data_in前面添加了22个比特0,这是符合设计预期结果的。图6所示是该帧数据的最后一组数据,根据rem值,cur_data_in只有18 B的有效数据,所以data_to_crc也只取了其中的18 B有效数据,在CC处结束,此时的CRC值就是最终的FCS值为83ACF5C1。

为了验证该值的正确性,使用8位并行CRC算法计算该帧的CRC值,在ModelSim平台下进行了仿真。结果如图7所示,可以看到计算完CC后CRC值为83ACF5C1,与前面的结果一致,说明了该方法得到的结果是正确的。

5结束语

由于100G以太网中会使用很高的并行数据位宽,但是数据帧中需要进行CRC计算的数据长度不一定是位宽的整数倍,本文针对这个问题提出了一种新的处理方法,并且通过了测试。该方法简单有效,能够克服传统方法的缺陷,在性能上有很大的提升。虽然本文是以100G以太网的CRC32作说明,该方法也能很容易地应用于其他的高速通信系统。

参考文献

[1] IEEE. IEEE Std. 802.3ba[S]. 2010.

[2] 彭建辉. 10G以太网接口并行CRC校验的一种简化算法[J].微计算机信息,2006,22(20):213215.

[3] STAVINOV E.A practical parallel CRC generation method [J]. Circuit Cellar, 2010(234):3845.

[4] 毕占坤,张羿猛,黄芝平,等.基于逻辑设计的高速CRC并行算法研究及其FPGA实现[J]. 仪器仪表学报, 2007,28(12):22442249.

[5] KENNEDY C E, MOZAFFARIKERMANI M.Generalized parallel CRC computation on FPGA[C]. Canadian Conference on Electrical and Computer Engineering (CCECE), 2015:107113.

[6] 张友亮,刘志军,马成海,等. 万兆以太网MAC层控制器的FPGA设计与实现[J]. 计算机工程与应用, 2012,48(6):7779.

[7] 刘昭,苏厉,金德鹏,等.10G以太网系统中的并行CRC编解码器的设计[J]. 电子技术应用, 2004,30(4):4750.