文献标识码: A

DOI:10.16157/j.issn.0258-7998.2016.09.038

中文引用格式: 李攀,田文娟,李娟,等. FC协议处理芯片设计与实现[J].电子技术应用,2016,42(9):147-151.

英文引用格式: Li Pan,Tian Wenjuan,Li Juan,et al. The design and realization of FC protocol processing chip[J].Application of Electronic Technique,2016,42(9):147-151.

0 引言

FC网络以其高带宽、低延时、扩展性好、传输可靠性高等特点得到了多方肯定,已广泛应用于民用网络、存储和数据传输领域,并成为我国新一代飞机航电系统通信网络首选[1]。根据国际航电系统的发展趋势和国内对航电系统研究论证的结果,我国采用基于交换架构的FC光纤通道网络作为新一代飞机航空电子系统的统一数据通讯网络,并选用光纤通道航空电子环境匿名签署消息(Fibred Channel Avionic Environment Anonymous Subscriber Messaging,FC-AE-ASM)协议作为航电系统间的通信标准[2]。

本文在深入研究及分析FC网络协议的基础上,结合我国机载航电系统对FC总线网络的应用需求,介绍了一种采用SoC技术实现FC-AE-ASM协议处理芯片的设计与实现过程[4],体系性地解决了制约我国FC网络发展的关键问题及瓶颈,填补了国内空白,实现了我国FC通信网络研制核心器件的自主保障、自主发展。

1 研制总体思路

首先全面解读和正确分析FC网络协议及标准,探索有效实现FC协议技术方法和途径,经过反复的理论分析和仿真、验证,突破FC协议正确解读及分析、关键IP设计与验证、高速串行SerDes电路实现等关键技术,开发FC协议处理关键IP,研制高速SerDes电路,构建芯片FPGA原型,并在多个系统中进行大量的应用验证和优化,为芯片定义、研制及应用打下扎实的技术基础,降低芯片研制风险。

在此基础上,结合系统需求,完成FC-AE-ASM协议处理芯片的定义、体系结构设计及优化;采用软硬件协同设计[3-6]方法完成芯片的逻辑设计、虚拟原型验证、FPGA原型验证、协议符合性测试验证;基于成熟工艺,完成后端物理设计、管壳定制、流片制造、封装与测试;基于FC-AE-ASM协议处理芯片开发配套驱动软件,为自主知识产权的机载FC网络开发提供核心芯片及基础软件。

2 设计与实现

2.1 芯片功能

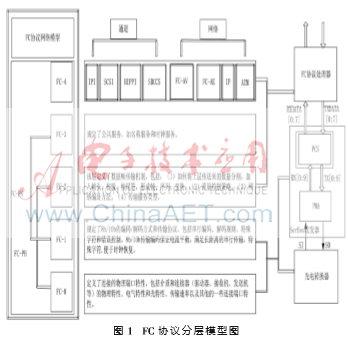

通过对FC网络协议全面解读与分析,确定使用光电转换器和SerDes收发器模拟电路实现FC-0层和FC-1层的功能,FC协议处理器数字电路实现FC-2层到FC-4层的全部功能。如图1所示。

通过对协议分层模型的反复理论分析,采用软硬件协同设计的方式,遵循与性能或者功耗相关的功能用硬件实现、其他用软件实现的原则。研制核心FC-MAC IP核完成FC-1、FC-2层协议的8b/10b编解码[5]、流量控制、FC-FS协议[7-8]核心端口状态机等功能;研制核心FC-AE-ASM协议处理核心IP,完成FC-4层中FC-AE-ASM协议中明确规定的对数据流分包和重组、组帧等内容。结合FC-AE-ASM节点机的功能及性能需求,提出FC-AE-ASM协议处理芯片的主要功能如下:

(1)内嵌高性能PPC460处理器,工作频率125 MHz/250 MHz可配置;

(2)FC-FS协议处理功能和性能:支持1、2、3、6类服务和N、F、E、B端口;传输速率:1.062 5 Gb/s、2.125 Gb/s可选;支持帧的CRC校验、信用管理;支持统计信息收集。

(3)集成FC-AE-ASM协议处理引擎:FC-AE-ASM协议通信处理功能;FC网络系统时统功能;FC网络运行控制功能;双余度FC链路功能。

(4)集成FC高速串并转换SerDes。

(5)存储器控制器。片内存储器资源128 KB;片外存储器接口:片上处理器程序加载Flash 32 MB;主机访问Flash 32 MB;片上处理器程序扩展SSRAM 64 MB。

(6)外围接口。高速PCIe主机接口支持4x、1x模式,通道速率为2.5 Gb/s;高速RapidIO主机接口支持自适应的4x、1x模式,3种不同线速率:1.25 Gb/s、2.5 Gb/s、3.125 Gb/s;串口、GPIO接口;JTAG调试接口。

2.2 芯片架构设计

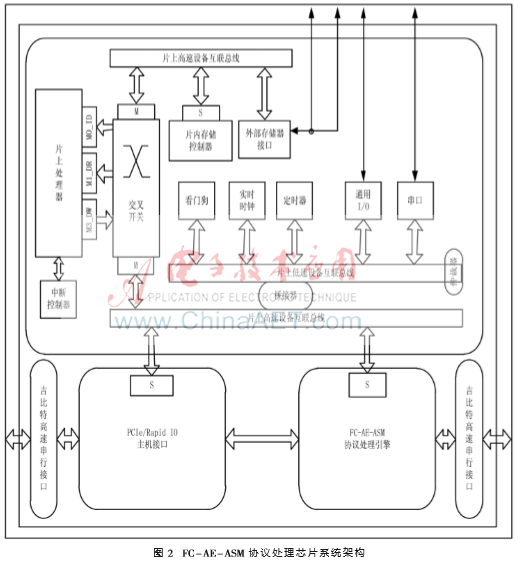

根据对FC协议标准的理解和系统应用功能及性能需求的分析,提出FC-AE-ASM协议处理芯片的体系架构如图2所示。

FC-AE-ASM协议处理芯片提供ASM协议处理功能,其工作原理如下:

(1)发送数据时,由主机在内存中按ASM消息格式准备消息,之后启动消息发送;主机接口DMA将数据从主机内存的消息发送缓冲区中搬移到片内帧缓冲;发送控制模块将数据输出到SerDes模块,SerDes模块将输入的并行数据流转换成2.125 Gb/s/1.062 5 Gb/s的高速串行数据流输出到片外;

(2)接收数据时,SerDes模块将2.125 Gb/s/1.062 5 Gb/s的片外串行输入数据流转换为并行数据流;接收控制模块接收帧时查询通信配置表,如果能查到相应的配置项,则将ASM数据搬移到FC接收缓冲区,再将其搬移到片内消息帧缓冲;接收管理模块判断消息所对应的通信配置索引项的位置,然后判断消息接收缓冲区状态,如果可以接收则计算出缓冲地址,并启动主机接口模块的DMA,将ASM数据帧从片内消息帧缓冲搬移到主机内存的接收缓冲区中;消息的接收方式可以配置为中断主机或主机查询,如为中断方式,则将消息ID保存到中断相关寄存器中,发中断给主机。

FC-AE-ASM协议处理芯片提供ELS帧实现网络管理功能,其工作原理如下:

(1)发送ELS帧时,片上处理器按照ELS帧格式组帧,并写入ELS帧发送缓冲,启动发送,由发送控制模块将要发送的帧从ELS发送缓冲区发送到FC MAC控制器的客户端接口;FC MAC控制器负责将ELS帧输出到SerDes模块;SerDes模块将接收到的并行数据流转换串行数据输出。

(2)接收ELS帧时,SerDes模块将接收到的串行数据转换为并行数据流;FC MAC控制器将SerDes输出的并行数据转换为32位的数据流从客户端输出;接收控制模块从FC MAC控制器的客户端接口将ELS帧接收到ELS帧接收缓冲区,更新接收头指针,交由片上处理器处理。

2.2.1 硬件设计

根据系统架构设计得出硬件系统,包括FC-AE-ASM协议处理模块、PCIe主机接口、RapidIO主机接口、高速串并转换SerDes、PPC460嵌入式处理器、其他片上资源等。

FC-AE-ASM协议处理模块支持256个非数据块消息和16个数据块消息的收发控制,支持ELS帧的收发,提供网络管理硬件支持,具备信息交互区及命令交互寄存器,用于主机与片上处理器之间交互网络管理信息数据,设备控制处理功能(包括设备软复位、ASM数据收发使能和禁止、主机和设备之间的硬件信号量、FC设备的WDT定时功能、硬件设备心跳控制和检测)、双余度控制功能、FC网络系统时统功能。

PCIe主机接口完成从PCIe串行链路到用户端逻辑之间的PCIe协议转换和数据高速传输。该PCIe主机接口由PCIe协议处理模块和DMA模块两部分组成。PCIe协议处理模块实现了协议规定的事务层、链路层、物理层逻辑子块的功能,支持端点操作,为用户提供全面的底层PCIe状态信息。DMA模块支持最多2个S2C及2个C2S DMA通道,支持用户端直接控制。

RapidIO主机接口由6部分组成:逻辑及传输层模块(实现逻辑及传输层协议包括负责事务组包、拆包等功能)、物理层模块(实现物理层协议包括包的控制符号传送、流量控制、错误管理等功能)、寄存器管理模块(负责对寄存器进行读写操作)、寄存器组模块(集中实现各层寄存器)、时钟及复位模块、应用模块(实现DMA、门铃操作以及片内资源访问等功能)。

高速串并转换SerDes主要完成FC-1层的8b/10b编解码、串化/解串和不同时钟域数据的时序转换。

PPC460嵌入式处理器提供强大的数据处理及控制能力,通过工作在较高时钟频率的PLB总线和外围设备通信,完成FC速率配置,ELS帧的接收、发送以及FC MAC的初始化配置。

其他片上资源包括片上总线、中断控制器、定时控制器、看门狗、通用输入输出接口、UART接口、调试接口等。

2.2.2 软件设计

FC-AE-ASM协议处理芯片的相关软件为各个系统提供使用FC-AE-ASM协议处理芯片实现FC网络数据传输的API接口。该软件主要分为:(1)运行在宿主机上由用户程序调用的FC-AE-ASM接口驱动软件、PCIe接口驱动软件、RapidIO接口驱动软件;(2)运行在FC-AE-ASM协议处理芯片上的FC-AE-ASM接口底层传输软件,及其他资源模块(VIC、Uart、Timer等)的驱动软件。

FC-AE-ASM协议处理软件的核心部件为FC-AE-ASM接口软件,包含FC-AE-ASM协议通信功能、设备管理功能、时统管理功能、网络管理功能。实现结构框图如图3所示。

FC-AE-ASM接口软件功能如下:

(1)FC-AE-ASM协议通信功能。实现对ASM消息处理程序的注册、注销,通信表的加载和卸载,FC-AE-ASM协议非数据块消息的封装,ASM协议通信的启动、停止控制,ASM消息的发送、接收控制等。航电应用通过调用ASM通信接口实现不同硬件模块之间的数据通信交互;

(2)网络管理功能。实现网络初始化控制,网络系统管理器控制权争夺控制。网络系统运行结构控制,网络上/下线管理(linkup/linkdown),网络上/下网控制(online/offline),网络系统健康监控,网络时统控制,网络配置数据加载及固化。航电应用系统管理通过调用网络管理接口实现对FC网络运行状态的控制及管理;

(3)设备管理功能。实现设备的打开、关闭,设备软复位,设备自测试,设备状态获取,软件版本获取。航电应用系统管理通过调用设备管理接口实现对FC网络设备的管理功能;

(4)时统管理功能。提供一组网络时钟同步驱动控制接口,包括时钟同步模式设置、时钟同步使能、时钟同步禁止、任务系统RTC设置、任务系统RTC获取、任务系统同步监控门限设置、网络日历信息设置以及网络日历信息获取功能。

2.3 物理设计与实现

FC-AE-ASM协议处理芯片设计规模为1 730余万门,芯片面积为12.3×12.3(mm2),芯片工作温度范围-55 ℃~125 ℃。

2.4 芯片流片、封装

FC-AE-ASM协议处理芯片的流片制造采用SMIC 0.13 ?滋m Logic工艺,内核电压1.2 V,IO电压3.3 V,封装形式为CBGA440。

2.5 芯片验证

2.5.1 验证策划

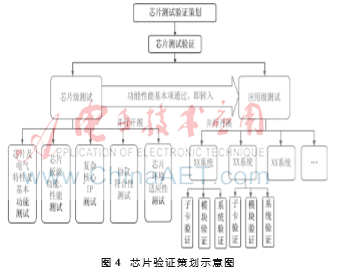

根据芯片需求以及功能定义,对芯片测试、验证进行详细策划,编制芯片样片测试规范,依据测试规范对芯片进行芯片级及系统应用级验证,以保证芯片功能、性能、对外接口、电气特性以及兼容性满足应用要求。

芯片级测试内容包括:电气特性及基本功能测试、板级功能及性能测试、复杂核心IP测试、协议符合性测试及芯片的环境适应性测试,以上测试可以基于芯片样片同步并行开展。芯片应用级验证主要结合实际研制项目开展基于子卡、模块及系统级的应用验证。具体实施如图4所示。

2.5.2 验证实施

芯片测试验证从芯片级测试到应用级测试,涵盖FC接口2.125/1.062 5 Gb/s 2种速率、RapidIO接口1线/4线2种模式和3.125/2.5/1.25 Gb/s 3种速率、PCIe接口1线/4线2种模式、PowerPC 250/125 MHz 2种时钟频率,共计32种场景,每种场景下开发测试程序807项。

2.5.3 验证结果

经测试芯片电气特性符合设计指标要求,复杂核心IP SerDes测试符合测试标准,协议符合FC-FS、FC-PI协议要求。系统应用测试功能、性能满足系统应用需求,满足环境适应性设计需求。主要指标验证结果如表1所示。

3 技术优势

市场上存在的一些FC网络产品大多都采用FPGA或ASIC方式实现,存在板面积大、功耗高、可靠性低、通用性差等不足,已不能满足系统小型化、高可靠性的要求。

与市场上的FC网络产品相比,FC协议处理核心芯片符合系统小型化、低功耗、高性能、高可靠性、高度综合、复杂恶劣环境等应用要求。

以基于该芯片研制的PMC卡和市场上同类产品相比较,主要指标对比情况如表2所示。

由表2可以看出,基于该芯片研制的PMC卡与市场上同类产品相比显著提高了功能、性能、可靠性及FC核心产品的自主保障能力。

4 总结

本文针对机载航电系统对FC总线网络的应用需求,以及我国在FC网络产品方面受制于人、系统功耗大、维护成本高的现状,提出了一种采用SoC技术实现FC-AE-ASM协议处理芯片的设计方法。该芯片功能及性能符合设计要求,现已成功应用在多个系统中。应用结果表明,该芯片符合协议、系统等的要求。该芯片的研制体系性地解决了制约我国FC网络发展的关键及瓶颈,填补了国内空白,实现了我国FC通信网络研制核心器件的自主保障和自主发展。

参考文献

[1] 李攀,田泽,蔡叶芳,等.基于FPGA的双通道FC数据采集卡设计[J].计算机技术与发展,2013,23(7):179-182.

[2] SULLIVAN W.Fibre channel: replacement for MIL-STD-1553&next generation military data bus[EB/OL].1998-09.

[3] 淮伟华.基于FC-2协议的SoC软硬件协同设计与验证[D].西安:陕西科技大学,2009.

[4] 黎小玉,田泽.FC协议分析仪软件设计与实现[J].计算机技术与发展,2013,23(8):31-34.

[5] 田泽,韩炜,蔡叶芳,等.基于FC接口的SoC软硬件协同设计验证平台构建与实现[C].第十三届计算机工程与工艺会议论文集.西安:西北工业大学出版社,2009.

[6] 张艳,胡桂.SOC设计中的核心技术[J].微计算机信息,2007,23(10-2):110-112.

[7] 张丹,董雷刚,祝裕璞,等.基于SOPC嵌入式系统中软硬件协同设计方法研究[J].大庆师范学院学报,2012,32(6):40-44.

[8] ANSI Fiber Channel Fhysical and Signaling Interface(FC-PH),X3[M].US:ANSI,1994.

[9] ANSI Fiber Channel Framing and Signaling-2(FC-FS-2),Rev0.01[M].US:ANSI,2003.