文献标识码: A

DOI:10.16157/j.issn.0258-7998.2016.08.021

中文引用格式: 王龙,杨承志,吴宏超,等. 基于FPGA的数字基带多模雷达信号源设计[J].电子技术应用,2016,42(8):87-90.

英文引用格式: Wang Long,Yang Chengzhi,Wu Hongchao,et al. The design of digital multi-mode radar signal generator based on FPGA[J].Application of Electronic Technique,2016,42(8):87-90.

0 引言

随着雷达技术的快速发展,采用复杂调制样式、具有低截获概率(Low Probability of Intercept,LPI)特性的雷达信号被广泛运用于火力引导和预警探测中,使得传统电子侦察设备很难截获到这类信号,需要设计一个能够模拟这些复杂调制样式的雷达信号的设备对现有和新研制的电子侦察设备进行测试,检验电子侦察设备对LPI雷达信号的有效性和可靠性[1-3];此外,在生成式欺骗干扰中,需要根据侦察到的雷达信号的调制类型和参数产生相应的干扰信号对目标实施欺骗干扰[4,5],因此有必要研究一个能够灵活产生多种调制样式的多模雷达信号源。文献[2]中提出一种采用ARM输入雷达参数,并通过USB接口将数据传输到DSP中进行参数处理,然后传递给FPGA合成多种模式的雷达信号的方法,但这种产生多模雷达信号的方法具有整体结构复杂、占用资源多、不利于小型化的缺点。本文设计了一种基于FPGA的多模雷达信号源产生结构,在FPGA中构建微控制器实现参数的处理,降低系统的复杂度,提高了系统的集成度。

本文选用Xilinx Zynq-7 系列xc7z010clg400 FPGA芯片[6]实现系统设计,上位机通过网口向FPGA中构建的微控制器(MCU)发送信号描述参数,微控制器经过计算和处理得到寄存器配置参数,并通过AXI(Advanced eXtensible Interface)总线[7]对自制的多模信号源IP核进行配置,产生特定调制形式和特定参数的雷达信号。由于整个数字系统都在一片FPGA上实现,降低了外部电路的设计难度,易于实现系统的小型化设计,同时关键的多模信号源产生模块被封装成具有AXI总线结构的IP核,提高了模块的灵活性、易用性和重用性,通过AXI总线可以很方便地与微控制器连接实现,并且在AXI总线上挂载多个多模雷达信号源IP核,可以模拟多部雷达信号,为电子侦察设备对同时到达信号的性能检测和生成式同时多目标干扰提供硬件支持。经测试,该IP核最高可工作在500 MHz 的时钟频率下,即数字信号的输出速率能达500 MS/s。输出的信号调制形式包含常规脉冲信号、线性调频信号、相位编码信号、频率捷变信号、重频抖动信号、重频参差信号和其他复合调制信号等。

1 关键技术研究

1.1 雷达信号模型

雷达信号的一般表达式可以用下式表示:

其中,A(t)表示信号的时域包络,f(t)为信号的频率调制函数, 为信号的相位偏移调制函数。从式中可以看出,雷达信号的调制方式不外乎幅度调制、频率调制、相位调制、时间调制这四种方式及这四种调制方式的组合,其中幅度调制常见的是矩形脉冲调制,故本文不对脉冲调制作过多研究。

为信号的相位偏移调制函数。从式中可以看出,雷达信号的调制方式不外乎幅度调制、频率调制、相位调制、时间调制这四种方式及这四种调制方式的组合,其中幅度调制常见的是矩形脉冲调制,故本文不对脉冲调制作过多研究。

以线性调频信号为例,线性调频信号是信号的瞬时频率随时间线性变化的信号,其瞬时频率可以用式(2)表示:

其中,f0为信号的初始频率,K=B/T是信号的调频斜率。

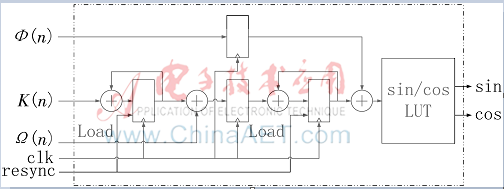

1.2 DDS原理和模块设计

数字频率合成器DDS(Direct Digital Synthesizer)常用于数字信号产生,主要包括相位累加器和正弦计算器两部分,其中正弦计算多采用查表的方法实现。DDS技术同模拟方法相比,具有稳定可靠、波形产生灵活、精确度高的优点,因此得到了广泛应用[8]。本文根据生成线性调频信号的需求,设计了如图1所示的二阶相位累加结构。雷达信号的通用表达式作离散化,可用式(3)表示:

图1 DDS模块结构原理框图

其中K(n)为时刻的调频斜率, 为时刻的频率偏移,

为时刻的频率偏移, 为时刻的相位偏移。通过控制这三个量,即可输出单载频信号、线性调频和相位编码等信号调制形式。为了减少查找表对FPGA中RAM资源的消耗,本文采用相位抖动和平衡DAC方法[9,10]对DDS 结构进行改进,抑制了相位截断误差并减小DAC非理想特性的影响,仿真结果表明采用该方法能够有效节约73%的RAM资源。

为时刻的相位偏移。通过控制这三个量,即可输出单载频信号、线性调频和相位编码等信号调制形式。为了减少查找表对FPGA中RAM资源的消耗,本文采用相位抖动和平衡DAC方法[9,10]对DDS 结构进行改进,抑制了相位截断误差并减小DAC非理想特性的影响,仿真结果表明采用该方法能够有效节约73%的RAM资源。

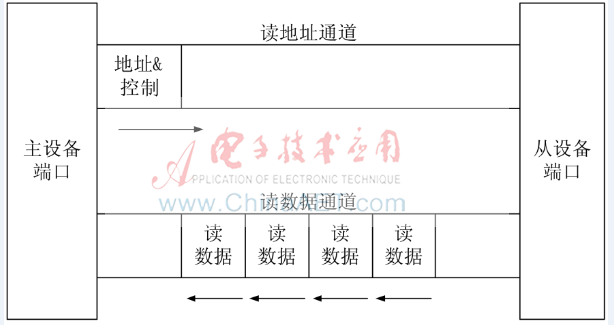

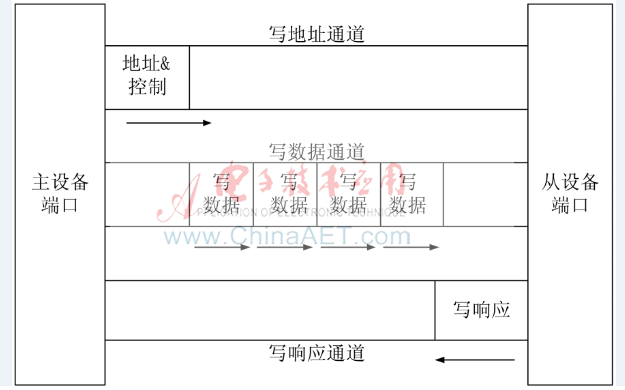

1.3 AXI总线协议

AXI总线是ARM公司提出的一种片内总线协议,该协议是先进微控制器总线结构(Advanced Microcontroller Bus Architecture,AMBA)协议[7]中最重要的部分,面向高性能、高带宽、低延迟的片内总线。Xilinx公司提供的IP核基本都采用这种总线结构,显著提高了系统设计的效率,降低了系统开发的复杂度。为了增强多模雷达信号源模块的灵活性和重用性,本文将多模雷达信号源模块分装成具有AXI总线结构的IP核。图2为AXI总线读写通道结构。

(a)AXI总线读通道结构

(b)AXI总线写通道结构

图2 AXI总线读写通道结构

AXI总线的地址、控制和数据相互是分离的,支持非对齐的数据传输,同时在猝发传输中,只需要首地址,同时具有独立的读写数据通道并支持乱序访问,能更加容易进行时序收敛。AXI 是AMBA 中一个新的高性能协议,并且兼容原有的AHB和APB总线,使得基于原有总线结构的组件能够很好地与AXI总线结构结合使用。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2 多模信号源IP核设计

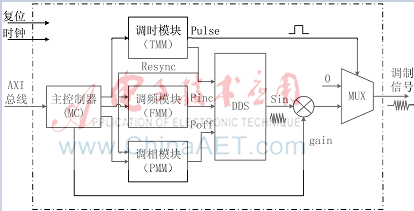

本文将所设计的多样式雷达信号源分成时间调制模块(Timing Modulation Module,TMM)、频率调制模块(Fre-quency Modulation Module,FMM)和相位调制模块(Phase Modulation Module,PMM)3种调制模块,每个模块分别负责产生时域调制控制信号、频域调制控制信号和相位调制控制信号。IP核的顶层结构如图3所示。

图3 多模信号源IP核结构框图

其中主控制器包含所有信号样式的配置参数寄存器和控制寄存器,MCU通过AXI总线将配置参数写入到配置寄存器中,并通过读写控制寄存器实现对信号源的发射使能、复位等控制。调时模块TMM产生单比特脉冲控制多路选择器(MUX)在高电平期间选择DDS 模块的信号输出,而在低电平期间选择“0”输出,同时产生同步信号(Resync)给调频模块FMM、调相模块PMM和DDS模块控制模块的同步。调频模块产生相位增量值(Phase Increase,Pinc)控制信号的瞬时频率产生调频类信号。调相模块产生相位偏移值(Phase Offset,Poff)控制DDS模块输出信号的瞬时相位偏移值,产生调相类信号。DDS模块是信号的产生单元,在调时模块、调频模块和调相模块的控制下产生特定调制类型的连续信号,经乘法器按指定衰减量衰减后,通过多路选择器产生具有调时特征的信号,然后输出特定样式的雷达信号。

3 多模基带雷达信号源总体结构设计

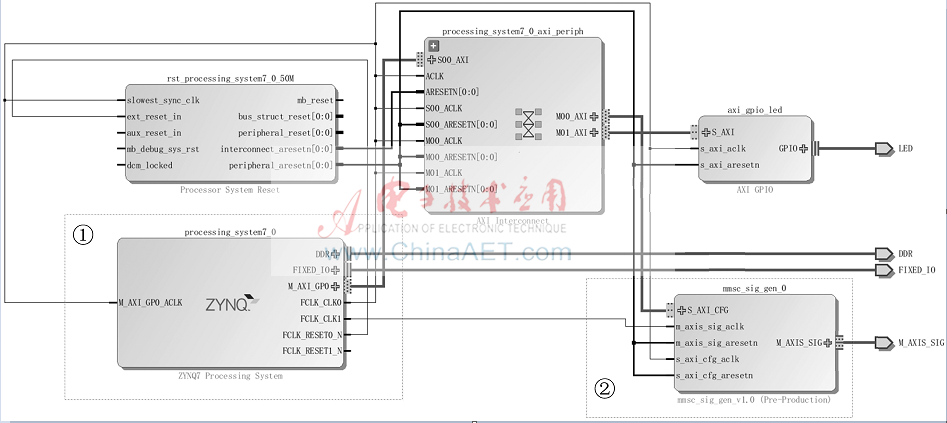

多模基带雷达信号源总体设计结构如图4所示。上位机软件通过网口发送信号描述参数给FPGA中的微控制器,微控制器通过计算和处理将信号描述参数转换为多模雷达信号源IP核需要的寄存器配置参数,然后多模雷达信号源IP核产生数字雷达信号并通过DAC输出模拟基带雷达信号。

在Xilinx提供的Vivado编程开发环境中,利用块设计方式搭建FPGA上的系统结构,最终得到的块设计图如图5所示。其中①为cortex-A9硬核,负责与上位机的网口通信,接收上位机下发的信号描述参数并通过计算处理产生多模雷达信号源IP核所需的配置寄存器参数。②为本文所设计的多模雷达信号源IP核,在cortex-A9硬核的控制下生成相应的基带雷达信号。

图4 多模基带雷达信号源总体结构框图

图5 多模基带雷达信号源块设计视图

4 测试与分析

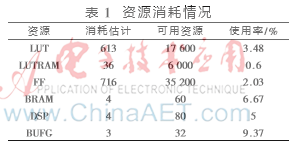

本文在Xilinx公司提供的FPGA开发环境Vivado 2015.4[11]下使用Verilog 语言进行编程,将关键的多模信号源模块分装成具有AXI总线结构的IP核,使得模块可以方便地挂载到AXI总线系统中。将系统工作时钟约束到500 MHz ,进行综合实现,布局布线的结果表明系统能够满足500 MHz 时钟的时序要求,并且占用资源少。其中多模信号源IP核仅占用了4个DSP核和2个BRAM(Block RAM),分别占总资源的3.3%和5%。具体资源消耗见表1。

将多模雷达信号源的系统工作时钟设置为250 MHz,信号模式设置为线性调频脉冲信号。信号的具体参数如表 2所示。

5 结论

多模雷达信号源在电子侦察设备的检测和生成式干扰信号生成方面具有重要的应用价值。本文提出的基于FPGA的多模雷达信号源具有占用资源少、结构简单、生成信号多样的特点,能够产生常见的调时、调频和调相信号以及这些调制方法的组合。最高输出信号的数据速率为500 MHz。

参考文献

[1] 吴宇,顾村锋,赵学州.低成本多通道注入式雷达信号模拟源设计方法[J].舰船电子工程,2016(2):58-60.

[2] 史高,胡兆峰.基于BF533和FPGA的雷达信号模拟器设计实现[J].电子科技,2015(1):32-35.

[3] 李杨.多模式软件化雷达波形产生的技术研究[D].成都:电子科技大学,2013.

[4] 何亮,李炜,郭承军.生成式欺骗干扰研究[J].计算机应用研究,2016(8).

[5] 马克,孙迅,聂裕平.GPS生成式欺骗干扰关键技术[J].航天电子对抗,2014(6):24-26.

[6] Xilinx Corporation.Zynq-7000 All Programmable SoC Overview[EB/OL].(2016-01).http://www.xilinx.com/support/docu mentation/data_sheets/ds190-Zynq-7000-Overview.pdf.

[7] ARM Corporation.AMBA AXI Protocol(Version:2.0) Speci-fication.[EB/OL](2010-3-3).http://www.arm.com/products/system-ip/amba- specification.php.

[8] 顾赵宇,王平,傅其详.一种基于DDS的信号源的设计与实现[J].现代电子技术,2015,38(5):51-53.

[9] 王硕,马永奎,高玉龙,等.基于FPGA的改进结构的DDS设计与实现[J].微电子技术,2016(3):28-30.

[10] Xilinx Corporation.LogiCORE IP DDS Compiler v6_0[EB/OL].(2013-11-18).http://www.xilinx.com/support/docu-menta-tion/ip_documentation/pg141-dds-compiler.pdf.

[11] Xilinx Corporation.Vivado Design Suite User Guide:Designing with IP.[EB/OL](2014-5-1).http://www.xilinx.com/support/documentation/sw_manuals/ug896-vivado-ip.pdf.