黄顺福

(上海贝尔股份有限公司,上海 201206)

摘要:针对目前在生产测试平台中广泛使用的高密度VXI PXI Digital I/O板卡容易损坏且故障定位困难、不便维修和维护的情况,开展了对其进行故障定位的诊断算法研究。研究了包括各种可能出现的错误模型及其相互关系,以及检测和定位这些错误模型的相应算法,并应用相应的算法成功地开发了高密度VXI PXI Digital I/O板卡的自动化诊断系统,大幅提高了生产效率,降低了维护成本,提高了经济效益。

关键词:PXI;VXI;Digital I/O;错误模型;诊断算法;自动化诊断系统

中图分类号:TP29文献标识码:ADOI: 10.19358/j.issn.1674 7720.2016.20.021

引用格式:黄顺福. 基于VXI PXI Digital I/O卡的诊断算法研究[J].微型机与应用,2016,35(20):75 78.

0引言

在Alcatel-Lucent的移动通信设备基站生产制造中,广泛采用了统一的测试平台,以满足纷繁复杂的不同系列产品的需要,如3G CDMA的BTS数字系统测试平台(DTP),射频系统测试平台(RTP),4G LTE BTS的公共测试平台(CTP)。这些测试平台中的核心部分都使用了VXI或PXI设备,其中对于生产测试最关键的模块设备是VXI或PXI Digital I/O板卡模块。

由于生产制造平台产量大,当VXI或PXI Digital I/O板卡某一线不良时,如不能及时排除故障,将造成该测试平台停产,严重影响产能。平台上的VXI或PXI Digital I/O线往往都超过90线以上,属于高密度,如果仅仅是用人工置1或置0的方法,不仅检测时间长,实际上很难精确找出哪一线有问题,很多情况下的检测都呈现出无故障的现象,但实际上又不能使用,这给平台维护人员的维修诊断造成巨大困难。高密度VXI或PXI Digital I/O板卡价格昂贵,大量购买新的VXI或PXI Digital I/O板卡来更换,会给公司造成很大的经济压力。鉴于此,本文开展了VXI或PXI高密度Digital I/O板卡的诊断算法研究,以便实现VXI或PXI Digital I/O板卡的高效自动化诊断。

1VXI或PXI高密度Digital I/O板卡的抽象模型及诊断模型

1.1VXI或PXI高密度Digital I/O板卡的抽象模型简介

VXI或PXI高密度Digital I/O结构框图见图1(a)。不同厂家的具体产品的电路会有所不同,但其原理是相同的。其主要由0~N个端口(Port)及端口选择控制器(Port Control)所组成。端口连到被测系统BTS的BBS(基带部分),其作用是采集相应位数的数字信号,或发出相应位数的指令,读回相应的响应。端口选择控制器用于选择相应的端口。诊断时需要每次读/写1位,由控制器发出,通过Data BUS总线送到端口。例如:Port0为8位,发出对Port0 D1位置1的指令0000 0001;发出对Port0 D2位置2的指令0000 0010,依次类推。由此可见,当每次读/写1位指定位时,VXI或PXI高密度Digital I/O电路可以抽象为图1(b)所示结构模型[1-3]。

从图1(b)中可看出,对指定1位的读写可看成是D1~D8的列与Port 0~Port N的行的交点的读写。对于选择Port 0~Port N中的哪一行,相当于是行译码器的行为模型;选择D1~D8列中的哪一列,相当于是列译码器的行为模型;而交点相当于一个元件单元,实际上还应该包含读/写电路、线驱动电路、锁存电路等。由于这些电路元器件的关联的复杂性,使得有些故障现象容易被认为是正确的结果而很难被诊断[4]。例如,Port 0 D7单元有卡死故障,其被卡死在1。当读1时,其是正确的;当置0时,由于周围邻居某0单元恰好在此状态下,又与卡死单元有某种类型的耦合,因此读0时也是正确的。在这种情况下,读0读1都正确,这时就无法检测出Port 0 D7的故障。下面叙述几种主要的错误模型。

1.2卡死错误模型

卡死错误定义为某单元或线总是0(SA0)或1(SA1);它总是在状态0或状态1,不能改变到其相反的状态。如图2(a)所示,单元状态原来为0,当置0时,还是回到0状态;当置1时,其还是到0状态,所以为SA0错误。如图2(b)所示,单元状态为原来为1,当置1时,为1;当置0时,仍然为1,故为SA1错误。对于卡死错误检测必须满足:所有的单元必须通过读一次0和读一次1进行检测。

1.3迁移错误模型

迁移错误是卡死错误的一种特殊情况,它定义为当0→1迁移时,单元或线向上迁移的错误。同理,当1→0迁移时,单元或线向下迁移的错误。向上迁移错误记为:TF<↑/0>;向下迁移错误记为: TF<↓/0>。如图2(c)所示,当单元或线在状态1(S1)时,置1时为1,置0迁移到状态0(S0)正确;当单元或线在状态0(S0)时,置0时为0,置1时仍为0,没有迁移到S1,所以为TF<↑/0>错误。实际迁移模型见图2(d),原来Q状态为0,在触发器的S端置1时,Q端应翻转为1,但仍旧是0,所以把它归类为TF<↑/0>。之所以不把迁移错误归入卡死错误,是因为其他错误形式(如耦合错误)可以使它翻转。对于迁移错误的检测必须满足:所有的单元必须进行一次向上迁移和一次向下迁移以及每次迁移后的读。

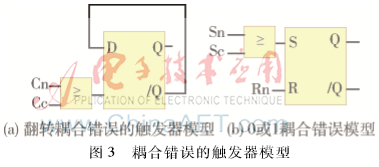

1.4耦合错误模型

耦合错误是由迁移所引起,其发生在两个单元之间。耦合错误的定义如下:在一个单元产生一个向上或向下迁移而引起第2个单元内容的变化。翻转耦合错误(CFin):在一个单元产生一个向上或向下迁移而引起第2个单元内容的翻转。CFin模型见图3(a),Cn为正常时钟输入,Cc为额外时钟输入。当Cc发生向上状态迁移时,则翻转了D触发器的内容。单元j产生一个单元i的耦合错误,单元j称作耦合单元。如果Ci为<↑;>,则表示为单元j引起单元i一次向上或向下的迁移。对于翻转耦合错误的检测必须满足:对于所有被耦合单元,通过触发耦合元产生可能的各次翻转耦合后,读各次翻转耦合的被耦合单元(条件是各次翻转耦合不能相互屏蔽)。这里讨论的耦合错误模型是单向的,即j→i,实际上可能是双向的,即也有可能同时存在i→j,这比较复杂,因篇幅有限,本文不作进一步讨论。

0或1耦合错误模型定义如下:一个单元的向上或向下迁移,强制第二个单元的内容为0或1。如图3(b)所示,Sn是普通的置1输入,Sc是不想要的置1输入,它强制R/S触发器置1,即为<↑;1>。R/S的R端情况与S端的情况类似,即为<↑;0>。该模型有4个可能性:<↑;0>,<↑;1>,<↓;0>,<↓;0>。

这里给出一个i单元和j单元的一个0或1耦合错误模型状态转换的例子,见图4(a),共有4个状态:00、01、10、11,即Sij表示为S00、S01、S10、S11。W0/i,W0/j表示i单元置0,j单元置0,状态返回到S00状态;W1/i,W0/j表示i单元置1,j单元置0,状态返回到S10状态;W0/i,W1/j表示i单元置0,j单元置1,状态返回到S01状态;W1/i,W1/j,表示i单元置1,j单元置1,状态返回到S11状态。在该例图的其他状态在一定条件下的转换的分析,可按照上述方法进行。这里需要特别指出的是S00在W1/j条件下转换到S11的情况。正常情况下,S00在W1/j条件下应该转换到S01状态,而不是S11状态,这说明发生了0或1耦合错误。即当j从0迁移到1(↑)时,i强制为1,即为<↑;1>。

与上述迁移引起的耦合错误模型不同的是桥接耦合错误模型和状态耦合模型。这两种耦合是由于逻辑电平的原因造成的,与迁移无关。

1.5邻近单元感应错误模型

邻近单元感应错误模型定义为:一个单元的内容是由其所有另外的单元构成的图式所影响,这些单元构成的图式是由0和1所组成的。如图4(b)所示,邻近单元是指与错误单元有关的所有单元包含错误单元。b代表基本单元,基本单元表示正在测试的单元。称不包含基本单元的邻近单元为已消除基本单元的邻近单元,简称为已消基邻近单元。邻近单元感应错误模型的表示方法为:Ci,j<d0、d1、d2、d3:b>,其中Ci,j为基本单元的位置,d0、d1、d2、d3为已消基邻近单元。邻近单元感应错误模型有三种类型,分别为主动邻近单元感应错误模型、被动邻近单元感应错误模型以及静态邻近单元感应错误模型。主动邻近单元感应错误模型定义为:由于已消基邻近单元的变化,基本单元也改变了器内容。如Ci,j<0,↓,1,1:1>,由于d1的迁移,使得基本单元的状态变成1。被动邻近单元感应错误模型定义为:由于某种已消基邻近单元所构成的图式使得基本单元的内容不能被改变。如Ci,j<0,0,1,1:↑/0>,当从d0到d3为0011时,基本单元的状态0不能改变。静态邻近单元感应错误模型定义为:由于某种已消基邻近单元所构成的图式使得基本单元的内容被强制到某个状态,如Ci,j<0,1,0,0,1,1,1,1;-/0>,当d0到d7为01001111时,基本单元的内容被强制到0。

1.6地址译码错误模型

地址译码错误有5种类型:(1)某一个地址没有单元可访问;(2)没有某单元可访问的地址;(3)某个单元多个地址可被访问;(4)某个单元可被多个地址访问;(5)以上四种类型的任意组合。在VXI或PXI高密度Digital I/O板卡中的端口选择的电路逻辑就相当于地址译码模型。

2VXI或PXI高密度Digital I/O板卡的诊断算法

2.1诊断算法简介

诊断算法就是根据VXI或PXI高密度Digital I/O板卡的特点,结合上述错误模型,选取最能检测出相关错误模型的方法。每种具体型号的板卡的电路结构可能不同,但有些错误模型是普遍发生的,如卡死错误模型、迁移错误模型、耦合错误模型、地址译码错误模型。根据具体电路结构来决定是否需要邻近单元感应错误模型的检测算法。诊断算法有:行程算法、0-1算法、棋盘算法、步行和快步0/1算法等。

2.2行程算法的概念

行程算法是由一定数量的有限的行程单元序列所组成的。行程单元是对高密度Digital I/O的每个单元诊断操作的序列。行程方向可以按地址方向向上行进,用↑表示;行程方向可以按地址方向向下行进,用↓表示;地址无关用表示。置0为(w0),置1为(w1)。读期望值0为(r0),读期望值1为(r1)。行程测试算法{↑(r0,w1);↓(r1:w0)}是由行程单元{↑(r0,w1)}和{↓(r1:w0)}所组成的。行程算法的类型很多,功能很强,有针对各种错误模型的解决方法,但算法比较复杂,其能检测到故障但不一定能定位到故障。行程算法的主要类型为:MATS+:主要检测卡死错误模型;行程C-:检测无关联的0或1耦合错误模型;行程A:检测相关联的0或1耦合错误模型;行程B:检测相关联的迁移错误模型和迁移错误模型。

2.30-1算法

最小测试是由置0和置1所组成。算法分为4个步骤:(1)对所有单元置0;(2)对所有单元读;(3)对所有单元置1;(4)读所有单元。0-1算法特点为:(1)不是所有的地址译码错误能被检测到;(2)卡死错误可以被检测到和定位(条件是地址译码正确);(3)不是所有的迁移错误能被检测到;(4)不是所有的耦合错误能被检测到。其算法表示为:{↑(w0);↑(r0);↑(w1);↑(r1)},优点是算法占用时间短和能够定位。

2.4棋盘算法

棋盘算法把所有单元分成2组,即单元组1和单元组2,由此形成棋盘图式。其算法分为4个步骤:(1)对单元组1置1,对单元组2置0;(2)读所有单元;(3)对单元组1置0,对单元组2置1;(4)读所有单元。其算法表示为:

其中M1为单元组1,M2为单元组2。其特点为:(1)不是所有的地址译码错误能被检测到;(2)卡死错误可以被检测到和定位(条件是地址译码正确);(3)不是所有的迁移错误能被检测到;(4)不是所有的耦合错误能被检测到。该算法的优点是占用时间短和能够定位。该算法主要针对邻近单元的短路检测(条件是地址译码正确)。

其中M1为单元组1,M2为单元组2。其特点为:(1)不是所有的地址译码错误能被检测到;(2)卡死错误可以被检测到和定位(条件是地址译码正确);(3)不是所有的迁移错误能被检测到;(4)不是所有的耦合错误能被检测到。该算法的优点是占用时间短和能够定位。该算法主要针对邻近单元的短路检测(条件是地址译码正确)。

2.5步行和快步0/1算法

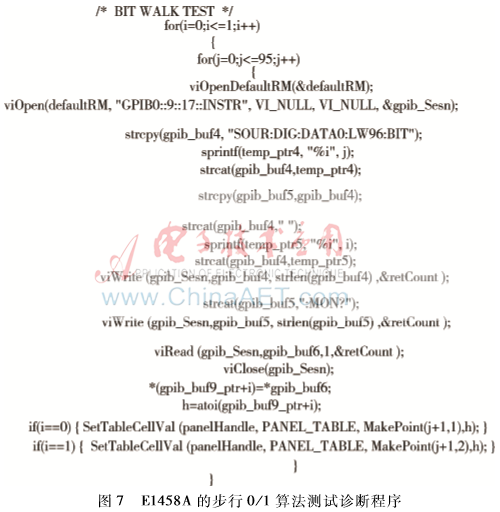

步行和快步0/1算法是相似的,只是读基本单元时的行为有些差异。步行算法是所有其他单元读过之后才读基本单元;快步0/1算法是每次读其他单元后,读基本单元。具体算法如图5所示。

步行和快步0/1算法的特点是:(1)能检测和定位所有的地址译码错误。地址译码错误将造成基单元不能在步骤2进行置位,算法从而在步骤5或7能够定位故障。同样,其他的单元在步骤2置位,在步骤4和步骤6定位故障。(2)能检测和定位所有的卡死错误,因为在基本单元在步骤2置位,在步骤5和7进行读(0和1)检测和定位。(3)能检测和定位所有的迁移错误。因为在步骤5和步骤7的读操作后,基本单元在步骤2有一次↑和↓的迁移动作。(4)能检测和定位所有的耦合错误。在步骤2,可以探测<↑;1>、<↓;0>、<↑;↑>、<↓;↓>耦合错误(根据步骤1中的0或1),在步骤4和6进行定位故障。在步骤3,可以探测<↓;1>、<↑;0>、<↓;↑>、<↑;↓>耦合错误,在步骤4和6进行定位故障。该算法的定位地址译码错误和耦合错误是十分精确的。因为在置位耦合单元后,算法立即进行读操作,所以它十分清楚哪个单元耦合给哪一个。步行和快步0/1算法在实际工程中得到了广泛应用。

3VXI或PXI高密度Digital I/O板卡的诊断算法应用举例

在AlcatelLucnt公司的3G CDMA测试平台中使用了4块Agilent VXI Chanel Digital I/O E1458A,快速和精确定位故障是选择诊断算法的基本要求。综合各种算法特点,根据2.5节的描述,步行0/1算法是比较适合本例。本例用NI LabWindows CVI[5]软件开发了E1458A的测试诊断程序,测试程序界面见图6,其涉及步行0/1算法的部分代码(由于篇幅有限,只用部分代码做演示)见图7。如图6所示,SELF BIT BY TEST REVIEW表格(位于界面的下半部分)用来显示采用了步行0/1算法的诊断结果。表格的第1行是通道号(Channel),第2行是测试置0的结果,第3行是测试置1的结果。如果测试结果在第2行(置0行)的某格显示出1或-1,则表示该格所对应的通道置0出错;如果测量结果在第3行(置1行)的某格显示出0或-1,则表示该格所对应的通道置1出错,这样可以即精确又方便地报告故障所在的位置,即哪一端口的哪一线出错及出错的类型。

4结论

通过对VXI PXI高密度Digital I/O建立抽象模型,引入了对其错误模型和算法的研究和讨论,从而得出了合适的算法即步行0/1算法,并应用此算法成功地开发了VXI PXI高密度Digital I/O自动化诊断系统,解决了大规模生产的实际维护问题。当然,可以应用此思路,改进或发展这些算法并应用到其他类似模型的电路结构中,从而能更好、更多地解决实际问题,开发更多的自动化诊断系统。

参考文献

[1] CHAKRAVARTY S, Gong Yiming. An algorithm for diagnosing two line bridging faults in combinational circuits[C]. 30th Conferecne on Design Automation, 1993:520-524.

[2] JHA N, GUPTA S.数字系统测试[M].王新安,蒋安平,宋春殚,等,译.北京:电子工业出版社,2007.

[3] BOPPANA V, FUJITA M. Modeling the unknown! Towards model independent fault and error diagnosis[C]. IEEE International Test Conference,1998:1094-1011.

[4] 秦莲童.高校微机室计算机I/O设备故障分析与修复[J].微型机与应用,2015,34(5):47-50.

[5] 王建新,杨世凤.LabWindwos/CVI测试技术及工程应用[M].北京:化学工业出版社,2006.