文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.10.011

中文引用格式: 杜微,李荣宽. 一种分步式Dual slope ADC的研究与设计[J].电子技术应用,2015,41(10):45-48.

英文引用格式: Du Wei,Li Rongkuan. Design of a new subranged dual slope A/D converter [J].Application of Electronic Technique,2015,41(10):45-48.

0 引言

温度、压力等缓慢变化的信号一般频率很低(几赫兹甚至更低),当传感器在感受这些缓慢变化的信号之后,需要通过一个转换速率可以很低但必须很精准的模数转换器将未知的模拟信号转换为已知的数字信号[1]。双积分 ADC 应用非常广泛。传统的结构主要由1个带有输入切换开关的模拟积分器1个比较器和1个计数单元构成,通过两次积分将输入的模拟电压转换成与其平均值成正比的时间间隔。与此同时,在此时间间隔内利用计数器对时钟脉冲进行计数,从而实现模数转换。积分型 ADC 两次积分的时间都是利用同一个时钟发生器和计数器来确定,因此所得到的表达式与时钟频率无关,其转换精度只取决于参考电压[2]。此外,由于输入端采用了积分器,所以对交流噪声的干扰有很强的抑制能力:能够抑制高频噪声和固定的低频干扰(如50 Hz或60 Hz),适合在嘈杂的工业环境中使用[3]。这类ADC 分辨率高,传统结构可达到22位,还具有功耗低、成本低等特点。大量应用于低速、精密测量等领域,如现有工业、民用仪器仪表中。

1 基本原理

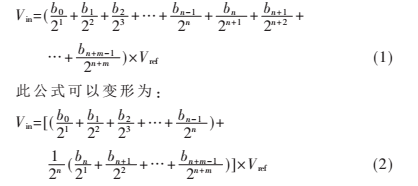

此新型Dual slope ADC的实质是基于分步式ADC的转换原理,一个基本的m+n位的奈奎斯特ADC的转换过程可以用数学公式表示为:

由式(2)可以看出此m+n位ADC的转换公式可以拆分成两个A/D转换公式,一个n位ADC的转换公式为:

其中的Vin是系统输入的未知模拟电压,Vref是给定的参考电压。另一个m位子ADC的转换公式为:

其中,Vin1为未知的输入信号,而此m位ADC的参考电压为:

至此,从理论推导的角度证明了这种分步式ADC结构的合理性。

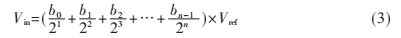

此分步式ADC先进行n位ADC的转换,将转换完成后的剩余电压作为m位子ADC的未知输入信号。整个过程等效实现了m+n位ADC的转换。但前n位ADC转换的剩余电压比较小,比较器可能无法分辨[3]。为了解决了这个问题,本系统中引入了自动补偿电路,如图1所示,通过开关控制积分器电阻和电容的比值,从而改变积分的时间常数。使得比较器的输入信号幅度不会被衰减。

此自动补偿方法不会影响分步式Dual slope ADC转换的精准性,系统中带补偿的积分电路如图1所示,正反向积分转换过程如图2所示。正向积分时系统的输入为未知的模拟信号Vin,而反向积分时系统的输入为参考电压Vref。

由虚短路、虚断路原则可以得到:

![3O[]VIIZZFRGH`JU1YA0~}H.png 3O[]VIIZZFRGH`JU1YA0~}H.png](http://files.chinaaet.com/images/2017/01/12/6361981439148053854172852.png)

式中的Vcm为运算放大器的共模电压,此系统中为2.5 V。Req、Ceq为补偿后的等效电阻和电容,这两个值由开关控制,可以得出输出电压为:

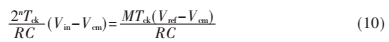

由图2可知,在T1=2nTck时积分器的输出电压为:

![16]@6T7{{OPR~QTOHCTDVLW.png 16]@6T7{{OPR~QTOHCTDVLW.png](http://files.chinaaet.com/images/2017/01/12/6361981457783053851864909.png)

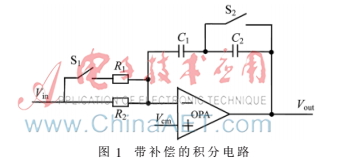

反积分过程接入的电压为Vref,从T1时刻积分到T1+T2时刻的输出电压为:

当Vo2=0时比较器刚好翻转,此时由式(8)、式(9)可以得到转换关系式:

其中的MTck=T2为反积分的时间,输入的未知模拟电压为:

![E9_AQ$~Y~`K@]7U(4JUMYM9.png E9_AQ$~Y~`K@]7U(4JUMYM9.png](http://files.chinaaet.com/images/2017/01/12/6361981641933953859774930.png)

由式(10)、式(11)的表达式可以看出最终的所求电压Vin与积分时间常数RC没有关系,只要保证正反向积分的时间常数相同,那么此Dual slope ADC的转换精度就不会受到影响[4]。而此系统中的补偿方法满足稳定条件,所以这种补偿方法是可行的。

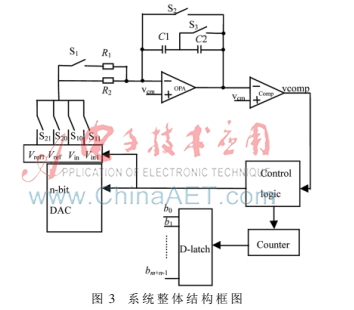

2 系统结构

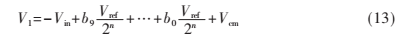

基于以上原理,文中所设计的分步式Dual slope A/D转换器由补偿积分器、比较器、D/A转换器(DAC)、数字控制逻辑等几部分组成,如图3所示。Vref为n位ADC的输入参考电压,Vin1是n位ADC转换完成后的剩余电压(也是m位ADC的未知输入电压),Vref1为m位ADC参考电压。其中Vin1、Vref1可以通过数字逻辑控制n位DAC模块而获得。

整个m+n位ADC的转换分为两个过程,当S10、S20闭合,S1、S2、S3、S11、S21断开时为n位ADC的转换过程,此时未知输入信号Vin及参考电压Vref通过开关S10、S20接入电路,此过程与传统的双积分ADC的工作过程相同。转换完成后,通过锁存器将得到的n位ADC的转换结果存储起来。当开关S10、S20、S2断开,S11、S21、S1、S3闭合时为m位ADC的转换过程,此时未知输入信号Vin1及参考电压Vref1通过开关S11、S21接入电路。进行m位ADC的转换过程。整个过程实现了m+n位ADC的转换。

此结构相对于传统的双积分ADC的创新之处有:

(1)通过开关S10、S20、S11、S21控制实现两步转换的过程。

(2)通过开关S1、S3实现了自动补偿的功能,保证了m位子ADC转换的精准性。

(3)通过增加一个DAC电路将n位ADC转换的剩余电压提取出来,进行m位子ADC的转换,从而具备了再分辨的能力。

3 电路设计

系统中的DAC结构如图4所示,其中C是单位电容,最右端的电容为终端匹配电容。第一个时钟周期为放电过程,此时k1、k2为高电平,d1、b1~b10全部为低电平。第二个时钟周期为采样过程,此时k1、k2、d1、b1~b10全部为高电平。紧接着的十个时钟周期是转换过程,此时k1、d1是低电平,b1~b10受数字控制逻辑控制[5]。其余的时钟周期为n位ADC转换的剩余电压提取过程,此时k1为高电平,k2、b1~b10全部为低电平。

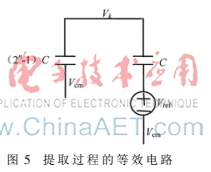

由DAC的转换过程,可以得到简化的等效电路如图5所示,从此等效电路可以容易地提取出所需要的电压Vin1、Vref1。

由基本的电容串联分压理论求得:

DAC电容阵列的上下极板的电荷守恒可以得到:

而电压Vk正好就是参考电压Vref1,电压V1就是Vin1。

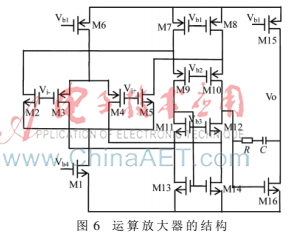

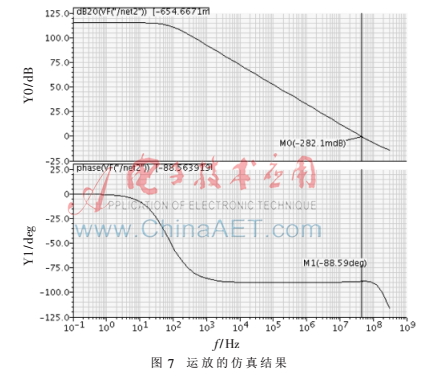

系统中的运放采用折叠共源共栅结构,为了增大输入共模范围而采用轨到轨运放的结构[6],具体实现电路如图6所示。在0.5 m工艺下,对此运放进行仿真,其增益和相位曲线如图7所示,由图可知运放的增益达到118 dB,相位裕度大于80°,单位增益带宽达到100 MHz。

4 系统仿真结果

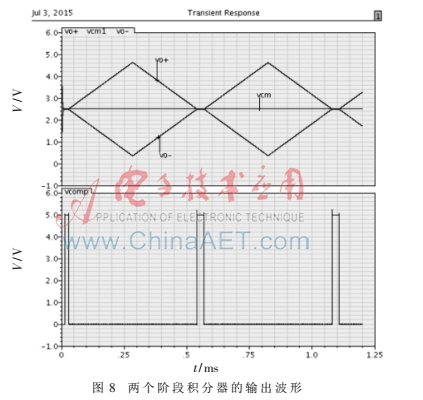

用Cadence软件对搭建的系统进行瞬态仿真,整个过程积分器的输出波形如图8所示,电压Vo+表示16位ADC的输出。可以看到由于采用了自动补偿电路,使得整个ADC的积分器输出幅度不会衰减。

在系统时钟频率为1 MHz,输入信号频率为0.5 kHz时,16位(m=n=8)ADC的系统转换结果如图9所示,当输入电压为3.0 V时,n位ADC的转换结果约为2.992 2 V,而m+n位ADC的转换结果约为2.999 92 V。有效位数大约为15位,其中的误差主要来自于数字控制逻辑,若继续对控制逻辑进行优化,分步式Dual slope ADC结构可以很容易达到很高的精度,同时速度也会得到提高。

相对于传统的双积分ADC,此分步式Dual slope ADC结构具有以下优点:

(1)此系统具有自动补偿功能,可以自动调节电压幅度,从而达到更高的分辨率。而且减小了传统双积分ADC对大电容的依赖性。

(2)此系统的两个过程通过复用的方式实现,从而使得芯片的功耗不会明显增大。

(3)此结构采用了分段结构,会将传统的双积分ADC的转换时间提高很多,传统结构最慢的转换需要22n个时钟周期,而此结构只需要2n个时钟周期。

5 结论

此新型Dual slope ADC系统采用了分步式工作方式,不仅会使其分辨率较传统的双积分ADC得以提高,而且转换速率也会大幅度提升;同时还引入了自动补偿方法,从根本上改善了传统的双积分ADC需要大的分布电容的缺点。值得一提的是:此系统由于采用了复用技术,所以将会和传统的双积分ADC一样具有低功耗的优势。此系统的缺点是数字控制逻辑比传统方法更复杂,且占据的芯片面积要有所增加,所以如何找到一种简洁有效的控制方法至关重要。此系统结构将更加适合于在低速、精密测量等领域应用。

参考文献

[1] RAZAVI B.模拟CMOS集成电路设计[M].陈贵灿,等,译.西安:西安交通大学出版社,2001.

[2] ALLEN P E,HOLBERG D R.CMOS analog circuit design[M].Second edition.Oxford University.Inc,ISBN 0-19-511644-5,2002.

[3] JOHNS D A,MARTIN K.Analog integrated circuit design[M].New York:iley,1997.

[4] BAKER R J.CMOS circuit design,layout and simulation[M].3rd Edition,John Wiley & Sons,2010.

[5] 罗刚.基于双积分原理的ADC设计[D],成都:电子科技大学,2009.

[6] 赵天挺.一种CMOS 12-bit 125ksps全差分SAR ADC[D].天津:南开大学,2004.