射频IC设计简述

2020-12-09

来源:EETOP

射频IC设计注意事项

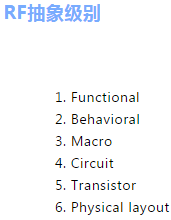

射频IC(RF IC)设计与模拟IC设计的特殊领域非常相似,通常是一种定制的过程,而该过程通常由一个或许多EDA工具来辅助设计。射频 IC设计的精确性质之一是寄生特性和封装特性对射频电路的性能有一阶影响。因此,射频IC设计通常是一个迭代过程,涉及整个IC设计过程中广泛使用的EM仿真、寄生建模和封装建模。

系统预算参数

射频IC设计还以 “系统预算 ”的形式对关键参数,如噪声图、功率、相位噪声、谐波、线性等给出性能要求和约束。这种预算由系统级设计团队确定,并将预算约束和性能要求传递给负责系统图中每个模块的射频设计人员。这些拓扑和电路经历了一个迭代的设计、仿真、优化和布局仿真过程,并使用能够处理IC的电磁仿真工具进行布局仿真。

设计约束

由于某些片上无源器件(例如电感器和电容器)受到代工厂的严重限制,RF IC设计人员通常对这些组件的尺寸和数值往往控制有限。这导致了设计中更大的不确定性,并且可能需要与代工厂进行反复的过程来设计和测试新组件,以生产出最能满足RF电路需求的组件。

在某些情况下,射频设计人员可能需要对邦定线和其他与代工厂无关的封装动态进行额外建模,以准确预测寄生和终端组装中的最终器件性能。许多RFIC都是以裸片的形式交付,并直接将其邦定到组件或托盘中,而不是典型的IC封装和PCB贴装。

电磁仿真

一旦RF IC进入物理布局阶段,通常会进行EM仿真,电路仿真和寄生提取的多次迭代,至少涉及IC封装,但也可能考虑到器件的PCB和外部电路。原因是射频电路与高度敏感的模拟电路非常相似,由于周边的外部电路、电场/磁场、温度、电磁信号和其他环境因素,性能可能会发生巨大变化。

即使在进行流片测试之后,在提交最终设计和开始生产RFIC之前,往往还需要进行测试、模型增强和额外的优化。