台积电分享碳纳米管的最新进展

2020-12-23

来源:半导体行业观察

硅基器件已经成为我们行业60多年的基础,这非常令人惊讶,因为最初的锗基器件将难以大规模集成。(值得一提,GaAs器件还开发了一个独特的微电子市场领域。)

最近,令人惊讶的是,通过引入诸如FinFETs之类的拓扑结构以及即将到来的纳米片,硅场效应器件获得了新的生命。硅基互补FET的研究正在进行中 (CFET)设计达到量产状态,其中nMOS和pMOS器件是垂直制造的,从而消除了当前单元设计中的横向n-p间距。

另外,材料工程学的进步已经将(拉伸和压缩)应力纳入硅通道晶体结构中,以增强自由载流子迁移率。

但是,硅设备收益递减的点正在逼近:

由于高电场下的速度饱和,无硅载流子迁移率接近最大值

尺寸的持续缩小降低了硅半导体的导带和价带边缘的“自由载流子态密度”(DoS)–填充更大范围的载流子态需要更多的能量

与Fin图案相关的统计过程变化很大

散热片的热传导导致局部“自热”温度升高,从而影响了几种可靠性机制(HCI,电迁移)

为解决以上问题,目前业界正在进行大量研究,以评估与硅完全不同的场效应晶体管材料的潜力,但这也与当前的大批量制造操作相一致。一种选择是探索 器件通道的单层二维半导体材料,例如二硫化钼(MoS2)。

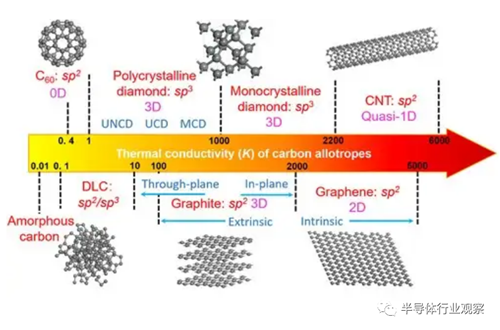

另一个有希望的选择是从碳纳米管(CNT)构造设备沟道。下图提供了碳键独特性质的简单图示。(我对化学反应有些不熟悉,但我记得“ sp2”键是指原子核周围亚轨道“ p壳”中相邻碳原子的电子配对。没有“悬挂键”,并且碳材料是惰性的。)

请注意,石墨,石墨烯和CNT的化学结构相似-使用石墨进行的实验材料分析更加容易,并且最终可以扩展到CNT处理。

在最近的IEDM会议上,台积电提供了有关CNT器件制造进展的有趣更新。本文总结了该演讲的重点。

CNT设备具有一些引人注目的功能:

极高的载流子迁移率(>3,000cm2在/V-sec,“弹道运输”(ballistic transport),散射最小)

非常薄的CNT主体尺寸(例如,直径~1nm)

低寄生电容

优良的导热性

低温(<400C)处理

最后一个功能特别有趣,因为它还为基于硅的高温制造与后续的CNT处理集成提供了潜力。

门介电(Gate Dielectric)

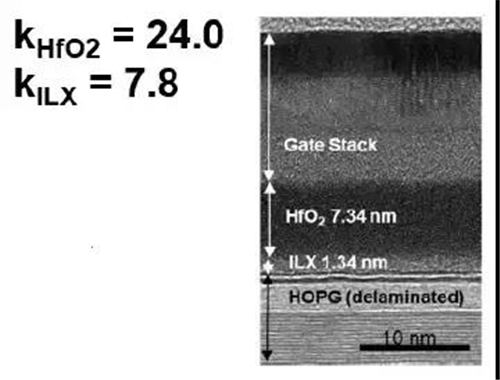

台积电开发了独特的工艺流程来为CNT器件提供“高K”电介质等效栅极氧化物,类似于当前硅FET的HKMG处理。

上面的TEM图说明了CNT的横截面。为了与独特的碳表面兼容,需要沉积初始界面电介质(Al2O3)–即需要在碳上对该薄层进行适当的成核和整合。

随后,添加高K HfO2膜的原子级沉积(ALD)。(如前所述,这些关于材料性能的介电实验是在石墨基底上完成的。)

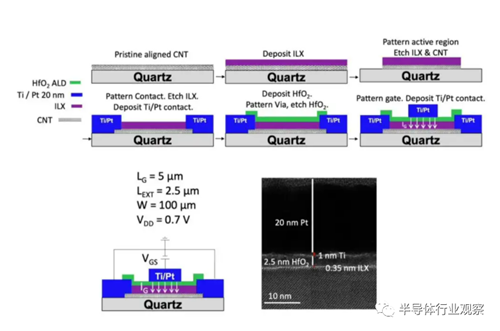

这些栅极电介质层的最小厚度受到非常低的栅极泄漏电流(例如,栅极长度为10nm的<1 pA/CNT)的限制。下面说明用于测量栅极到CNT泄漏电流的测试结构。(对于这些电测量,CNT结构使用石英衬底。)

实验得出的“最佳”尺寸为t_Al2O3=0.35nm和t_HfO2=2.5nm。由于这些极薄的层,Cgate_ox非常高,从而改善了静电控制。(请注意,这些层厚于CNT的直径,其影响将在稍后讨论。)

门方向(Gate Orientation)

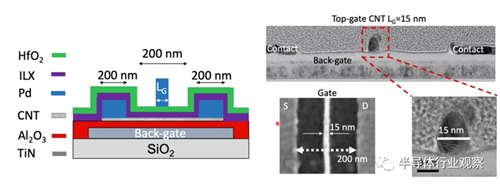

台积电评估的CNT器件采用了独特的“顶栅加背栅”拓扑。

顶栅提供常规的半导体场效应器件输入,而(较大的)背栅提供对S/D扩展区域中载流子的静电控制,以有效降低寄生电阻Rs和Rd。而且,背栅会影响CNT与钯金属之间的源极和漏极接触电势,从而降低肖特基二极管势垒以及在该半导体-金属界面处的相关电流行为。

设备电流

CNT pFET的IV曲线(线性和对数Ids(用于亚阈值斜率测量))如下所示。对于此实验,Lg=100nm,S/D间距为200nm,CNT直径=1nm,t_Al2O3= 1.25nm,t_HfO2=2.5nm。

对于此测试(制造在石英基板上),单个CNT支持超过10uA的Ids。接近上述目标尺寸的更薄电介质将实现进一步的改进。

最终将在生产制造中使用平行CNT-相关的制造指标将是“每微米CNT的数量”。例如,4nm的CNT间距将被引用为“ 250CNTs/um”。

挑战

规划CNT生产时肯定要解决一些挑战(仅举几例):

规则/均匀的CNT沉积,具有非常干净的表面,用于介电成核

需要最小化栅极电介质堆栈中的载流子“陷阱密度”

最佳S / D接触电位材料工程

设备建模设计

上面的最后一个挑战尤其值得注意,因为当前用于场效应晶体管的紧凑型器件模型肯定不够用。CNT栅氧化层拓扑与平面或FinFET硅通道完全不同。由于栅极到沟道的电场本质上是径向的,因此与平面器件一样,“有效栅极氧化物”并不存在简单的关系。

此外,S/D扩展需要唯一的Rs和Rd模型。而且,CNT栅氧化层的厚度比CNT的直径厚,从而导致从栅到S/D延伸以及到(小间距分隔)平行CNT的大量边缘场。为基于CNT的设计开发合适的紧凑模型是一项持续的工作。

顺便说一句,CNT“环绕栅极”氧化物(类似于纳米片周围的所有栅极)将比沉积的顶部栅极氧化物有所改进,但难以制造。

台积电显然正在投入大量研发资源,为“不可避免的”后硅器件技术的引入做准备。CNT的制造和电学表征结果证明了该器件替代产品的巨大潜力。