台积电展示全新的SRAM方案,可用于存内计算

2021-03-16

来源:半导体行业观察

纵观全球,研究人员在内存计算(in-memory computing)架构上的研究非常活跃。在最近的国际固态电路会议(ISSCC 2021)上,针对新颖的存储器阵列技术的多个技术会议专门用于支持机器学习算法的计算需求。

众所周知,现在将数据和权重值从内存移动到处理单元,然后再将中间结果存储回内存的做法效率低下。因为信息传输过程中不仅增加了计算延迟,而且相关的功耗是一个主要问题。

如下所示,“无增值”的数据移动消耗了大部分的能耗,这个比例甚至可能大于“增值”计算的能量消耗。请注意,实际的计算能耗是与数据和权重传递到计算单元相关的一小部分。

而存内计算的目标是减少这些低效率,这对于在边缘实施机器学习推理系统尤其重要。

机器学习应用中的存内计算的主要重点是优化与每个神经网络节点关联的向量乘法累加(MAC)操作。下图说明了(训练的)网络的计算——每个数据输入乘以权重值的乘积,然后提供给偏差和激活函数。

对于一般网络,数据和权重通常是多位数。权重向量(对于经过训练的边缘AI网络)可以使用有符号,无符号或二进制补码整数位表示形式。

对于存内计算,最终的MAC输出是通过添加部分乘法乘积来实现的。节点中每个(数据*权重)弧(arc)的位宽是定义明确的-例如,2n位向量覆盖2 n位无符号整数的乘积。但是,将所有弧的(数据*权重)乘积累加到高度连接的网络中可能需要更多的位才能准确表示MAC结果。

存内计算研究的重点领域之一是使用电阻RAM(ReRAM)位单元实现位线电流检测测量。数据输入(作为活动存储器行字线)和存储在ReRAM单元中的权重值的乘积会产生可区分的位线电流,该电流用于为参考电容充电。后续的模数转换器(ADC)将该电容器电压转换为等效的二进制值,以进行后续的MAC移位累加。尽管(数据*权重)产品基于ReRAM的实现具有区域效率,但它也有其缺点:

由于电压范围,噪声和PVT的变化,模拟位线电流检测和ADC的精度受到限制

ReRAM阵列的写入周期时间长

ReRAM阵列的耐用性严重限制了其作为通用内存存储阵列的适用性

这些问题都得出相同的结论。对于一个相对较小的推理神经网络,其中所有权重都可以加载到内存阵列中,并且数据矢量表示受到限制(例如8位或更少),基于ReRAM的实现将带来部门优势。

但是,对于需要网络大于阵列中存储的网络和/或需要重新配置的工作量的机器学习应用,更新权重值通常会阻止使用ReRAM当前检测方法。在数据精度要求很高的情况下,同样的问题也适用,因此需要更大的输入向量。

存内计算体系结构的替代方法是利用增强的SRAM阵列来支持(数据*权重)计算,而不是采用新颖的存储技术。这允许支持更丰富的机器学习网络集。

如果层数很大,则可以将输入值和权重值加载到SRAM阵列中以进行节点计算,保存输出值以及检索后续的层值。与通用计算解决方案相比,减少了与数据和权重传递相关的能耗,并且消除了ReRAM耐久性的问题。

使用扩展SRAM设计的存内计算

在最近的ISSCC上,台积电的研究人员提出了一种基于数字改良的SRAM设计存内计算方案,能支持更大的神经网络。

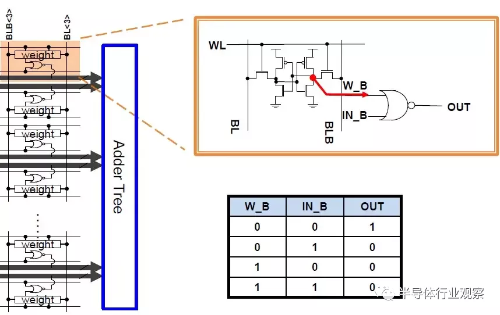

上图显示了台积电用于其测试的扩展SRAM阵列配置——阵列的一部分被圈出。每个切片具有256个数据输入,它们连接到“ X”逻辑(稍后将对此逻辑进行更多介绍)。数据输入向量的连续位在连续的时钟周期中提供给“ X”门。每个切片存储256个4位权重段,每个数据输入一个权重半字节。这些权重位使用常规的SRAM单元,因为它们可能会经常更新。存储在每个权重位中的值连接到“ X”逻辑的另一个输入。

下图说明了如何将此逻辑集成到SRAM中。

其中,“ X”是2输入或非门,具有数据输入和权重位作为输入。(两个“一位”值的乘积由“与”门实现;通过使用反相信号值和DeMorgan定理,2输入“或非”门在面积和功率方面都具有效率。)在每个限幅之间,有一个加法器树和一个加法器树。集成了部分和累加器逻辑,如下所示。

请注意,上图中的加权位存储使用常规的SRAM拓扑-对于6T的位单元,加权位字线和位线照常连接。每个单元上的存储值都扇出到或非门的一个输入。

每个切片的输出表示每个权重向量的半字节的部分乘积和。扩展数组之外的其他逻辑提供了移位和相加计算,以实现更宽的权重值表示。例如,(有符号或无符号整数)16位权重将合并来自四个条带的累加器结果。

现场测试结果

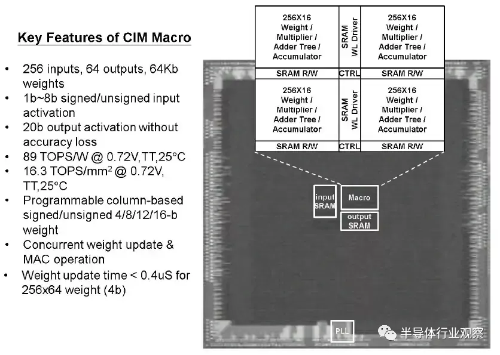

下方显示的是台积电基于全数字SRAM的测试工具的显微照片,突出显示了256输入,16切片(4位重量半字节)的宏设计。

请注意,基于SRAM的Compute-in-Memory宏的关键规范之一是可以在阵列中更新新权重的效率。

相对于电源电压的测量性能(TOPS)和功率效率(TOPS / W)如下所示。请注意,基于数字逻辑的MAC的使用可在很宽的电源电压范围内提供功能。

(从理论上讲,通常用于描述神经网络实现功率效率的TOPS / W品质因数可能是一种误导性度量–它在很大程度上取决于阵列中权重的“密度”和翻转率下图还有一张图,说明了此度量如何取决于输入切换率,假设权重向量中“ 1”值的比率为50%。)

尽管此内存计算测试站点是在较旧的22nm工艺中制造的,但将这种设计扩展到5nm节点时,TSMC研究人员提供了初步的面积和功率效率估算。

总结

研究人员目前正在进行大量研究活动,以支持用于机器学习的存内计算,以减少冯·诺依曼架构中数据传输的效率低下。研究的一个方面是寻求使用新的内存存储技术,例如ReRAM。但ReRAM的有限耐用性将这种方法的范围限制在权重值不会经常更新的应用中。位线电流检测的有限精度也限制了数据输入向量的宽度。

台积电(TSMC)展示了如何扩展常规SRAM阵列以支持大型和/或可重新配置网络的内存计算,并且需要频繁写入权重值。在SRAM行和列之间插入2输入或非门和加法器树逻辑提供了一种节省面积和功耗的方法。