芯片开发语言:Verilog在左,Chisel在右

2021-07-25

来源:半导体行业观察

老石按:在传统的数字芯片开发里,绝大多数设计者都会使用诸如Verilog、VHDL或者SystemVerilog的硬件描述语言(HDL)对电路的行为和功能进行建模。但是在香山处理器里,团队选择使用Chisel作为主要开发语言。这是基于怎样的考虑?

Chisel是基于Scala这个函数式语言来扩展出来的,我们可以把它看做是一个用来描述电路的领域专用语言,它和Verilog还是有很大区别的。

事实上,我们自己也做过两种语言的对比。在2016年,我们整个团队开始决定用RISC-V去实现标签化体系结构,也在那个时候开始接触Chisel。最早的时候我们重用了UC伯克利开发了的名叫Rocket的开源内核。这是个顺序执行的小核,我们在它上面加上了我们的标签机制,这期间其实就有很多的一些开发体会。

Rocket chip generator的系统架构图

前面提到我们的同学原来对Verilog很熟,但是用Chisel以后就会有一种爱不释手的感觉。有好多的通信,特别是年轻的同学,他们都愿意去尝试使用Chisel。有一个北大的研究生,他在做报告的时候讲,你用了Chisel以后就再也回不去了。

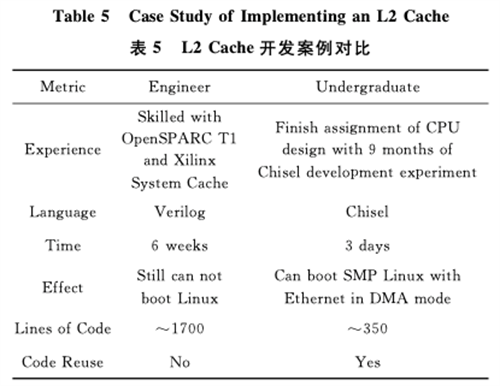

其实,我们自己还做过量化的评估。在2018年,我们团队里有两个本科生和一个工程师做过一个实验。这个实验是要开发一个L2 Cache,但是要集成到RISC-V的内核里。我们的工程师是用Verilog来开发的,他对Cache非常熟悉。他把OpenSPARC里面的Cache、还有Xilinx提供的Cache等等都研究过,代码都读得很透。所以他用Verilog开发,并且接到RISC-V里面去。当时他花了应该是6个星期开发,包括测试框架等等,一共写了5000多行代码。即便这样,后面还是有一些问题和Bug。

另外,我们当时有一位大四的本科生,现在也是香山的核心成员,他懂一些计算机体系结构,使用Chisel有9个月的时间。同样的任务,他用Chisel开发只花了三天时间就写出来了。把设计接到RISC-V核里面之后,还能够正常工作。之后又进一步就把DMA调通了,就能够支持像网卡这样的一些DMA的数据的传输。这个给我们留下了很深刻的印象。

表格来源:《芯片敏捷开发实践:标签化RISC-V》

我们觉得,本科生使用Chisel做的设计,哪怕是性能或者各方面差了一些,但他只用了三天时间。这样我们就可以快速去验证,并且实现我们的想法。

当然这个只是第一组实验。我们当时有一个群,在群里面吵的还是挺不可开交的,因为我们的工程师那个时候很不服气,他就觉得他的代码各方面都质量更高。所以我们后来又有另外一位中国科学院大学的大四本科生,他懂Verilog、但是没学过Chisel,所以他做的事情就是读我们工程师的Verilog代码,并把核心代码一行一行翻译成Chisel,最后要通过工程师写的测试。也就是说,翻译后的Chisel和Verilog实现的逻辑功能是完全一致的。

翻译完之后,再在同一个FPGA上面评估,看设计的PPA、 频率、功耗,还有使用的资源等等。这样下来的话,你就会看到其实出来的指标上面,大多数的指标实际都是Chisel还反而更好一些,代码量也会比他要小。

这还只是第一个阶段。后面我们的本科生又在博士生的指导下,把Chisel里面的高级特性给它加进去,结果一下子就完全超越Verilog的版本了,代码量大概只有Verilog的1/4~1/5,有些逻辑资源可以减少百分之六七十。所以那时候这组数据出来以后,工程师就他也觉得服气了。

表格来源:《芯片敏捷开发实践:标签化RISC-V》

Chisel vs 高层次综合

老石按:在FPGA里高层综合是一个非常热、非常流行的一个研究方向。但是我知道Chisel和高层次综合可能并不是一回事。在Chisel官网上也明确的指出:我不是高层次综合。但在我看来,它们背后的思维方式、或者是大的方向是有共同之处的,也就是让硬件开发更加的快速、更加敏捷。也就是像您刚才说的,从想法到实现,周期更加缩短。

但是从高层综合的角度来看,虽然学术界一直在讲高层次综合已经很多年的时间,它实际的商业化可能还是需要特别突破性的进展。现在业界的这些设计,比如大的网络设计、还有数据中心加速器的这些设计,仍然是基于SystemVerilog/Verilog/VHDL这样的RTL语言。这主要是因为高层次综合有这么几个问题:

第一个就是HLS可能并不能覆盖掉的全部应用领域,也就是说它可能适合于某些应用领域,但是对于这种吞吐量比较大的、或者高速数据包处理这些应用,它可能就不那么适合。

另外一个就是它的验证。因为它相当于在RTL顶上加了一层额外的高层次语言,等它综合或者处理完了以后,还是生成底层的RTL语言,然后再走原来的FPGA的这些开发流程。所以在验证过程中,增加额外的这层可能会给验证工作造成很大的问题。所以关于这两点您怎么看?

我想其实它的通用性方面是没有问题的。Chisel本身是一个硬件描述语言,所以从它的这种完备性来看的话,它跟Verilog是一样的。也就是说,Verilog能干什么事,Chisel也能干什么事,这两个是没有什么区别的,它只不过是另外一种语法表达而已。

调试是很多人都担心的一个问题。因为Chisel它现在其实是一个源到源的翻译,是首先是基于Scala这套语法去写一个硬件的描述。然后通过FIRRTL进行翻译。再往后走的话,其实是用Verilog那套流程去做,最后生成GDSII版图。

所以在这个过程当中,其实是明显的分成两个阶段了。前面一个阶段Chisel到Verilog,第二阶段就是Verilog到GDSII版图。

我们用Chisel已经流过三颗芯片,有大的芯片、有的小的芯片,有单核的有8核的。在早期的时候,我们其实也遇到过这样的一些问题。比如你用Chisel写的代码生成了Verilog,Verilog里面有一些变量,你那边在Chisel里面改一行代码,那它这个变量就全部重新改变。后来其实仔细分析以后,我们发现这些问题都是可以有一些办法来解决的,或者说它不是阻碍可调试性的最根本的问题。所以后面我们在做香山的时候,我们在这些方面已经处理得比较好了。

就像我们有同学,他自己开发了一个工具,可以把电路波形直接转变成一个上层的高级的事件。这个时候他其实就用了Chisel和FIRRTL里面的特性。

因为FIRRTL它有点像LLVM,它可以放很多的这样自己设计的模块,FIRRTL也可以定义自己需要的功能。这个在LLVM里叫pass,在FIRTEL里叫transformer。

有了这些工具,就可以让Chisel源码和下面波形建立起联系,让调试的过程甚至比原来用Verilog还要方便。

除了这个工具,同学们还自定义和扩展了一些printf,让我们在调的时候很多时候根本不用去看波形。这些都得益于Chisel的强大和开放。