拿什么抵抗美帝的新一轮芯片打压

2022-10-13

作者: CrazyBingo

来源: 疯狂的FPGA

这两天的新闻,相信芯片行业的小伙伴们都不陌生了。网络上也有了各种解读,有说美籍不能在华工作的,有说高端芯片工艺被清退的,也有说被制裁工作相关成员准备后路的,众说纷纭。

随之而来的是整个行业的恐慌,昨天芯片ETF直接暴跌7.2%,多家龙头吓的瑟瑟发抖,都担心身边的美籍华人专家要被迫回美国。

甚至今天都有应届生问猎头,高端芯片不能流片,那做高端芯片研发的意义何在?如下图所示:

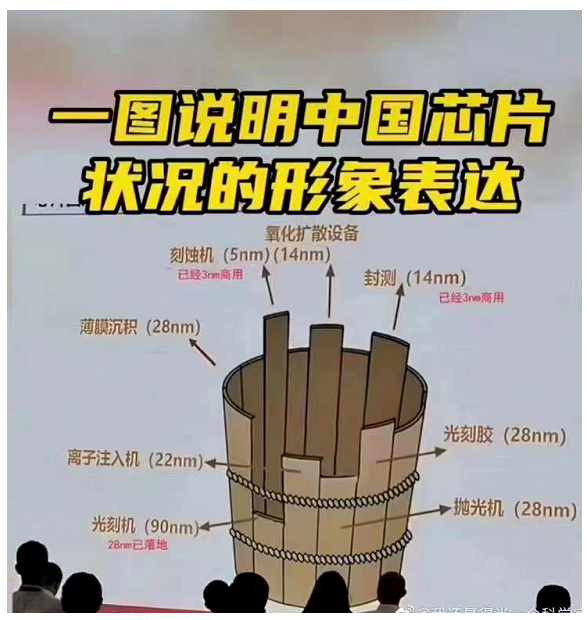

个人觉得,首先是落后要挨打,其次老大不想让老二成长,我们仍然需要卧薪尝胆,毕竟不管是半导体工艺,还是EDA都离老美相去甚远,此时不努力,更待何时。

网络时代,眼见未必为实,耳听未必为虚。这两天都是对于新的制裁法案的解读,甚至过度解读。我所探讨所得如下,也不知道对不对:

1)原先由台积电/三星把控30%美国技术实行流片限制,现在直接干到了>0%;

2)明确了16nm工艺、4800TOPS算力芯片的流片限制;

3)明确了美籍不得给大陆设计2)中的芯片,否则***

我之前写过一篇公众号:《如何才能半导体雪崩中活下来》,意思是当前我们过度膨胀,一定会一地鸡毛,雪崩一定会到来。那么,想要在雪崩中过下来,就必须练内功,等待机会,厚积薄发。

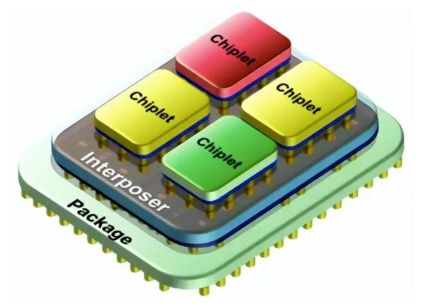

我们当然还要做高端工艺的设计,只是要卧薪尝胆的做;同时我们也得继续研究,如何在当前条件下突破限制,即面对16nm工艺,我们可以继续深度研究如何做好3D封装工艺,既然平面限制了,我们就从空间上下手。

面对4800TOPS算力的限制,那也正是时候进行Chiplet的研究与落地,采用多die的互联,去实现单die性能的限制。

3D封装工艺与Chiplet也可以探讨如何更好的耦合,从数量及空间上突破原先的限制,在当下为中国半导体的发展再争取一点时间。

相关的技术大家自可以行去脑补充,总之这两年国内新起的GPU DPU公司,也不是完全就没有出路,只不过原来我们通过面积去换取性能,现在只不过可能要通过空间去换取速度,难受是难受了点,但这改变不了我们前进的步伐。

芯片,是21世纪中美之间最大的斗争,也是我们绕不过去的坎,我们这一代人势必在没有硝烟的战争中坚持下去。

虽然国内芯片技术被打压,我反而还是认为当下是国产芯片百年一遇的机会。新的产品除了价格,大家都会评估选型,以及重点考虑全国产化的需求。国产芯片,尤其是国产传感器,国产FPGA除了忙于内卷,一定不要忘记功能与技术的演进,争取让国内的公司,多一个选择的权利,也让大家多一份安全感。