教程:基于FPGA图像处理的视频流实时处理系统

2022-10-24

来源:FPGA技术江湖

第一部分 设计概述

1.1 设计目的

本设计针对低照度高动态情况下,单帧图像曝光不足导致的图像噪声大、色彩失准等问题,在传统的 HDR 多帧融合(Frames Merging)方法上,采用层次化的图像配准(Image Alignment)方案、自适应白平衡(White Balance)与色调映射(Tone Mapping)策略,在降低图像噪声、真实还原景物色彩的基础上,极大 抑制了多帧融合时常见的运动伪影(MoTIon ArTIfact)现象。本设计采用 FPGA 进 行图像处理加速后,可以实现视频流的实时处理,视频流经过摄像头输入后,由 FPGA 进行处理并以较低的时延经 HDMI 信号输出。

1.2 应用领域

本设计可用于手持摄像系统(摄像机、智能手机)图像、视频流的 HDR 处 理,可用于低照度情况下固定监控系统的视频流 HDR 处理,可用于线上直播系统的视频流 HDR 处理。

1.3 主要技术特点

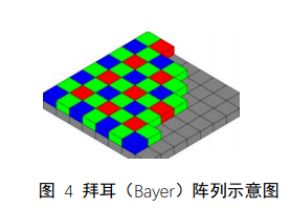

采用层次化的图像配准方案,对输入的拜尔格式(Bayer Mosaic)原始图像 进行处理,生成四层高斯图像金字塔(Gaussian Pyramids)。较高层次的图像配准结果将作为低层次配准的预偏移。这一过程极大优化了算法效率,其结构化的特 点为并行处理提供了便利。

采用有权重的图像融合方案,对输入的多帧图像,经图像配准后计算相应图像对(Image Pairs)的 L1 残差,得到各融合帧(Alternate Frame)相对参考帧 (Reference Frame)的权重,有效地降低了配准失误造成的运动伪影。

采用自适应白平衡及色调映射策略,在低光照情况下最大程度还原了景物的 色彩;在保证较高信噪比的情况下,提高了主要景物的亮度。

利用 FPGA 进行硬件加速,在 Pynq-z2 的 Python 开发环境中挂载封装有 IP 加速核的 Overlay,极大提高了运行速度,能够实时处理。

1.4 关键性能指标

相机感光度(ISO)、快门时间(Shutter TIme)、融合帧数;

图像融合处理时间、视频流处理延时;

图像信噪比、色彩还原度、细节清晰度、纹理清晰度(人眼观察)。

1.5 主要创新点

(1) 低照度高动态图像处理;

(2) 层次化的图像配准;

(3) 有权重的图像融合降噪;

(4) 自适应白平衡与色调映射策略;

(5) FPGA 硬件加速;

(6) 低时延视频流处理。

第二部分 系统组成及功能说明

2.1 整体介绍

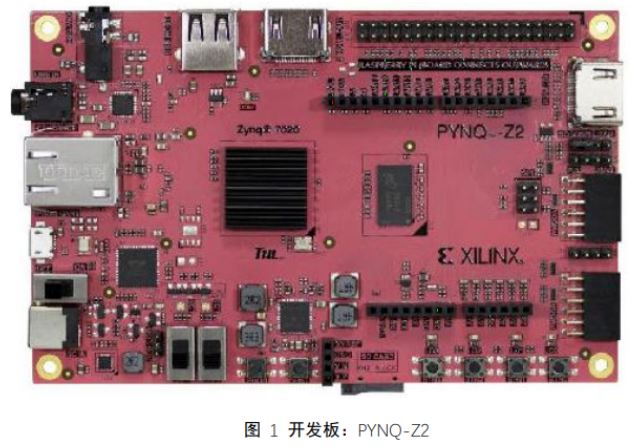

PYNQ-Z2 是基于 Xilinx ZYNQ-7000 FPGA 的平台,除继承了传统 ZYNQ 平 台的强大处理性能外,还兼容 Arduino 接口与标准树莓派接口,这使得 PYNQZ2 的具有极大的可拓展性与开源性。PYNQ 是一个新的开源框架,使嵌入式编 程人员能够在无需设计可编程逻辑电路的情况下即可充分发挥 Xilinx Zynq All Programmable SoC(APSoC)的功能。与常规方式不同的是,通过 PYNQ-Z2,用户可以使用 Python 进行 APSoC 编程,并且代码可直接在 PYNQ-Z2 上进行开发 和测试。通过 PYNQ-Z2,可编程逻辑电路将作为硬件库导入并通过其 API 进行编程,其方式与导入和编程软件库基本相同。

Xilinx Zyng All Programmable device 是一种基于双核 ARM cortex - a9 处理 器(称为处理系统或 PS)的 SOC,集成了 FPGA fabric(称为可编程逻辑或 PL)。PS 子系统包括许多专用外设(内存控制器、USB、Uart、IIC、SPI 等),并可以扩展额外的硬件 IP,其封装在 PL 的 Overlay 中。Overlay(或 Hardware Libraries, 硬件库)是可编程/可配置的 FPGA 设计,能将用户设计的应用从 Zynq 的处理系 统(PS 端)扩展到可编程逻辑(PL 端)。Overlay 可用于加速软件程序,或为特定程序定制硬件平台。

本设计的硬件平台整体结构如上图所示。为了对低照度高动态下的多帧融合 图像处理系统进行硬件加速,我们利用 Vivado HLs 工具,自主设计了 DownSample、Alignment、Merge、raw2rgb 等 IP Cores,并通过 AXI 总线与处理器核(PS 端)及存储器接口相连。在 PYNQ-Z2 的设计流中,这些 IP 被封装成 Overlay 并构造 Python API 驱动,以供 PYNQ-Z2 中的 Python 开发环境(JupyterNotebook)调用。

我们调用了 PYNQ-Z2 自有的 HDMI Overlay 进行处理流程及结果的显示。此外,PYNQ-Z2 为我们提供了丰富的存储单元、外设模块与通信接口。这些存储单元被用来存储图像数据及各类处理中间结果,而各类外设模块及通信接口则 被用来进行系统调试与控制的过程监控。

图像处理系统的工作流程如上图所示。相机在低曝光的情况下拍摄多帧(比 如说,6 帧)图片,这些原始图片(RAW images)由相机 CCD 或 CMOS 图像传感器生成,其像素值以拜耳阵列的形式存储。我们首先将原始各输入帧进行一次系数 2 的均值下采样,两次系数 4 的高斯下采样,得到一个四层的高斯图像金字塔。基于这个高斯图像金字塔,我们进行层次化的图像配准。配准的结果将作为图像融合的参考,同时结合备选帧与参考帧的 L1 残差作为融合权重,进行图像 融合。融合后的图像进行去马赛克及伽马降噪,并进行自适应的白平衡及色调映 射等操作,将单通道的融合图像转为三通道(对应 RGB 色彩空间)输出图像, 最终输出与原始图像同分辨率的处理结果。

均值下采样与高斯下采样处理被封装在名为 DownSample 的 IP core 中,层次化图像配准处理被封装在名为 Alignment 的 IP core 中,图像融合处理被封装在名为 Merge 的 IP core 中,去马赛克、白平衡、色调映射等处理被封装在名为 raw2rgb 的 IP core 中。这些 IP cores 挂载到 AXI 总线上,经封装为 Overlay 提供 Python API 给 PYNQ-Z2 的 Jupyter-Notebook。

2.2 各模块介绍

下采样模块(DownSample)

下采样模块为后续的层次化图像配准处理提供四层高斯图像金字塔。四层高斯金字塔的最底层为全分辨率的拜耳原始图像(我们称该层为 layer_raw),其像素点以拜耳阵列的形式排布,如下图所示。

我们首先进行系数 2 的均值下采样,直观上将一个 2*2 像素的“方格”取均值下采样为一个像素。下采样后的结果类似于一个单通道的灰度图像,但实际上绿色通道对下采样后的结果影响较大。我们称该层为 layer_0。

layer_0 随后进行两次系数 4 的高斯下采样。卷积核函数见附录。该卷积核 函数的大小为 5*5 像素,以 4 像素为步长在被采样的图像上以后,对该图像进行下采样。高斯下采样的结果将在一定程度上保留了采样前图像的低频信息,而图 像细节则被丢失。直观上图像的大致轮廓被保留,图像尺寸更小,细节模糊不清。两次高斯下采样的结果分为称之为 layer_1 与 layer_2。

经下采样模块处理后的结果可以用下图说明。

图像配准模块(Alignment)

图像配准以图像对(Image Pairs)的形式,在融合备选帧(Alternate Frame) 与参考帧(Reference Frame)之间展开。对参考帧中的每一个 16*16 像素的图块 (TIle),寻找其在融合备选帧中使两者 L1 残差最小图块,两个图块位置上的偏 移即为配准结果。其 L1 残差的计算方式可用下式表达。

式中的求和对一个图块内的所有像素进行,配准的目的是对参考帧中的每一个图 块,寻找其在每一个备选帧中的对应图块,使得上式的结果最小。此时两个图块 的坐标偏移量即为配准结果。

在保证图像间偏差不大的前提下,图块配准的搜索范围可以限定图块原始位 置周围的若干像素内。为了进一步提高配准的效率,我们采用层次化的配准方案:在上层低分辨率图像中进行预配准,配准结果将作为下层图像配准的预偏移 (Previous Offset)。各层图像以图块为基本单位,在预偏移的基础上进行小范围的配准。由此,上述残差计算式可以重新表达如下。

更多信息可以来这里获取==>>电子技术应用-AET<<