台积电整合推出最先进CoPoS半导体封装

2025-08-18

来源:IT之家

8月16日消息,消息源 Digitime 昨日(8月15日)发布博文,报道称台积电持续推进先进封装技术,正式整合CoWoS与FOPLP,推出新一代“CoPoS”工艺。

首条CoPoS实验线将于2026年设立,量产预计落地嘉义AP7厂与美国亚利桑那州厂,最快2028年底至2029年上半年量产。

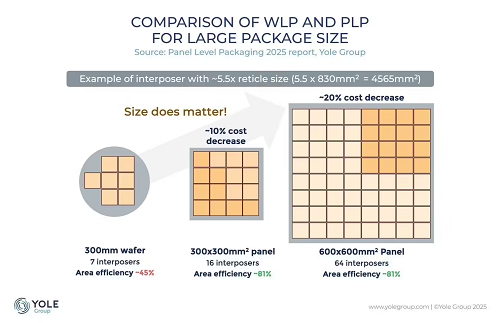

消息称CoPoS本质上是CoWoS的面板化升级,将芯片排列在大型方形基板上,取代传统圆形硅中介层,不仅能有效提升产能,还能大幅优化面积利用率与成本。

CoPoS技术针对AI大尺寸芯片的封装挑战,创新采用玻璃或蓝宝石方形载具作为中介层,并在其上镀制RDL(再分布层),支持更大光罩和更高集成度,有效缓解芯片尺寸扩大带来的翘曲(warpage)问题。

面板尺寸可达310x310mm、515x510mm甚至750x620mm,远超传统300mm圆形晶圆,为AI芯片扩产和降低单位成本提供了技术支撑。

据半导体供应链消息,台积电已规划于2026年在采钰(台积电子公司)设立首条CoPoS实验线,而嘉义AP7厂的P4、P5厂则将作为量产据点,最快2028年底至2029年上半年实现量产。此外,台积在美国亚利桑那州也同步规划两座先进封装厂,分别以SoIC与CoPoS为主。

随着相关设备规格与订单量确定,全球供应链企业纷纷加入竞标行列,首波供应链名单囊括KLA、TEL、Screen、Applied Materials、Disco等国际大厂,以及印能、辛耘、弘塑、均华、致茂、志圣等 13 家台厂。

简要介绍下不同封装工艺:

· CoWoS(Chip-on-Wafer-on-Substrate)是台积电主力封装技术,将芯片排列在圆形硅中介层,适用于高性能计算芯片

· FOPLP(Fan-Out Panel Level Packaging)是扇出型面板级封装技术,可在更大面板上进行芯片封装;

· CoPoS(Chip-on-Panel-on-Substrate)是台积电新一代先进封装技术,将芯片排列于方形面板基板,提升产能、降低成本,并解决大尺寸芯片封装难题。

· WMCM(Wafer-level Multi-Chip Module):台积电升级版 InFO-PoP 封装技术,专为苹果等高端客户开发。

· SoIC(System on Integrated Chips):台积电 3D 堆叠型封装技术,实现高密度集成与互联。