适合中国3G TD-SCDMA标准的数字前端解决方案

2008-04-17

作者:Tim James,David

时分同步码分多址(Time Division-Synchronous Code Division Multiple Access)是中国自主研发的第三代蜂窝通信标准,也是两个3GPP" title="3GPP">3GPP时分蜂窝标准之一(另一个是TD-CDMA)。TD-SCDMA" title="TD-SCDMA">TD-SCDMA与同类标准不同之处在于码片速率低,并且上行链路" title="链路">链路提供时间同步传输能力。中国目前在这一标准的研发方面已经进行了大量投资,到目前为止已经成功建设了多个测试和试验网络。一旦中国颁发3G牌照,相信TD-SCDMA网络会很快实现部署。

TD-SCDMA的突出系统特点

TD-SCDMA系统有两大突出特点:首先,考虑到其上行传输(手机到基站)的时间同步特点,被称为联合检测(joint-detection)的高级信号处理技巧在基站恢复每个用户的传输。在理想情况下,利用联合检测可以完全消除同一小区内来自其它用户的干扰,因此与其它异步匹配检测技术相比,可以提高系统容量。第二个突出特点是使用自适应波束成形(beam forming)来提高信噪比并减轻干扰。

利用赛灵思 FPGA 可以高效实现联合检测功能,但本文的重点基于FPGA的成本经济的TD-SCDMA数字前端(DFE)解决方案。波束成形需要在基站使用多个天线(通常为六至八个天线)。在下行链路,一个小区中的每个载波在经过适当的相位和幅度加权以及上转换以后,传输到对应的天线。在上行链路,每个天线接收到的信号需要下变频转换到基带。上变频和下变频功能分为模拟和数字两个部分。在数字部分,这些功能采用数字上变频器(Digital Up Conversion)和数字下变频器(Digital Down Conversion)完成,两者共同构成数字前端(DFE)。图1是一个基站模拟和数字前端的通用示意图。

对于每个小区使用六个天线和六个载波的情况,共需要 36个通道,通常这意味着需要大量专用标准产品(ASSP)芯片。无论是从功耗方面,还是从PCB面积方面,这都意味着昂贵的成本,更不用提还有可靠性问题。本文描述了一种基于FPGA的DFE解决方案。该方案使用了Multiple Access Communications (MAC)Limited公司为赛灵思公司开发的经过预先验证和优化的Xilinx? System Generator for DSP TD-SCDMA DFE IP库。MAC公司是一家咨询公司,位于英国南安普敦市 (Southampton)。

TD-SCDMA DFE解决方案

使用赛灵思芯片器件(FPGA)能够以极高的资源利用率实现一个符合采样速率和调节范围要求、同时包括DUC和DDC模块的数字前端(DFE)解决方案。基于Xilinx System Generator for DSP工具的DFE库支持针对不同天线和载波配置实现快速方便的重新配置、实现和验证,不需要重新设计或修改DUC和DDC链路上的基本模块,因此用户可以从容应对基站DFE设计的复杂性。

TD-SCDMA DFE库中包含了创建DUC和DDC链路所需要的所有System Generator IP块,包括滤波器、本地振荡器和混频模块以及不同的输入和输出格式模块。DFE库是参考设计包的一部分。该参考设计包还包括一个用于硬件协同仿真的18通道设计实例、用于实现3GPP兼容性测试的MatLab测试脚本以及一个运行在Nallatech V4 XtremeDSP套件上的全速演示解决方案。根据客户要求,赛灵思公司可向客户提供这一参考设计包(请参阅网址http://china.xilinx.com/esp/wireless/index.htm)。

图2和图3给出了利用TD-SCDMA DFE库中的IP模块实现的DUC和DDC信号路径细节。库中的基本模块是优化的六通道" title="六通道">六通道DUC和DDC模块,调谐范围均为9.6 MHz,中频(IF)采用速率为76.8 Msps,即TD-SCDMA 1.28 Mcps码片速率的60倍。基带数据以码片速率输入和输出。信号路径经过仔细设计,可实现最优的资源效率,并使用307.2 MHz系统时钟。这一高性能是充分发挥V4 SX FPGA中集成的DSP48功能的结果。

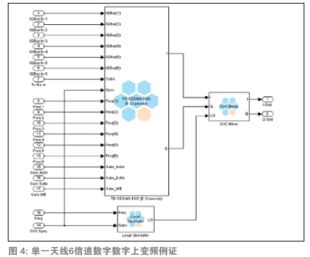

图4所示为使用DFE资料库模块构建的六通道DUC。信号处理的大多数操作都是在六通道“TD-SCDMA DUC”模块中完成的。添加“本地振荡器”和“DUC混频器”资料库模块是为了将DUC的复合输出从零转换成一个更为实用的中频。这一子系统生成是针对单天线" title="单天线">单天线输出的。只需简单地复制这一子系统,就可以支持多单元天线系统。

这样,支持任意数量的天线就变得相对简单了。那么,对于需要的载波器少于六个时,又该怎么设计呢?在这种情况下,如果使用“完整的”六载波器设计,尽管也不失为完全可行的解决方案,但会导致过大的FPGA设计。最坏的情况下,可能导致难以使用较小的器件,因而大大增加解决方案的成本。

如果解决方案要求用户手动删除任何不需要的逻辑,或涉及实现和提供一整套预定义的变量,这无疑与“让用户不必掌握设计的复杂细节”这一使用资料库的初衷背道而驰。相反,DFE库提供了一些精巧的附加逻辑,可帮助下游设计工具在构建时将未使用的逻辑优化掉。这样,用户只需要使用适当的库模块,并终止未使用的输入就可以了。三通道DUC设计的例子如图5所示。其中,利用“未使用的BB输入”模块将通道3到6阻断,同时这些通道的控制输入也被固定了恒定值。现在,尽管此设计使用的是六通道DUC子系统构造,但那些专为未使用通道预备的所有逻辑、Block RAM 和 DSP48 都会在构建时被删除。

DDC的情况与此类似。图6是六通道单天线设计的例子,而图7是其三通道的变型。对于DDC,使用标准的Simulink Terminator模块终止未使用的输出,并将未使用的控制端口固定为定值,就可以将未使用的通道优化掉。对于DUC,只需要简单地复制单天线设计,就可以支持多个天线。

前面假设9.6 MHz的调谐范围是足够的,对于需要大于9.6 MHz调谐范围的应用,可以通过级联两个同样DUC或DDC模块的方式扩展调谐范围,例如,调整到15 MHz的范围。

3GPP兼容性测试和性能验证

如上所述,TD-SCDMA DFE库模块组中的IP模块设计满足TS25.105中的3GPP要求。因此,可以确保对于任何基于该IP库的系统都可以满足相关的3GPP要求,如频谱屏蔽和邻近信道泄露比(ACLR),并且有足够的余量来弥补模拟器件的失真效应。

表1给出了与3GPP要求相关的性能总结,包括每个参数提供的余量。针对DUC和DDC功能的3GPP兼容性测试以MatLab脚本的方式实现,脚本使用了硬件协同仿真(运行在Nallatech V4 XtremeDSP套件之上)。表1给出的性能数据就是由这些测试给出的。图8至图10显示出Matlab测试脚本得到的一些测试图,包括DUC频谱屏蔽、DDS性能以及DDC邻近信道选择性和阻塞测试。

采用运行全速12通道设计的V4 XtremeDSP套件还进行了进一步的实际测试。利用V4开发板上的14位数模转换器生成19.2 MHz的IF输出信号。DAC输出被馈送到安捷伦(Agilent)频谱分析仪中,如图11所示。

如图12所示,这一12通道设计带有一个图形用户界面(GUI)。该界面能够支持多种功能。例如,DUC输出可以通过DAC-ADC路径或内部反馈到DDC,经过下转换并显示在某个图形用户界面窗口中。

实施结果

综上所述,利用TD-SCDMA DFE IP库可以实现和配置从单载波、单天线,直到六载波、多天线的各种不同DFE配置,唯一的限制就是可用的FPGA资源。表2和表3分别给出了实现一个六载波、三天线配置的半区方案,和一个三载波、四天线配置的半区方案所需要的FPGA资源。换句话说,两种情况下实现全区设计也只需要两片SX25器件。两个例子的中频带宽为9.6 MHz。

结论

由于TD-SCDMA标准的波束成形(beam forming)要求,因此基站需要大量上变频/下变频(DUC/DDC)通道。本文表明利用赛灵思 V4 SX FPGA和赛灵思 TD-SCDMA DFE 库可以实现高效快速的符合3GPP标准的TD-SCDMA数字前端(DFE)解决方案,从而使设备供应商能够集中更多精力来实现产品差异化并加快产品的上市时间。