一种基于VHDL的通用全数字电路人工神经网络的设计

2008-05-20

作者:蒋 垒, 李东生

摘 要: 从分析人工神经网络" title="人工神经网络">人工神经网络的设计原理入手,阐述了全数字" title="全数字">全数字电路人工神经网络的设计方法。通过一个小规模前馈人工神经网络的设计实例,简要说明了利用VHDL语言及编译平台,完成一种可调整权值" title="权值">权值的通用人工神经网络的设计算法和流程。

关键词: 人工神经网络 VHDL 数字电路

人工神经网络(ANN)是一门起始于19世纪90年代,复兴于20世纪80年代的综合性学科,涉及生物、电子、计算机、物理等多种学科,有着非常广泛的应用前景。长期以来,人们都在想方设法了解人脑的功能,用物理可实现系统去模仿人脑的神经网络。其实现方法是多种多样的,总的来说可分为两种:一种是利用现代高性能的计算机形成具有模拟能力的通用软件来完成神经网络的预期功能;另一种是利用硬件直接实现神经网络,如模拟VLSI 实现、数字VLSI 实现、模数混合VLSI 实现。

迄今为止,人们利用C、Basic等高级语言开发了很多神经网络软件包,实现了许多算法和模型,但是用软件模拟的神经网络并不能达到真正的并行处理,且对计算机性能要求很高;硬件实现中的模拟VLSI,虽然速度快和集成度高、便于实现非线性运算,但精度低、对噪音和温度的变化非常敏感、设计复杂、突触权值存储困难;而硬件实现的数字VLSI,虽然免疫力强、速度快, 但是部件(如乘法器" title="乘法器">乘法器) 占芯片面积大[1]。不过,随着大规模集成电路和HDL语言的不断发展,数字VLSI设计日益成熟,EDA设计工具的不断更新换代,使得全数字电路ANN的实现工艺难度越来越小,集成度和可靠性越来越高;同时FPGA的现场可编程特性,又使得ANN的调整更加方便快捷,因而数字VLSI逐步成为ANN实现的发展主流。本文通过一个小规模前馈ANN的设计实例,简要说明利用VHDL以及QuartusII编译平台完成一种可调整权值的通用ANN的设计算法和流程。

1 人工神经网络的实现原理

人工神经网络就是采用物理可实现系统模仿人脑神经细胞的结构和功能的系统[2]。它把很多处理单元有机地连接起来形成网络,进行并行的工作;通过模拟生物神经细胞发出信息脉冲,控制网络的运行。神经细胞单元的信息是宽度和幅度都相同的脉冲串" title="脉冲串">脉冲串,而脉冲串的间隔则是随机变化的。例如某个神经细胞单元兴奋,其轴突输出的脉冲串的平均频率就高;若细胞单元不兴奋,则脉冲频率就低甚至没有脉冲。多个神经细胞单元的轴突脉冲可以加权,形成细胞单元的电位变化,电位变化累加超过一定阈值,就产生一个脉冲,通过控制阈值大小,就可以控制脉冲。人工神经元的示意图如图1所示。

图中,x1…xn表示其他神经元的轴突输出脉冲,ω1…ωn为其他神经元与第i个神经元的突触连接,ωi可正可负,分别表示兴奋和抑制,则:

在式(1.1)中,si表示神经元i突触后的累加值,θi为阈值。在式(1.3)中,vi为神经元i的状态,yi为神经元i的输出,它是一个单调上升的函数,且为有限值,这是由于生物体中神经元脉冲发放率有一个最大值,不能无限上升的缘故。

总之,人工神经网络由很多几乎相同的单元组成,这些神经元的输入与输出的函数关系为单调上升的非线性关系,它们之间的连接采用权的办法实现,每个神经元的输入是其他神经元输出的加权和,因此在电路实现中需要完成:

(1)实现神经元输入与输出的线性关系。

(2)实现两个信号的相乘。在神经网络中权的数量很多,加权的计算都用乘法完成,因此对应于两个信号相乘的电路必不可少。

(3)实现加权后脉冲累加。

2 一种前馈人工神经网络的全数字电路模型

在全数字电路组成的人工神经网络中,乘法是利用与门进行的。如图2所示,两个脉冲序列通过“与”以后的输出即为二者的乘积;两个脉冲序列的占空比为1/2和1/3,相“与”后,脉冲序列的占空比为1/6,从而达到相乘的目的。

权存储在寄存器中,寄存器可以与外界的计算机内存或EPROM相联,因而权可从外面写入。这意味着权的存储和权的改变没有什么困难,可以设计出可重构的人工神经网络模型。

累加器是用计数器完成的,从乘法器输出的脉冲串经过计数器实现累加,当累加到达阈值时即作为神经元的一个状态输出。

图3给出了一个简单的前馈人工神经网络的结构示意图[3]。图中,xi代表第i个输入,wij代表输入i与神经元j之间的权值,yj是第j个神经元的输出。则:

式中, f( )是激化函数(如线性阈值的sigmoid的函数)。

根据ANN的设计实现原理,可以把图3所示的网络结构设计成如图4所示的数字电路结构。

图4中,每个矩形框内部的电路构成一个神经元,在垂直方向上有几组移位寄存器,在水平方向上有个大的环形结构。垂直的环形移位寄存器存储着前面所有的权值,水平环行移位寄存器中装载的是输入信号。每个权值在自己的移位寄存器中的相对位置必须和输入值匹配。在每个垂直的环形移位存储器输出端有一个乘法器/累加器电路,用于对权值和输入信号进行乘-累加运算。运算的结果送给查找表(LUT),用于实现激化函数,得到输出yi。

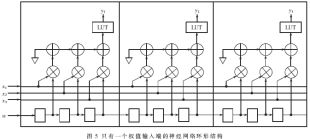

这个电路只用到了三个乘法器,有效地节省了资源。但是各个权值单独输入,不便于外部调整,不适于通用人工神经网络的编程。为此,设计如图5所示电路。图中,只使用一个输入端口加载所有的权值,权值按照顺序移位,直到每个寄存器都存储相应的权值,然后权值与输入相乘并累加,最终得到期望的输出结果。

3 VHDL语言的编程实现

为了使设计具有通用性,按照图5的结构用二维数组表示输入和输出,并自定义一个程序包,用来定义数组的数据类型:verctor_array_in和vector_array_out。由于程序包中的参数是通用的,可被多个实体即电路块调用,因而大大地提高了设计效率。

人工神经网络设计权值通用程序包如下:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

use ieee.std_logic_arith.all;

package currency_data_type is

constant b:integer:=3;——输入位数或者权重,改变b的值,可以调整网络的规模和大小

type vector_array_in is array(natural range〈〉) of signed (b-1 downto 0);

type vector_array_out is array(natural range〈〉) of signed (2*b-1 downto 0);

end currency_data_type;

同时,将输入位数、神经元的数目以及每个神经元的权重等参数放入类属说明中,由设计实体即设计电路外部提供,因而设计者可以根据需要方便地调整网络的结构和规模。

具体程序如下:

ENTITY dann IS

generic(n: integer :=3;——加入类属说明,可从外部通过类属参量重新设定电路规模

m: integer :=3;

b: integer :=3);

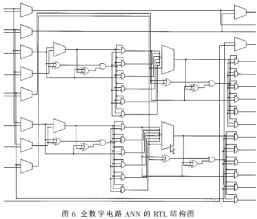

编写完的程序经过编译综合,便可得到如图6所示的门电路。

4 仿真分析

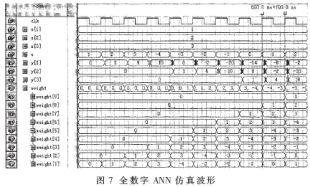

经过QuartusII对程序综合编译之后,还需要对电路进行波形仿真,以检验设计的正确性和程序的实用性。波形仿真如图7所示。

为了观测方便,在仿真时把输入信号固定为x1=1,x2=2,x3=3,时钟周期为10MHz。程序中共有九个权值,需要九个时钟周期来移入。因此到第9个周期的时候,由图7可知,权值weight[1..9]分别为[0,-1,-2,-3,-4,3,2,1,0],则输出为:

由于选用的FPGA器件不同,芯片内部产生延迟,导致波形中毛刺出现,但相对于模拟电路,精度和稳定性仍有很大的提高。在实际的系统设计中,可以根据需要并结合成本考虑选择恰当的芯片下载。

通过上面的设计,不难发现,数字电路在权值累加和非线性函数的计算上比较麻烦,综合编译的时候,数字乘法器占用的资源巨大,尤其是随着神经元和输入位数的增加,成平方倍增长。但是,以一套较好的EDA工具为平台,使用VHDL语言从顶至下设计全数字电路的人工神经网络,不仅能够避开电路搭配的繁琐,缩短设计周期,提高设计效率,而且由于FPGA器件的现场可编程特性,可以灵活控制网络的规模和结构,设计出可通用的网络模型,大大节省了开发周期,延长了设计寿命。

参考文献

1 Keulan E et al. Neural network hardware performance criteria.In:Proc of the IEEE Conf on Neural Networks,Vol. Florida,1994. 1885~1888

2 张立明. 人工神经网络的模型及其应用.上海:复旦大学出版社, 1993:3~4

3 乔庐峰(译).VHDL数字电路设计教程.北京:电子工业出版社, 2005:243~250

4 潘 松.VHDL实用教程.成都:电子科技大学出版社,2000

5 罗 莉. 数字神经元芯片的设计与应用.计算机研究与发展, 1998:798~802