新型DVB-C信道编码、中频调制的全数字实现

2008-05-30

作者:陈守金, 于鸿洋, 葛锦环

摘 要: 提出了如何在FPGA上实现DVB-C" title="DVB-C">DVB-C的信道编码" title="信道编码">信道编码和中频调制,概述了实用的编码调制的技术难点及其改进,阐述了各个关键模块的实现方法和性能指标,给出了整个模块的综合测试和仿真指标。

关键词: 有线数字视频广播(DVB-C) 数字控制震荡(NCO) Nyquist滤波器 半带滤波器 级连积分梳妆(CIC)滤波器 反SINC滤波器 等波动最优设计 规则有符号数(CSD) 相位锁定环(PLL) 正交幅度调制(QAM) 现场可编程门阵列(FPGA) 传输流(TS) 程序参考时钟(PCR) 星座映射" title="星座映射">星座映射 里德-索罗蒙(RS)编码

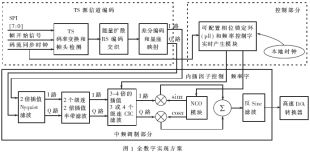

有线数字电视信道编码和调制的传统实现方式是将成型滤波输出的数据经过D/A变换后与外部的正交调制信号" title="调制信号">调制信号相乘得到基带的中频调制。由于在外部要产生严格正交的调制信号需要额外的电路,同时模拟器件温差特性会破坏它们严格的正交性,难以调试。本文采用图1的全数字实现方案。

该方案采用数字信号直接合成(DDS)技术产生正交信号,实现基带的中频调制。在DVB-C标准中,从复用器出来的TS流速率是连续可变的,而要求调制输出的是中频固定的基带调制信号,所以必须实时检测TS码流的速率,计算并补偿数字控制震荡器(NCO)的频率控制字,使得NCO输出稳定的正交调制信号。而基于本地时钟的可配置PLL,可以配置PLL的链路来实时产生所需的各级时钟,因此各个模块间具有严格的同步性,保证了模块间正确的时序,首先输入的TS码流进入缓冲器和变换模块,和可配置PLL一起保证了与内部信道编码时钟的同步,TS码流也变换为连续的无缝隙码流。由于DVB-C收端的数字机顶盒在64QAM下接受符号率范围在3M~7Mbps(TS比特流18M~42Mbps),所以在中频调制部分经过固定32倍内插" title="内插">内插后的速率变化范围就是96M~224Mbps,而一般FPGA芯片系统时钟可以工作在250M~300MHz,但是在代码综合后一般只能工作在180MHz以下。所以对中频调制部分的CIC滤波器内插因子设为3倍或者4倍可调,总的内插倍数为24或者32,对3M~7Mbps的符号率分为两段, 当符号率低于4Mbps时,CIC滤波器内插因子设为4倍;当符号率高于4Mbps时, CIC滤波器内插因子设为3倍。这样经过内插后的速率变化范围分别为96M~128Mbps和96M~168Mbps,这样既可以满足NCO的输入频率大于产生的正交信号频率2.5倍以上,又可以降低FPGA的系统工作频率。这种可变内插因子和实时补偿NCO频率控制字的实现方法避免了符号率过高而要求过滤TS码流空包来降低中频调制速率的麻烦,而且因为空包过滤涉及到PCR(程序参考时钟)修改和调整后的TS流速率不确定带来的难以与内部系统时钟同步的问题。这样充分利用了FPGA的可配置特性对DVB-C信道编码和中频调制进行全数字化处理,在提高集成度的同时也降低了实现的复杂性。

1 TS流信道编码

信道编码部分参照DVB-C标准,TS流首先输入环行缓冲器,进行码率变换和帧检测。当码率过低或过高时造成下溢出和上溢出,指示溢出错误;当检测没有TS流输入时,自动切换到空包发送状态,以维持调制器正常和收端机顶盒解调器的锁定。随后送给能量扩展器,RS编码和交织,完成序列的随机化和前向纠错编码(FEC)。交织部分进一步打乱码流的突发错误。

在星座映射和差分编码部分,把字节并行数据流转换为调制所需的符号流,在M-QAM调制下,一个符号对应的比特数为m=log2M,当M为{16,32,64,128,256},则m为4,5,6,7,8;码流变换是在控制器的控制下,根据设置取相应的m值;得到符号流后对高两位进行差分编码,以解决四重相位模糊问题。映射是在一定的映射逻辑下,把原始符号与星座图上某一位置的星座点联系起来,而该点在正交,同相两轴上的坐标值即为映射结果(自然码),两正交轴上的自然码输出值即为I、Q基带信号。为了得到优良的调制信号,星座点之间的最小间距应尽可能取大,但同时又受到成形滤波器输入比特数的限制,不可能取很大的输入宽度,否则滤波器的资源占用量将急剧上升。要求星座图是可变的,而系统中的成形滤波器数据输入宽度一般是固定的,所以应选取一个合适的映射结果集合,以利用成形滤波器的计算精度。以下给出用5bit表示的M-QAM,使从16QAM到256QAM的情况都能较好地利用成型滤波器的计算精度:16QAM:{±5,±15},32QAM:{±3,±9,±15}; 64QAM:{±2,±6,±10,±14};128QAM:{±1,±3,±5,±7,±9,±11};256QAM:{±1,±3,±5,±7,±9,±11,±13,±15}。本文主要针对64QAM进行了论述,笔者对映射的星座坐标采用补码表示,以方便后面滤波器的运算处理。

2 中频调制

2.1 2倍采样率奈奎斯特滤波器

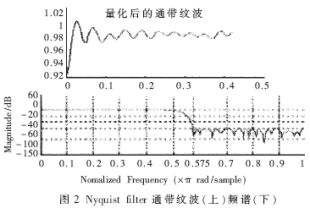

星座映射得到的5位宽的数据进入奈奎斯特(Nyquist)滤波器,由于DVB-C标准规定的平方根升余弦滤波器的滚降系数a为0.15,通带纹波小于0.4dB,阻带衰减大于43dB。在Matlab工具下采用等波动分段加权最优滤波器设计法,设计了2倍采样率fs,归一化后的Wp(通带截止频率即滤波器幅频下降到-3dB)为0.5π,Ws(阻带开始频率)为0.575π, 分段加权为三段加权:通带加权系数为0.977 45,过渡带加权为9.774 5e-005,阻带加权为1;得到了通带纹波小于0.006 089 1dB,阻带衰减大于67.677dB,阶数为96,97个抽头系数且奇对称的根升余弦滤波器。采用系数奇对称是为了保证有限冲击响应滤波器(fir)具有严格的线性相位。系数进行14bit量化后,通带纹波小于0.077 527dB,阻带衰减大于61.115dB,如图2。量化后的系数如下,由于对称性只给出前49个:{-2,-2,1,0,-3,-2,3,0,-5,0,4,-3,-6,4,5,-9,-5,12,2,-17,1,19,-6,-23,12,22,-21,-20,29,11,-41,2,51,-25,-64,57,76,-106,-88,174,98,-278,-107,450,113,-826,-118,2593, 4216}。

对Nyquist滤波器量化后的系数编写了Verilog代码。该滤波器的输入数据宽度为5bit,滤波输出数据宽为14bit。采用fir直接实现结构,为提高代码的运算速率,在分级求和中的每一级使用了寄存器;为减小在运算时溢出精度,内部乘积的宽度为19bit,求和宽度为26bit。对该设计Verilog代码在modelsim Se 5.8 下仿真,输入5位宽的随机数,仿真输出得到的数据在matlab下调用,得到幅频特性,如图3,可以看到该滤波器的频谱特性非常理想(注:图2在0~π归一化,图3在0~2π归一化)。

在quartus 4.1环境下,调用器件为stratix ep1s25f780c05的库,经过综合后该代码需要4300 LE(logic element),约77 400 逻辑门;由于要对星座映射后得到的I路和Q路正交信号分别滤波,而2倍采样率滤波器为上采样,在输入数据间进行了插零,所以实际的滤波器运算在每个时钟下只利用了一半的抽头系数,因而可以将IQ两路合为一路,用一个滤波器实现IQ两路滤波,其实现框图如4。

从图4中可以看到,乘和运算ab两部分对按序移入97个寄存器的偶数和奇数部分的数据分别进行计算。用IQ_syn作为选择信号,当其为0时,将乘和运算a部送给I路, 将乘和运算b部送给Q路,而当它为1时,将乘和运算a部送给Q路, 将乘和运算b部送给I路,这样经过IQ合路共用一个Nyquist滤波器,修改后的代码经过仿真,性能不变,综合后大约4 700LE,只增加约300LE,大大节约了硬件资源。同理后面的两个半带滤波器也进行了复用,进一步节约了硬件资源。

2.2 2个级连2倍采样率半带滤波器

由于Nyquist滤波后的信号要与NCO产生的正交信号相乘,信号必须在数字域中内插与产生正交信号的NCO输入速率相一致,参照一些文献介绍的内插滤波器设计,采用级连两个半带滤波器,以及3或4个级联积分梳妆(CIC)滤波器,在实现复杂度和性能上是一种比较好的实现方式。

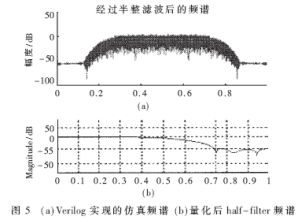

根据半带滤波器的特性:第一个2倍内插半带滤波器的设计参数:Wp为0.25π,Ws=π-Wp=0.75π(由于前面Nyquist滤波器作了2倍采样,所以归一化通带频率为:(1/2)*(1/2)π), 通带纹波为0.01dB,采用等波动最小阶设计法,得到14阶、15个抽头系数中心对称的半带滤波器。实际上半带滤波器有一半系数为零,所以只需要其一半的乘加器,对系数14bit量化,其值为h:{-31,0,168,0,-593,0,2 502,4 096,2 502,0,-593,0,168,0,-31},得到幅频特性如图5(b) ,阻带外衰减大于65dB。

对量化后半带滤波器系数编写Verilog代码,在modelsim Se 5.8下仿真,输入14位宽的随机数,仿真输出得到的数据在Matlab下调用,其滤波后的幅频特性如图5(a);由于半带滤波的输入14bit宽,所以内部乘积为28bit宽,求和为32bit宽,Verilog代码经过综合后约需要930 LE,约16740逻辑门。

同理第二个半带滤波器的设计参数:Wp为0.125π,Ws=0.875π,通带纹波为0.01dB, 得到最小6阶,7个抽头系数, 对系数14bit量化,其值为h:{-288,0,2 334,4 098,2 334,0,-288},阻带外衰减大于60dB;对实现的Verilog代码经过综合后约需要476LE,约8568 逻辑门(注:图5(b)在0~π归一化,图5(a)在0~2π归一化)。

2.3 级连型积分梳妆(CIC)滤波器

因CIC滤波器就是级连简单整系数矩形窗滤波器,它的系数全为整数1,其阶数与转换因子R一致,所以CIC滤波器的系统函数为: ,频率相应为:

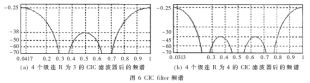

,频率相应为: 。这里分别给出转换因子为3和4的频谱,如图6(注:图6在0~2π归一化)。可以看到带外抑制分别为38dB、45dB,因为在CIC滤波前,已经作了8倍内插,当转换因子为3的3倍内插时,可以看到在通带(1/8×1/3=0.041 7)内,其频谱倾斜小于0.25dB;当转换因子为4的4倍内插时,可以看到在通带(1/8×1/4=0.031 3)内,其频谱倾斜也小于0.25dB,而DVB-C标准中允许的带内波动小于0.4dB。因此,CIC滤波所引起的通带倾斜在可接受的范围,不必进行CIC滤波补偿。

。这里分别给出转换因子为3和4的频谱,如图6(注:图6在0~2π归一化)。可以看到带外抑制分别为38dB、45dB,因为在CIC滤波前,已经作了8倍内插,当转换因子为3的3倍内插时,可以看到在通带(1/8×1/3=0.041 7)内,其频谱倾斜小于0.25dB;当转换因子为4的4倍内插时,可以看到在通带(1/8×1/4=0.031 3)内,其频谱倾斜也小于0.25dB,而DVB-C标准中允许的带内波动小于0.4dB。因此,CIC滤波所引起的通带倾斜在可接受的范围,不必进行CIC滤波补偿。

2.4 数字压控振荡器(NCO)和实时相位补偿计算

经过CIC滤波后出来的IQ两路符号速率被内插到原始符号速率的24倍或者32倍,该速率与NCO的系统速率一致。该信号与数字压控振荡产生的正交信号相乘,产生了正交的调制到中频的数字信号。这里数字压控振荡器产生正交信号的原理就是通常的数字信号直接合成(DDS)技术。由于输入的符号率是可变的,所以送给NCO的系统时钟也可变,并由可编程的PLL(相位锁定环)根据输入符号率调整,包括对CIC内插倍数的控制,使得NCO的输入时钟始终满足工作要求,同时控制NCO的频率相位控制字来达到输出稳定的中频。其原理框图见图1。其补偿的相位控制字inc_phase(16位宽)的计算原理如下:

inc_phase=(2N×Fm)/fs; fs=Fts×(8/M)×K×L

在这里,N为相位控制字的字宽16,Fm为NCO输出的正交信号的频率,需要调制输出的中频为36.65MHz, fs为NCO工作的系统频率,Fts为TS输入的字节速率,M为相应的2M正交幅度调制(QAM),K为CIC滤波前内插因子为8,L为CIC的内插转换因子为3或者4;假设M为6,L为4,将以上的值代入可得以下的公式:

inc_phase=(56 294)/Fts;

Fts的速率为2.25M~5.25Mbps,取小数位宽为10位,整数位宽为3位,共13位宽度,即表示误差为1kHz以下。在做除法运算时,被除数放大 210与除数对齐,其输出中频误差小于1kHz,满足实际应用对中频调制器的要求。在Fts的计算当中,笔者采用本地产生的1kHz信号作为TS输入时钟的计数使能信号,计数精度小于1kHz,其计数器的宽度等于上面除法宽度,为13位,将得到的值与(56 294×210位宽为26位无符号数)相除,得到的商从低位向高位取16位,送给inc_phase,作为中频补偿值。同理 L=3,用以下式子inc_phase=(42221)/Fts计算,得到的值作为中频补偿值。

2.5 反SINC滤波器

当数字信号要变回模拟信号、送给D/A变换器时,由于数模转换器的采样和零阶保持带来SINC效应,改变了在通带内频谱特性,所以在送给D/A转换前,要做相应的反SINC滤波。

调制信号的表示:S(ω)=αSα(ω)e-jωτ/2;Sα(ω)=sin(ωτ/2) /(ωτ/2);α=τ/Ts; τ是采样脉冲宽度;Ts=1/fs=2π/ωs是采样周期; 通常τ=Ts,因此有:S(ω)=sin(ωTs/2)/(ωTs/2)e-jωTs/2= sinc(ωTs/2)e-jωTs/2。

反SINC频谱函数为:|H(ω)|=1/|sinc(ωTs/2)|,0≤ω≤ωs/2。

选择频率补偿范围为:DC~0.4fs;纹波系数0.01dB,设计了一个11阶的滤波器,其系数做13比特量化,即:{-8,32,-90,206,-609,6304,-609,206,-90,32,-8},可以把系数放到matlab里面看它的频谱特性。

3 控制部分

整个控制部分包括:(1)对输入TS流的速率检测;(2)实时计算可配置PLL的链路数据,输出系统所需要的分配时钟;(3)调整补偿的频率控制字给NCO,使得输出稳定的中频正交信号;其中(1)、(3)部分上面已经介绍。对(2)部分,系统工作需要的各个同步时钟包括:信道编码时钟、星座映射时钟、后面的多级内插滤波用的时钟(Nyquist滤波时钟,两个半带滤波时钟,CIC滤波时钟)。对于信道编码时钟,假定输入的TS包是204字节,那么在RS编码时就不用进行码率变换;对于星座映射时钟,因映射点数的变化,致使码率发生变化,时钟也相应发生变化。对于后面的多级内插滤波用的时钟,它们和星座映射时钟构成简单整数倍关系,倍数由内插倍数决定。在复位后,首先计算TS流时钟,用得到的该数据去初始化PLL的各级时钟链路,完成后即得到了系统内部需要的工作时钟。这里笔者调用了FPGA专用库(stratix ep1s25f780c05的库)的可配置PLL,详细使用可以参照Altera 公司的技术手册和帮助文档。

4 整个模块的仿真、综合和调试

这里对整个模块作了前后仿真,将所写的各个模块的Verilog代码联合测试仿真,测试是在modsim 5.8se环境下进行的,前级滤波器输入的数据是5bit随机数,周期是320ns,经过32倍内插,变为10ns,滤波器输出速率变为100MHz/s,等于NCO的系统时钟频率,这样两路IQ信号可以直接与NCO输出的正余弦相乘,相加(注意实际使用的D/A器件有接受有符号数据和无符号数据区分,所以需在送给D/A之前转换一致,本文使用14宽的,AD公司的可以转换有符号数的芯片,所以与本文数据格式一致,不用转换到无符号格式),将仿真的输出数据在Matlab下分析频谱,如图7。系统速率是100MHz, 调制中频是36.65MHz,其中基带比特速率18.75Mbps,基带经过64QAM映射后符号率是3.125Mbps。从图7中可以看到,超外带宽(加上0.15滚降)是3.59375MHz,有效超外带宽(为超外带宽一半)是1.796875MHz。进行了32倍内插后,大大压缩了有效带宽,这样7MHz以下的符号率就可以容易地调制到中频上。从图7中可以看到,基带信号在分级内插下如何提高到与调制信号一样的速率,最(接上页)

终经过NCO调制后,可以看到信号频谱从基带搬到了所要求的中频点,整个基带信号带外抑制大于50dB,很好地抑制了镜像频谱,可以满足大多数的调制系统要求。

本文比较全面地论述了DVB-C的信道编码和调制方面的细节和难点,重点放在了中频调制部分,在对整个代码作综合后,需要11 000个左右LE。要整个符号率都能调制,NCO后端速率高于168MHz/s;笔者对代码进行了优化,例如对CIC滤波器中的多级求和抽取加入了寄存器和对反SINC滤波器系数采用CSD表示,用简单的移位加法代替乘法运算,综合后速率可达182MHz/s,这样整个DVB-C的符号率都可以调制。经过EFA的QAM分析仪测试,指标优于现在同类产品。不足之处是在使用FPGA的PLL时,有些时钟速率的分频和倍频值的表示由于舍入误差影响,某些速率误差大一些。

这里综合利用Matlab工具、modsim仿真工具、quartus 4.1 EDA软件开发,在Altera公司推出的高端FPGA芯片EP1S25f780-5的验证板上仿真验证;这样从理论到代码实现,从代码调试到仿真和测试,是一种比较快捷的开发验证手段,大大缩短了实现周期。

参考文献

1 王 方.多采样率数字滤波器的设计与实现.无线电通信技术, 2000;26(4)

2 赵民建.全数字多星座,可变符号率QAM调制器.电路与系统学报, 2001;6(1)

3 Shen,Bo Fudan UNIV. An X_SIN(X) FIR digital filter for DVB-C DAVIC modulator. Shanghai:China 2001 IEEE 0-7803-6677-8/01

4 Digital Video Broadcasting (DVB);Framing structure, channel coding and modulation for cable systems.En300 429 V1.2.1(1998-04) dvb-c

5 Koukourlis C.S. A general purpose differential digital modu-lator implementation incorporating a direct digital synthesis method. member, IEEE eee transactions on broadcasting, December 1993;39(4)

6 胡广书. 数字信号处理——理论,算法与实现. 北京:清华大学出版社, 1997

7 Bernard Sklar(美)著,徐平平译.数字通信——基础与应用(第二版).北京:电子工业出版社,2002

8 贝斯(美)著,刘俊,胡永生译.数字信号处理的FPGA实现.北京:清华大学出版社,2002