基于TR600语音编解码芯片的过程调用设计与硬件实现

2008-06-17

作者:王 沁, 赵凤海, 江山刚

摘 要: 介绍了TR600语音编解码芯片中过程调用的设计及实现方法,并与堆栈寄存器结构实现方式做了简要的比较,重点阐述了重叠寄存器窗口技术" title="窗口技术">窗口技术和存取算子对存储体交叉访问技术的原理、技术特点及其在TR600芯片体系中的具体实现。

关键词: 可重构体系 过程调用 重叠寄存器窗口 交叉访问

随着大规模集成电路的不断发展,软硬件界面的划分也发生了变化,VLSI设计方法的改进、IP技术的标准化以及系统在片(SOC)设计的日渐成熟,为软件功能逻辑硬件化实现提供了技术条件和实现手段。作为软件程序设计的重要部分,过程调用功能使用频度相当高,尤其在结构化设计中起到重要作用,因此,其硬件实现方法的优劣对于软件能否很好地移植到逻辑电路" title="逻辑电路">逻辑电路中起到了非常重要的作用。

TR600语音编解码芯片设计是基于MELP、SELP2(Sine Excitation Linear Prediction)等多种语音算法,采用可重构体系结构[1]和变长指令技术[2],实现了多种语音算法可在片配置的SOC设计。这款语音芯片结合了逻辑电路的快速性和用户指令编程灵活性的特点,通过分析多种语音算法,并提取资源共集,建立了资源、运算、网络可重构的逻辑电路,同时提取资源的可控节点,形成用户指令界面,以指令流形式控制逻辑电路,实现算法级应用功能。过程调用功能就是以指令形式提供给使用者,并通过指令译码器" title="译码器">译码器控制逻辑电路动作,实现具体功能。因此,过程调用功能的硬件实现效率和灵活度直接影响芯片整体的速度、规模以及用户指令编程的复杂度。

过程调用模型可简单描述为主调过程将被调过程置于某一位置,然后把控制权交给被调过程,执行完毕,再取回控制权,并返回运行结果,主调过程继续执行。因此过程调用需要2个步骤:调用过程和返回过程。过程调用需要处理的信息有:程序计数器(PC)值的保存与恢复、现场保护和参数传递" title="参数传递">参数传递。过程调用是一种典型的后入先出堆栈寄存器结构,这种实现方式虽已相当普遍,但也存在不足:(1)堆栈寄存器使用效率低,存储时间和空间浪费严重。因为参数传递的个数和规格因调用过程的不同会有所不同,而主调过程需要对所有可能被破坏的数据堆栈进行保护,而堆栈的宽度和深度会因满足过程调用最坏情况而设计得最大,而且嵌套调用会增加堆栈寄存器的开销。(2)堆栈寄存器结构无法解决调用过

程存取算子对存储体交叉访问的问题。为了给用户指令编程提供一个清晰的指令界面,在指令体系设计时,将LS存取算子设计成与SDRAM存储体一一对应的关系。单块存储体采用独立编址。而对于过程调用,主调过程传递实参可来源于任意存储体,被调过程的LS存取算子只能指向某一个存储体,这就产生了过程调用中参数传递的全局性与存取算子访问局部性之间的矛盾。

为了解决堆栈寄存器结构实现方式的不足,TR600语音编解码芯片采用了重叠寄存器窗口技术和存取算子对存储体的交叉访问技术来实现过程调用功能。

1 重叠寄存器窗口技术[3]

重叠寄存器窗口技术是一种寄存器堆设计方法,它将寄存器堆分成若干个寄存器子堆,相邻寄存器子堆有重叠部分并共同可见,作为子堆之间信息交互的窗口,称为窗口寄存器。寄存器子堆与其他子堆不重叠的部分只有自身可见,独立于其他子堆,称为局部通用寄存器。在外部控制电路作用下,同一时刻只有一个子堆对用户是可见的,可以进行读写操作。存储于局部通用寄存器的数据不会影响相邻子堆的操作,而存储于窗口寄存器的数据可以被相邻子堆直接使用。过程调用操作利用了局部通用寄存器的局部性和窗口寄存器的共用性的特点,将过程调用中的相关数据存入局部通用寄存器,避免了数据相关;将传递参数写入窗口寄存器,可以供被调过程直接使用,避免了寄存器之间的数据转移。因此,重叠寄存器窗口技术可以解决过程调用中的现场保护和参数传递的问题。

TR600芯片体系结构采用可重组思想设计了二组总线寄存器堆,每组寄存器堆有19个寄存器单元,每个单元由2组16位寄存器拼接而成,因此,单指令周期可以存取64位、32位、16位规格的数据。为了实现语音算法中多重嵌套过程调用,每组寄存器堆分为三层寄存器子堆,如图1所示。每层最多可以使用9个寄存器单元,调用操作可以在寄存器子堆内部,也可以在相邻子堆之间完成。总线寄存器堆控制信号" title="控制信号">控制信号由过程调用指令和寄存器读写控制指令经指令译码器译码产生。过程调用指令控制层计数器,产生层译码器使能,控制寄存器子堆换层操作。同时,控制输出选通器选择寄存器子堆输出;寄存器读指令产生当前子堆内寄存器单元输出选择信号,寄存器写指令控制产生数据通路选择和寄存器写使能信号。

TR600芯片体系结构采取2种过程调用方式:同层调用和换层调用。当一层寄存器子堆满足主调过程和被调过程的寄存器资源使用时,采用同层调用;当换层调用时,被调过程位于主调过程的下一层寄存器子堆,主调过程和被调过程分别控制所在层的寄存器单元,主调过程将传递参数写入窗口寄存器,被调过程则从窗口寄存器取入参数,以当前寄存器子堆为存储空间进行运算,并将需要传递的运算结果写入窗口寄存器,返回主调过程。如果被调过程内还含有调用,可以根据寄存器使用情况确定是同层调用还是换层调用,从而决定传递参数写入局部通用寄存器或是窗口寄存器。多重过程调用同样遵循这个过程。TR600体系中采用的语音编解码算法的过程调用最多涉及到17个子函数过程和5重嵌套调用,而重叠寄存器窗口技术都可以很好地解决这些问题。

2 存取算子对存储体交叉访问技术

存取算子对存储体交叉访问机制解决了存取算子访问局部性与过程调用中参数传递的全局性之间的矛盾。由于在指令体系设计时,将LS存取算子设计成与SDRAM存储体一一对应的关系,这就使得存取算子只能固定访问单块存储体。而对于过程调用,主调过程实参传递可来自于任意存储体,被调过程的形参却只能指向某一个存储体,这就要求主调过程要将实参转移到形参指定的存储体内,才能正确执行调用;而在数据转移过程中,可能引起数据相关,并且浪费数据转移时间。本设计的解决方法是对LS存取算子做变换,使其能够访问所有存储体,避免数据转移,并称其为存取算子对存储体的交叉访问。

为了在过程调用时使存取算子能够访问任意存储体,使被调过程形参可以指向任意存储体,采用在体系中添加段寄存器配置,标识存取算子访问存储体的信息的方法。因此用户可以通过设置段寄存器的值来动态改变LS存取算子对SDRAM存储体的访问关系。在初始化状态,段寄存器中的值表示LS存取算子与存储体访问是一一对应的,如图2所示。在存储体交叉访问时,过程调用指令通过重置段寄存器值,改变存取算子与存储体的对应关系,并在执行调用过程中保持不变,如图3所示。段寄存器值由过程调用指令来动态配置,用户在使用过程中调用指令时,要参照指令格式的要求,在具体指令域装载段寄存器的配置信息。段寄存器值经过译码器译码产生存储体控制信息,再经过逻辑运算产生每个存储体的控制信号,包括:输入输出数据通路选择信号以及存储体的使能、读写、地址控制信号。

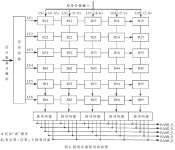

在TR600芯片体系结构中包含5块独立编址的SDRAM存储体,指令体系提供5个LS存取控制算子,分别为LS1控制读写RAM1、LS2控制读写RAM2……LS5控制读写RAM5。相应地,体系中提供5个3位段寄存器,标识过程调用时存取算子与存储体的对应关系。考虑到语音算法存在多重嵌套过程调用,每次过程调用时都可能发生存储体交叉访问的情况,因此设计了6层段寄存器阵列分别标识每次调用时存取算子与存储体的对应关系,如图4所示。执行过程调用指令时,段寄存器被重新配置,同时将过程调用的嵌套次数保存在层计数器。通过对层计数器输出的译码,产生段寄存器的层控制信息,包括段寄存器使能和段寄存器输出选择控制。通过段寄存器阵列的变换,实现每个存取算子对存储体访问的控制转换,再经过段译码器译码及逻辑运算产生存储体控制信号。例如,存储体RAM1使能信号(RAM1_E)可由5个段译码器译码产生的RAM1控制信号做逻辑“或”运算产生,变换逻辑运算即可以产生存储体的读写信号、地址控制信号和输入输出选择控制信号(本文不做详细论述)。

3 技术特点

(1)TR600芯片体系结构中重叠寄存器窗口技术采用可重组思想设计寄存器堆结构,提高了存储灵活性,适应了语音算法在过程调用中数据规格多样性的特点;多层窗口寄存器结构和寄存器堆局部可见的特点,解决了过程调用时的现场保护和参数传递问题,不需要设计现场保护参数的专用部件,减少了系统的时空开销。

(2)存储体交叉访问机制采用段寄存器标识存取算子与存储体的对应关系,由过程调用指令配置段寄存器,避免了因为参数传递而进行的存储体之间的数据转移;同时提供了清晰易读、编程灵活的指令界面,屏蔽了逻辑设计的复杂性,方便了用户指令编程。但过程调用功能的硬件实现与应用环境及体系结构是密不可分的,设计者应依据具体情况调整实现方案,如窗口寄存器堆的分层数目及段寄存器的层数,要根据具体算法中过程调用的最大嵌套层数而定,存取算子对存储体的交叉访问要依据体系结构提供的指令界面而定等,因为这些设计都具有灵活性和多样性。

本文论述的过程调用功能硬件实现方法也可以为其他应用设计借鉴,例如,在网络体系结构中,对多种通信协议的硬件实现以及RPC远程过程调用的实现都具有一定的参考价值。

参考文献

1 曲英杰. 可重构体系结构的特征及应用. 计算机工程与应用, 2001;(9)

2 Hennessy J L. Computer architecture: a quantitative approach. China Machine Press, 2002

3 David L. Weaver the SPARC architecture manual(Version 9). PTR Prentice Hall, 1994