基于MPC860和VxWorks的硬件防火墙设计及实现

2008-07-10

作者:李正熙1,于兴晗1,杨 扬1朱

摘 要: 介绍了一款以MPC860 PowerQUICCTM(Quad Unit Integrated Communications Controller)嵌入式通信控制器为核心、嵌入式操作系统VxWorks为操作系统,带有内容过滤功能的硬件防火墙设计与实现,详细阐明各种相关原理和关键技术。

关键词: MPC860 PowerQUICC 防火墙 嵌入式

与传统的PC架构硬件防火墙卡相比,利用MPC860实现的硬件防火墙在系统结构、体积、功耗、成本以及应用上具有很大的优势。本文介绍的利用MPC860开发的硬件防火墙设计方案,不仅充分利用了MPC860的功能,并且在实现上所采用的设计思路可以很容易地应用到其他嵌入式开发中。

本方案所使用的器件大部分是嵌入式开发中最经常使用的器件,所有的器件都具有一定的通用性,稍加改动即可应用到其他设计中。并且在该系统的基础上能很容易地开发出适用于其他方面的网络控制及通信系统。

1 系统硬件结构及工作原理

1.1 系统结构及特点

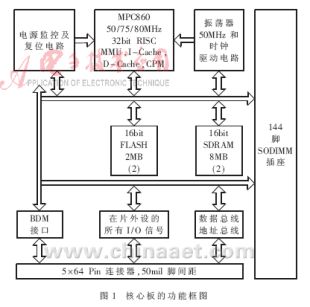

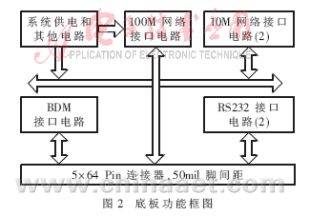

整个系统由核心板" title="核心板">核心板底板组成,核心板主要包括:核心CPU(MPC860)、Flash存储器、SDRAM存储器、标准的SODIMM接口、电源监控及复位电路、时钟驱动电路" title="驱动电路">驱动电路以及与底板相连的连接器。底板主要包括:100M网络接口电路" title="接口电路">接口电路、10M网络接口电路、BDM调试接口电路、系统供电电路、实现控制和监控功能的RS232接口电路和与核心板相连的连接器。方案设计中将整个系统分为核心板和底板两部分,分别设计实现,既降低了整个系统的开发难度又使系统易于维护、升级和和扩展。

1.2 系统的功能框图及工作原理

核心板的功能框图如图1所示。系统上电后,核心板通过连接器将电源从底板引上来。电源监控及复位电路开始工作,产生复位信号。在复位信号产生后,核心板的核心CPU(MPC860)开始启动。此时MPC860开始读取数据线(D0~D15)上的值,并通过读出的设置值来初始化CPU,主要包括存储器初始化、中断向量初始化、调试寄存器初始化等。当所有的硬件环境(主要指CPU中所有与操作系统相关的一些特殊功能寄存器,如SRR0、SRR1、CR等)初始化完毕后。系统会将控制权交给存储在Flash中的操作系统(如Linux、vxWorks等),通过操作系统管理系统中的所有硬件及任务。通过操作系统的调度来实现核心板管理、控制底板,并通过底板的硬件实现硬件防火墙的路由、网关及内容过滤等功能。

此外为提高核心板的适用范围,在核心板上增加了一个标准的SODIMM插槽和总线复用" title="复用">复用电路,SODIMM插槽可通过跳线支持16MB、32MB、64MB及128MB内存。总线复用电路支持外部总线仲裁(即在同一系统中可以将多块核心板加在同一总线上而不会产生冲突),本核心板可以不加任何改动即可用于其他系统中,包括多个核心板用于同一个系统[1][2]。

底板的功能框图如图2所示。当操作系统完全接管系统(包括对核心板底板所有硬件的管理)后,由操作系统发起任务控制底板上的资源,从而实现硬件防火墙的功能,包括路由功能、网关功能和内容过滤的功能。同时连接器将核心板所有的引脚引出用于扩展设计。这样设计的优点是当系统进行局部更新或设计时,只要更改底板的设计即可,并极大降低了开发难度,同时也提高了本系统复用率。

2 关键器件和关键技术

2.1 系统核心CPU MPC860

MPC860是由基于Motorola的MC68360嵌入式通信控制器演变而来的。PowerPCTM结构处理器由三个模块组成,即PowerPCTM内核、系统接口单元(SIU)及通信处理器模块(CPM)。这三个模块均采用32位内部总线。MPC860的主处理器是32位的PowerPCTM内核,能够实现内存管理(MMU)以及指令与数据的缓存;MPC860的系统接口单元中,存储器控制单元可支持多种高性能的存储器,包括SDRAM和Flash,还增加了PCMCIA控制器及实时时钟电路。MPC860采用了类似于MC68360的通信处理器模块(CPM),并增加了I2C通道。MPC860的CPM赠加了DSP功能。详细介绍见参考文献[1][4]。

LXT972是Intel公司推出的符合IEEE标准的快速网络物理收发器驱动芯片。适合于在100BASE-TX和10BASE-T标准的介质连接中应用。除此之外,它还提供一种非常易于应用在10/100M介质访问控制器(MACs)的独立介质独立接口(MII)。详细介绍见参考文献[2]。

LXT905是Intel公司生产的一款低电压通用10Base-T收发器,适合于IEEE 802.3标准的物理层应用。LXT905的功能包括曼彻思特编码/解码,接收器压制和发送脉冲波形休整、模糊识别、连接完整性测试和反极性探测和校正。LXT905驱动10Base-T双绞线仅用单一3.3V或者5V供电的隔离变压器。详细介绍见参考文献[3]。

3 设计方案的实现

3.1 硬件部分

由于篇幅有限,本文仅对系统的几个具有代表性的电路进行分析。

3.1.1 核心板部分

由于本系统的最终设计目标是设计出一台标准的嵌入式设备,所以在Flash存储器电路上选用了两片富士通生产的型号为MBM29LV160BT 16MB(2M×8/1M×16)位)的Flash存储器,使用方式为2MX8位,在电路连接上,它占用了MPC860的存储空间管理器的两块。两片Flash存储器的片选分别与MPC860的片选CS0#和CS1#相连。CS0接启动Flash,一般将系统的启动代码烧录进去。CS1接文件系统Flash,一般将操作系统和文件系统存储在该Flash中。

本系统所使用的SDRAM存储器为现代公司生产的型号为HY57V641620HG 4Banks×1M×16位Synchronous DRAM,使用的方式为将两片SDRAM通过字扩展构成4M×32位SDRAM,即共16MB的存储器空间。在物理连接上该两片SDRAM与MPC860的片选CS2#相连,占用MPC860的存储空间管理器的一块。除此之外该片选可通过跳线禁用。MPC860与SDRAM的接口电路如图3所示。

为了提高本系统的应用范围,增加系统的存储器空间,系统设计在核心板上增加了一个144pin的标准SODIMM插槽,通过跳线可以支持16MB、32MB、64MB、128MB的标准内存。与MPC860的片选CS5#和CS6#物理连接。

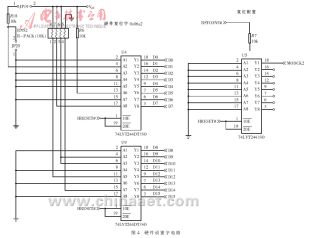

硬件设置字电路如图4所示。

在上电复位和硬件复位时,CPU除了读取时钟的缺省设置外,还会从数据总线上读取硬件复位设置字(HRCW),如图4所示。这个16位的HRCW字必须用上拉电阻进行设置,若未加上拉电阻,各数据位的值缺省为0。

在本系统中,硬件复位设置字用三个总线驱动器244加到数据总线上实现。硬件复位的设置字如下:

上电复位时,MODCK1=1、MODCK2=0,选则EXTCLK为OSCCLK的输入。

D0=0,即EARB=0,本系统采用内部总线仲裁机制。

D1=0(可通过跳线设置成1),即IIP=0,本系统复位中断向量的地址为0XFFF00100,可通过跳线设置成0X00000100。

D2=1,即BBE=1,本系统的启动设备不支持突发模式。

D3=0,即BDIS=0,启动禁止位禁止,硬件复位后内存控制器将所有的地址都映射到BANK0区。从CS0#连接的Flash启动。

D4=0,D5=1,即BPS=01,系统启动后数据总线工作在8位模式。

D6=0;系统保留位。

D7=1,D8=0,即ISB=10,系统复位后内部内存的起始地址为0XFF000000H。

D9=1,D10=1,即DBGC=11,对MPC860的一些复用引脚进行设置。使系统复位后MPC860的一些复用引脚工作在确定的引脚状态。以满足系统的需求。

D11=0,D12=0,即DBPC=00,MPC860的调试端口BDM调试端口管脚设置。

D13=0,D14=0,即EBDF=00,总线工作在全速模式下。

D15=0,即CLES=0;数据存储模式为大端模式。

在本系统中为减少PCB板尺寸提高系统的可靠性,采用Cadence Allego SPB15.1软件,布成8层板。在提高电磁兼容性方面。除了在PCB板上增加地层外,在PCB板的上下表面层板的周围增加贯穿孔以增加整个PCB板的抗干扰性和电磁兼容性。

3.1.2 底板部分

本系统中100M网络驱动电路为主要部分,是本系统与外网相连的接口,所有的网络数据都通过100M网口进入硬件防火墙,将核心板分析及处理后的数据通过10M网络驱动电路接口送入内网,所有的算法(如查找算法、IP数据包内容还原、甚至于高级的内容替代算法等)都在核心板实现。

本系统共有两路10M网络驱动电路。10M网络驱动电路是硬件防火墙与内网相连的惟一路径,硬件防火墙将处理过的数据通过该接口送入内网。同理,内网访问外网的数据也要通过它进入硬件防火墙。数据经硬件防火墙处理后,通过100M网络驱动电路送到外网。同时本系统所设计的两路10M网络电路还可以同时监管两个10M带宽的局域网,完成一些高级功能(如网络流量检测、内网监控、网关及路由功能等)。

由于功能和开发需要,系统在设计中采用了双串口" title="串口">串口方案。在开发中,一个串口可以作为与宿主机超级终端相连的调式串口,另一个可以作为与上位机通信的端口。

由于MPC860支持片上调试,且为降低开发成本,所以在本系统开发时所采用的调试手段是MPC860所支持的BDM 调试。

3.2 软件部分

主要包括启动代码编写、操作系统移植、硬件驱动编写以及应用程序等。由于篇幅有限,本文仅对BSP移植进行简单介绍。

3.2.1 BSP移植的步骤及建立BOOTROM的方法

(1)阅读手册,了解WINDRIVER的BSP模板编写规范、文件的组织,找到适合于目标处理器的模板。

(2)找到BSP模板以后,针对不同的CPU类型,确定基本BSP中所有寄存器配置是否适合当前的硬件(包括SDRAM、Flash)。如果不适合则做相应的改动,这主要是指rominits,config.h中的修改。

(3)如果有网络设备,则需要配置confignet.h。如果有串口,则需要修改sysSerial.c。修改sysLib.c中的硬件相关部分。

建立BOOTROM的方法:

(1)进行BSP定制,主要是修改bootline,配置configAll.h,config.h和Makefile。

(2)选择VxWorks的加载方式,然后配置target server,通过“build bootrom”图形对话框或者命令行建立bootrom,然后通过visionprobe将bootrom下载到目标机RAM中运行,或者将成功的bootrom用专门烧写器烧写到Flash中。

3.2.2 根据硬件修改BSP

在本课题中,将ads860目标板的BSP拷贝到目录installDir/target/config/ncut860t下,同时将all目录下的所有文件都拷贝到installDir/target/config/ncut860t/all目录下,之后针对本系统的硬件环境对BSP进行修改,同时修改相应的makefile。

注意:应将BSP拷贝到相应目录下后再启动Tornado,否则在Tornado的BSP列表中可能看不到新添加的BSP。

(1)config.h文件需要修改的配置(部分代码)

#define DEFAULT_BOOT_LINE

″motfec(0,0)host:vxWorks h=219.224.61.102 e=219.224.61.202 u=ncut pw=ncut″

#define CRISTAL_FREQ 50000000 /*50MHz*/

#define LOCAL_MEM_LOCAL_ADRS 0x00000000

/*Base of RAM*/

#define LOCAL_MEM_SIZE 0x02000000

/*32MB memory available*/

#define ROM_BASE_ADRS 0x02800000

/*base address of ROM*/

#define ROM_TEXT_ADRS ROM_BASE_ADRS+0x100

#define ROM_SIZE 0x00200000 /*2M ROM space*/

#define RAM_HIGH_ADRS (LOCAL_MEM_LOCAL_

ADRS+0x00500000)

#define RAM_LOW_ADRS (LOCAL_MEM_LOCAL_

ADRS+0x00010000)

#define USER_RESERVED_MEM 0x00000000

/*user reserved memory size*/

(2)makefile文件修改(部分代码)

TARGET_DIR =ncut860t

VENDOR=Motorola

BOARD=fw860t

ROM_TEXT_ADRS=02800100 # ROM entry address

ROM_SIZE=00400000 # number of bytes of ROM space

RAM_LOW_ADRS=00010000 # RAM text/data address

RAM_HIGH_ADRS=00500000 # RAM text/data address

HEX_FLAGS=-a $(ROM_TEXT_ADRS)

MACH_EXTRA=motFecEnd.o

CONFIG_ALL=F:workSetUpPpCTornado2.2targetconfig

ncut860tall

3.2.3 BSP常用的调试方法

开发调试BSP有两种方法,一种是使用仿真器通过BDM的方式一步步地跟踪调试;另一种是通过点灯的方式进行所谓的“黑”调。这里主要介绍“黑”调的方法。“黑”调的方法是通过 “灯”闪或用示波器测片选等,根据外部现象和所编的测试代码进行比较分析来调试程序。进行黑调的首要条件是串口部分代码已经调通,宿主机可以通过串口与目标机的通信,然后再调试BSP的其他部分。

BSP调试流程分成两部分。首先是位于BootRom中的Boot代码,它的作用是实现配置硬件和启动VxWorks下载程序;接下来是下载后跳转到VxWorks的入口地址运行操作系统和应用程序。

ROM中的启动代码部分:

RomInit:在文件romInit.s中,它是程序运行的开始,实现判断启动类型,配置内核和非内核寄存器以及内存和外围设备的读写时序,因此可以在此处加入内存检测功能。闪灯功能函数也要在此加入。判断启动类型和配置寄存器的部分不需要改动。配置内存和外围设备读写时序部分要进行改动,这一部分的SDRAM、ROM、Flash、FPGA有相应的模板可以参考,是通过使用宏定义来实现的。一般是改动空间大小的屏蔽位,读写位数以及片选寄存器OR和BR。内存检测在这里实现较复杂,它根据相应的内存检测算法实现。主要是对地址线和数据线的检测,通过写入数据再读出数据来判断,使用“走步1”和“走步0”算法。闪灯在这一部分是强烈推荐的,因为闪灯才能定位程序的运行位置。

在RomInit函数结尾处,指针跳入RomStart(),RomStart()在BootInt.c文件中。它是系统运行的第一个C函数。这一部分是Wind River公司提供的标准程序,一般不需改动。该函数是C的入口函数,由汇编程序调用,主要完成清内存,将ROM中的程序拷贝到RAM,解压并跳至解压后的程序运行。

UsrInit在BootConfig.c文件中,主要实现硬件的初始化。其中涉及到串口、网口的初始化及CONSOLE的配置等。其中串口和网口的配置是BSP的重要部分。UsrRoot在BootConfig.c文件中,它主要是实现vxworks文件的下载,并且跳转到vxworks的入口地址,从而进入操作系统。

VxWorks文件中的代码部分:

SysInit在sysAlib.s中。它是VxWorks的启动代码,与RomInit的作用相同。对于这个文件,一般不需要改动。UsrInit在Usrconfig.c中,其作用与Boot中UsrInit的作用相同。他们都调用SysLib.c中的子函数实现相同的硬件初始化功能。UsrRoot在UsrConfig.c中,它的作用与Boot中的UsrRoot的作用类似,但是这里的UsrRoot最终是进入到应用程序中。

该硬件防火墙的特点是高性能、高稳定性和强兼容性,除了可以实现网关、路由、上位机监控的功能外,在硬件防火墙的功能上通过软件可实现典型的性能参数、1000个并发联接数、实现吞量20M、实现10M的安全过滤带宽、实现对VPN、IDS、Dos等的支持。

同时,本系统作为一种嵌入式开发的典型设计,核心板可以不作任何改动即可应用于其他嵌入式应用中。充分体现了嵌入式开发在后续开发中电路重复应用的优势。此外在设计中所采用的一些扩展性设计,如为增加系统存储器所加的标准SODIMM插槽、不同封装的晶振驱动电路,不但增加了该核心板电路的应用范围,而且在实际使用中也增强了该电路的稳定性。

参考文献

[1] Freescale semiconductor Co.Ltd.MPC860 PowerQUICC Family User′s Manual.Rev.3,2004,7.

[2] Intel Co.Ltd.LXT972A 3.3V Dual-Speed Fast Ethernet Transceiver Datasheet.2001,1.

[3] Intel Co.Ltd.LXT905 Universal 10Base-T Transceiver with 3.3v Support Datasheet.2001,1.

[4] 谢斌.MPC860/850嵌入式系统开发入门与指导.西安:西安电子科技大学出版社,2004.

[5] Freescale semiconductor Co.Ltd.Application Note《SDRAM and the MPC860》 03-19-98 Revised,01-11-00.