评价存储器的一个重要指标就是它的可靠性,在一般的数据存储中,几个位的错误可能不是很关键的问题,如果但是发生在某个敏感的数据上,这个小小的故障可能会导致严重的后果。因此,必须采取一些措施来及时检出并纠正出错的数据。目前常用的方法有:奇偶校验、CRC校验、重复码校验等。

ECC校验是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成ECC校验码。它能够检测并纠正单比特错误和检测双比特错误,但对双比特以上的错误不能保证检测。它克服了传统奇偶校验只能检出奇数位出错、校验码冗长、不能纠错的局限性。文中在高速大容量固态存储器的硬件结构基础上,详细介绍了ECC校验码的生成规则以及ECC校验流程,并用C语言和VHDL语言两种方法实现了该算法。

1 存储器的硬件结构及芯片介绍

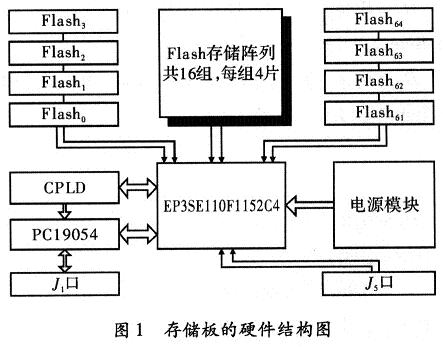

本存储器是以FPGA为控制核心,用64片Flash芯片构成存储阵列,采用CPCI接口实现数据的高速率存储。Flash存储阵列分为16组,每组4片,每组Flash芯片共用数据和控制总线。该存储器的硬件结构图,如图1所示。

存储板上的存储芯片用的是Samsung公司的高速大容量固态存储芯片K9W8G08U1 M Nand Flash Memory,其容量为1 G×8 bit,分为8 192个块,每个块又分为64页,1页有(2 k+64)Byte,其中一页有64 bit的空闲区。存储板上的控制芯片是Ahera公司的高端FPGA芯片EP3SE110F1152C4,它负责数据的缓冲和整个存储器的时序控制,并负责以页为单位生成校验码,并把校验码存人到页的空闲区内。下面以1页2 048 bit为单位介绍校验码的生成以及校验流程。

2 EGG算法分析及校验流程

2.1 EGG校验码生成规则

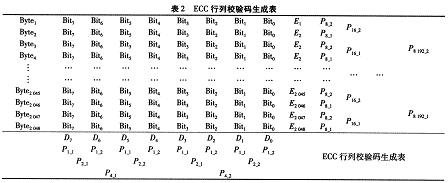

Flash在读写数据的时候是以页为单位进行的,一页有2 048个数据,所以可以以2 048 bit为单位生成校验码。每个数据有8位信息组成,可以把这2 048个数据看成2 048×8的矩阵,这样就可以分别生成行校验码和列校验码来分别校验。ECC校验中,每2 048个数据生成4个字节的校验码,这32位的校验码分成3个部分:6位的列校验信息,22位的行校验信息,其余的4位置1,ECC校验码组成,如表1所示。

其中P4_l,P4_2,P2_1,P2_2,P1_1,P1_2是列校验码,而P8_1,P8_2,P16_1,P16_2,P32_1,P32_2,P64_1,P64_2,P128_1,P128_2,P256_1,P256_2, P512_1,P512_2,P1024_1,P1 024_2, P2 048_1, P2 048_2, P4 096_1,P4096_2,P8192_1,P8192_2是行校验码。行列校验码生成表,如表2所示。

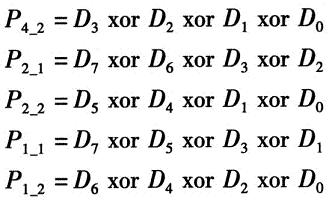

列校验码生成用数学表达式表示为

![]()

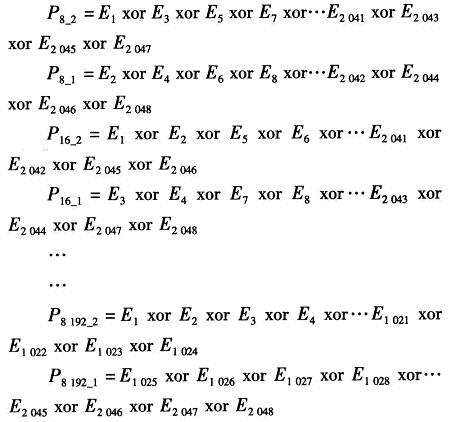

行校验码生成用数学表达式表示为

这里xor表示异或操作。

因为发生错误的数据位在该数据块中的字节的偏移量为

发生错误的数据位在所处的字节中的位偏移量为P4_1,P2_1,P1_1

所以根据字节的偏移量和字节中的位的偏移量即可确定该页数据中哪一位发生了变化。

2.2 ECC校验流程

当向NAND Flash的页中写入数据的时候,每2 048 bit生成4 bit的ECC校验码,称之为写ECC校验码,保存到每一页的空闲数据区中。

当从NAND Flash中读取数据的时候,每2 048 bit生成4 bit的ECC校验码,称之为读ECC校验码。校验的时候,根据上述ECC生成原理不难推断:将从页空闲区中读出的写ECC校验码和读ECC校验码按位异或,若结果为0,则表示不存在错;若4 bit的异或结果中存在14 bit为1,表示存在1 bit错误,且可纠正;若4个bit的异或结果中只存在1 bit为1,表示空闲区中的校验码出错;其他情况均表示出现了无法纠正的错误,校验流程图,如图2所示。

3 ECC算法的实现

3.1 C语言实现ECC算法

以一页数据2 048个字节作为测试数据产生ECC校验码,数据是0x00~0xFF,循环8次产生2048个数据,数据序列,如图3所示。

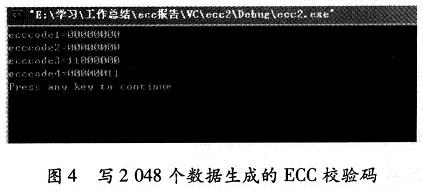

按前面的ECC校验码生成规则,2 048个数据应该生成4个校验码,生成的校验码,如图4所示,其中ecccode1,ecccode2,ecccode3,ecccode4是生成的4个校验码。

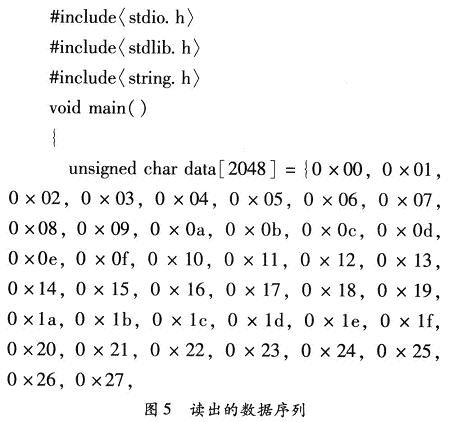

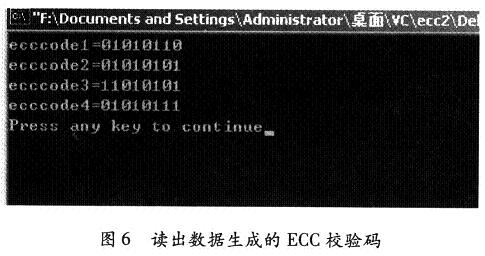

现在假设读出的数据中有一位数据发生了翻转,出现了一位数据错误的情况,即假设数据的第2 bit的最低位发生了翻转,0×0l变成了O×00,此时读出的数据序列,如图5所示。

3.2 利用VHDL语言实现EGG算法

文中以0x00~OxFF循环8次产生2 048个数据,利用VHDL语言编程,在QuartusII7.2下进行了仿真,得到了如图7所示的校验码。其中ecccodel =00000000,ecccode2=00000000,ecccode3=11000000,ecccode4=000000ll是生成的4个校验码,从图中可以看到利用VHDL语言得到的校验码和用C语言得到的ECC校验码是相同的。

4 结束语

文中介绍了ECC算法的一种实现方法,说明了ECC的校验流程,最后用两种方法实现ECC校验算法。ECC校验算法简单,软硬件均能实现,它能够检测并纠正单比特错误和检测双比特错误,所以可以为数据存储和通信系统提供一种强有力的差错检测手段。