引言

随着无线通信的发展,出现了多种模式的通信体制,为了满足互通性的问题,软件无线电" title="软件无线电">软件无线电的思想被提出来。所谓软件无线电,其中心思想是:构造一个具有开放性、标准化、模块化的通用硬件平台,将通信的各种功能通过软件来完成,并使宽带A/D和D/A转换器尽可能靠近天线,以研制出具有高度灵活性、开放性的新一代无线通信系统。由于软件无线电可以通过增加软件模块来增加新的功能,而且硬件也可以随着器件的发展而不断地升级,所以这一概念一经提出就受到了广泛的关注。

OFDM" title="OFDM">OFDM(orthogonal frequency division multiplexing,正交频分复用)是一种具有多种优点的传输系统,目前已经有很多应用,而且随着第四代(4G" title="4G">4G)无线通信系统的研究进入实质性阶段,OFDM极有可能成为4G中的传输方案。本文在此背景下,设计了一种基于软件无线电的平台,并在此平台上实现了OFDM传输系统,

系统结构设计

目前受器件的限制,软件无线电一般都采用中频采样的结构,这样做既兼顾了软件无线电的思想,又能在目前的器件水平下搭建实际可应用的系统。本文的软件无线电平台也采用了这一结构。随着无线通信系统的发展都在朝着高速率、可移动性方向发展,因此本平台的设计也必然要适应宽带无线通信系统的要求。

平台结构

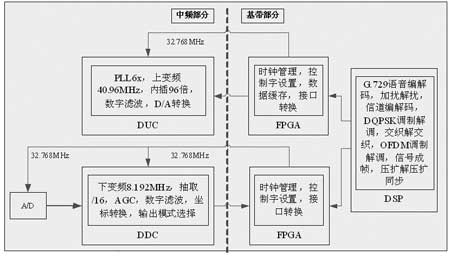

平台主要针对系统物理层中的中频和基带处理单元而设计。系统的结构如图1所示。平台由一个DSP(TMS320C6414T" title="TMS320C6414T">TMS320C6414T)、两片FPGA(Cyclone EP1C6Q240C8" title="EP1C6Q240C8">EP1C6Q240C8)、上变频芯片DUC(AD9857)、下变频芯片DDC(HSP50214B)等构成。

图1 平台结构图

根据信号处理模块和各芯片数据处理的特点,我们将各通信模块分配到不同的器件中来完成。DSP的主频很高,而且内部资源丰富,支持高级语言的编程,适合于串行的算法,用来完成协议和基带处理;FPGA配置灵活多变,虽然主频不太高,但是鉴于其并行处理能力突出,用于完成时钟分配、芯片设置、接口转换等;AD9857和HSP50214B是用于上下变频的ASIC,集成程度高,参数设置灵活,可以满足多模式的数字上下变频,数据速率变换和滤波。下面简要介绍一下平台上器件的性能。

器件介绍

● DSP

平台选用的DSP芯片是TI公司的TMS320C6416T芯片。该处理器属于32位定点处理器,主频1GHz,内部集成丰富的外设和接口。在指令结构上,扩展了寻址指令、位域指令、打包解包、控制转移等指令,增强了芯片的处理能力。在计算2048点的复数FFT运算时,可以在大约26 000个时钟周期内完成。

6416T主要包含的模块有:1)两个通用寄存器组,64个32位通用寄存器;2)8个功能单元,6个ALU(32/40b),两个乘法器(16×16);3)一共8.256Mb的两级缓存内部存储;此外,还有图1中没有列出的Viterbi编解码协处理器(VCP)和Turbo码编解码协处理器(TCP)。VCP支持500路7.95Kb/s AMR,TCP可以处理6路2Mb/s 3GPP。

接口方面包括:1)多通道EDMA控制器;2)多通道缓冲串口(MCBSP);3)高性能外部存储器接口(EMIF);4)可访问DSP的整个存储空间的主机口(HPI);这里不在一一列举。

● 上变频芯片AD9857

AD9857是一款高性能的数字上变频器,最高时钟为200MHz,根据外时钟的范围,可以选择0~80MHz的任意中频输出;芯片还具有两级内插功能,可以实现4倍固定内插和2~64倍可选内插倍数,便于多数据速率变换;14b的DAC。

● A/D变换器AD9051

ADC选用ADI公司的AD9051,最高采样速率达到60MSPS,10b输出,对于中心频率较低的中频信号可以进行直接采样,中频值较高的则运用带通采样方式。

●下变频芯片HSP50214B

HSP50214B是专用数字下变频芯片中综合性能最好的,除数字下变频外还具有最高255阶可编程FIR滤波器,0~96dB动态范围的 AGC自动增益控制,数据速率变换包括4~32倍CIC抽取和5级HB抽取,以及FIR1-16倍抽取,坐标转换,鉴频等功能,而且具有四种输出形式,接口灵活。

● FPGA

由于平台上的中频处理由ASIC完成,所以FPGA选用了CycloneⅡ EP1C6Q240C8,这是一款低端的FPGA芯片,逻辑单元只有6000门,主要用来完成时钟分配,接口转换,ASIC控制字配置,以及作为DSP的协处理器的补充。

该平台较好的整合了DSP、ASIC和FPGA,兼顾了系统的通用性和复杂度,ASIC的应用减少了系统配制时的软件设计复杂度。

OFDM收发信机的实现

OFDM技术是当前的热门技术之一,与传统的传输技术相比,OFDM具有:1)降低了子载波的数据速率,减小了无线信道引起的ISI,有效的降低了多径干扰;2)采用若干相互正交的子载波,频谱有重叠,最大限度地提高频谱效率;3)采用IFFT和FFT进行调制和解调,硬件实现简单;所以,尽管存在峰均比较高以及对频偏敏感等问题,OFDM仍然不失为一种性能优良的传输方式。目前采用了OFDM的标准主要有数字音频广播(DAB)、数字视频广播(DVB)、欧洲无线局域网Magic WAND、802.11、非对称数字用户线(ADSL)等。为此,我们在本平台上实现了OFDM的收发信机。

本OFDM系统采用了如下的基带和中频结构,如图2所示。图2中,音频编码采用了G.729标准,加扰采用了9位的反馈移位寄存器产生的伪随机序列,压扩部分为μ律压扩变换,其中μ=3。另外,系统子载波个数为2048,载波间隔1kHz,中频40.96MHz。图中的结构几乎包括了所有 OFDM系统应有的处理单元,具有一定的代表性,在此基础上经过必要的参数修改,可以演变出绝大多数标准的系统。为了便于接收端的同步处理,在帧结构上采用了类似DAB的结构,每帧76个符号,其中第一个符号为空符号,第二个符号为固定的相位参考符号。

图2 OFDM系统框图

通过对各模块功能的分析,并结合本平台上各器件的特点,对各模块的实现在平台上进行分配。图3显示了这种分配方式。

图3 OFDM系统处理流程

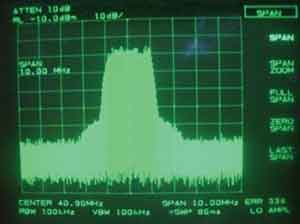

数据接口方面,发射端DSP将经过基带处理以后成帧的信号通过EMIF接口发送到FPGA的FIFO中缓存,然后数据进入数字上变频器,进行40.96MHz的上变频,上变频后的数据经过4倍固定内插和CIC的24倍内插后经过D/A输出,形成OFDM中频信号。如图4所示。

图4 OFDM中频信号频谱仪截图

接收端对中频信号以32.768MHz进行带通采样,数字下变频器对采样后8.192MHz的镜像频率进行数字下变频,之后对信号进行16 倍的抽取,使信号速率下降到2M,HSP50214采用并行直接输出的模式,分两路分别输出16b的IQ两路数据,FPGA通过并串转换,将数据通过 MCBSP送入DSP进行同步处理和基带处理,得到原发送信息。

结论

本文提出了一种基于DSP、FPGA以及ASIC的软件无线电平台,并在该试验平台上完成了OFDM系统的基带和中频设计,并且经过了实际的验证,系统运行情况良好,有效地支持多种通信模式,是一种应用广泛的软件无线电平台。目前正在对功率放大器的基带预失真技术进行研究,以进一步的改善系统性能。