一种脉冲多普勒雷达数字信号处理机的设计

2008-07-28

作者:王 旭,何佩琨,毛二可

摘 要: 针对某型脉冲对多普勒雷达的信号处理要求,设计了一种全数字化信号处理机" title="信号处理机">信号处理机。该信号处理机采用“ADC+FPGA+DSP+存储器”结构,具有体积小、重量轻、功耗低、可靠性高等优点。重点讨论了信号处理中数据采集、脉冲积累及目标检测的方法和实现。

关键词: 脉冲多普勒雷达;信号处理机;数据采集;恒虚警检测

多普勒雷达的主要功能就是在杂波背景下测量运动目标" title="运动目标">运动目标[1]。其基本原理是利用运动目标和背景杂波相对于雷达的径向速度不同而产生的多普勒频率不同,从而在雷达回波中区分运动目标。脉冲多普勒雷达发射信号为脉冲串,其回波信号也为脉冲串。雷达信号处理机实现目标检测和目标多普勒信号的提取。随着大规模集成电路的发展,高速高精度的ADC转换器件、大规模FPGA以及高性能数字信号" title="数字信号">数字信号处理器(DSP)日益普及,采用数字技术实现雷达信号处理得到了广泛应用。雷达数字信号处理机通常采用ADC转换器将雷达回波信号转换为数字信号,利用FFT运算实现多普勒滤波器组,然后利用恒虚警检测" title="恒虚警检测">恒虚警检测原理实现运动目标的检测[2]。

1 信号处理机设计要求和基本组成

本文设计的脉冲多普勒雷达数字信号处理机为某型号对海矢量脱靶量测量雷达专用信号处理机,其性能直接影响雷达的测量精度。信号处理机设计不仅要满足信号处理的精度和实时性要求,还要综合考虑整个信号处理机的低功耗、可重构性及可靠性。

本文设计的信号处理机的基本功能是:将多路雷达接收机输出的I、Q视频信号按距离波门进行模数转换变为数字信号并进行脉冲积累提高信噪比,然后从中检测运动目标,根据检测结果录取目标过靶前后的回波信号,通过数据传输接口将录取的数据传输到数据处理计算机,还能接收遥控指令,控制处理机的工作模式。

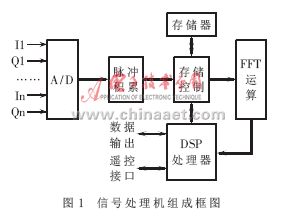

信号处理机采用“ADC+FPGA+DSP+存储器”结构实现,由ADC转换、脉冲积累、存储控制" title="存储控制">存储控制、FFT运算、DSP以及遥控接口和数据传输接口等部分电路组成,如图1所示。其中脉冲积累、存储控制、FFT运算由FPGA实现。DSP处理器除了完成恒虚警目标检测功能外,还作为整个处理机的总控制器控制处理机各部分的工作。信号处理机采用的数据流驱动方式进行流水处理,各组成部分也分别采用流水方式工作,保证了信号处理机的实时性。

这种实现方案既能满足信号处理的高速度和高精度的要求,且具有一定的灵活性和可扩展性,同时还能满足系统的功耗、体积、重量和可靠性要求。

2 信号处理机的设计与实现

2.1 ADC转换电路设计

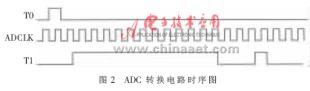

ADC转换电路负责将雷达接收机输出的目标回波I/Q视频信号转换为数字信号。雷达采用脉冲多普勒体制,雷达发射脉冲宽度为200ns,为了保证在每个距离波门都能采到一点,ADC转换时钟至少为5MHz,且与发射脉冲严格同步,以保证各距离波门的采样位置相对发射脉冲的延时一致。采样时钟的相位可以在一定范围内调整,以控制采样时刻相对发射脉冲的延时。本雷达作用距离为360m,另外为了进行接收机状态在线监测和校准,还在有效作用距离外发送参考信号,因此在进行数据锁存时,需要将发射脉冲后12个采样脉冲以及参考信号所在波门的数据进行锁存。ADC转换电路时序如图2所示。其中T0为发射脉冲同步信号,ADCLK为采样时钟,T1为数据锁存控制信号。T1信号前一个脉冲宽2 400ns,用于锁存有效作用距离内的回波采样信号;后一个脉冲宽200ns,用于锁存参考信号采样。ADCLK和T1由接收机输出60MHz时钟分频产生,该时钟与T0严格同步。ADCLK与T1相对于T0的延时通过控制分频器的起始相位进行调整,以确定距离波门的采样位置。

2.2 脉冲积累电路设计

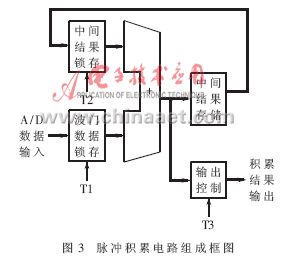

脉冲积累电路负责将ADC转换的结果按距离波门进行可变次数的积累,以提高回波信号的信噪比。由于雷达脉冲重复频率远大于目标多普勒信号频率,在不发生模糊的条件下,脉冲积累不但提高回波信号的信噪比,而且能降低实际输出数据的采样率,从而降低信号处理的速度和存储量要求。脉冲积累电路功能为:在每个脉冲积累周期内,对每个发射脉冲回波信号按距离波门将ADC转换数据依次进行累加,并将累加结果输出到存储控制电路。脉冲积累电路由数据输入控制器、累加器、中间结果存储器以及输出控制器组成。其组成如图3所示。

脉冲积累时序如图4所示。其中T1为距离波门锁存信号,负责按距离波门锁存ADC转换数据,读取中间结果,并将累加结果存储至中间结果存储器;T2为累加起始控制信号,用于清零中间结果锁存器,开始新的积累过程;T3为输出控制信号,用于积累结束后将累加输出至存储控制器。通过调整T2和T3的位置则可获得不同的积累次数。

2.3 存储控制电路设计

存储控制电路负责将经过ADC转换和脉冲积累的雷达回波信号分别送入数据存储器和FFT处理器,且能在DSP处理器的控制下将存储器中的存储结果输出。存储控制电路由用于产生存储数据地址的存储地址产生器和用于控制数据存储器总线控制权的总线切换电路组成。

数据存储阶段,存储地址产生器控制数据存储器的总线,将输出进行存储。数据输出阶段,则通过总线切换将数据存储器的总线控制权交由DSP控制,DSP将数据读出并通过数据输出接口输出。

为了正确保存目标过靶前后的回波数据,数据存储采用循环存储方式,即在检测到目标前,数据在存储器中按一定格式顺序存储,存储到存储器末地址后,则回到存储器首地址继续存储数据;当检测到目标后,继续存储一定数量的数据,然后结束存储。这样不但能存储检测到目标后的回波数据,而且能够保存一定数量的检测到目标前的回波数据,从而能够适当提高检测门限,降低虚警概率,而在事后数据处理过程中,利用更复杂的检测算法完整得到目标过靶前后的回波数据,计算脱靶量测量结果。

2.4 FFT处理器设计

FFT处理器用于将脉冲积累后的雷达回波数据以512点为一帧完成去直流、加窗、FFT、求模平方以及累加运算。信号处理器的存储单元保证了整个信号处理器的流水工作方式,提高了整体处理速度。其功能框图如图5所示。

去直流运算用于去除回波信号的直流成分,以便充分利用FFT处理器的动态范围,减少固定杂波的影响。加窗运算则用于以降低频谱泄漏。加窗运算器由窗函数存储器和乘法器组成,窗函数存储器存储窗函数的量化值。将数据和窗函数值读出送至乘法器的输入端,完成乘法运算后,将结果截断送至FFT运算器,完成加窗运算。两个乘法器并行处理,以便同时对I、Q数据进行加窗运算。

FFT运算用于将数据转换到频域以实现多普勒滤波器组。折中运算精度和速度,本设计FFT运算器采用逐级流水结构的16位块浮点结构实现按时间抽取基2(DIT-2)FFT运算。块浮点算法相对定点运算有较高的精度,相对浮点运算硬件结构简单,是定点和浮点运算的折衷,从而保证了信号处理机的高速和高精度要求[3]。

模平方运算用于将FFT运算结果就模平方获得雷达回波信号的功率谱以便进行目标检测。模平方运算由乘法器和加法器组成,其工作过程为首先将FFT结果的实部和虚部分别读入两个乘法器的输入端与自己相乘,然后将两个乘法器的输入相加即得模平方结果。

累加运算用于将多路接收机的回波共功率谱按距离波门进行累加,从而减小功率谱的方差,降低恒虚警检测的虚警概率。

FFT处理器在每帧时间段内要对所有4路接收机12个距离波门的雷达回波数据进行处理,处理完毕后,FFT处理器自动通知DSP将结果读出进行恒虚警检测。

2.5 恒虚警检测器设计

恒虚警检测器用于在回波中检测目标,采用单元平均恒虚警检测方案,由DSP处理器实现。

FFT处理器完成一帧处理结果后,发送中断给DSP处理器,DSP处理器按距离波门读取FFT处理结果,在目标可能出现的频率范围内进行选大处理,获得目标功率的估计值,计算功率谱的均值作为噪声功率估计值(计算平均时剔除目标所在频点附近几点以及存在杂波的低频分量),再计算两者的比值并与给定门限进行比较。如果超过门限则认为存在目标,否则认为没有目标。

为进一步降低虚警概率,在进行恒虚警检测时采用二元检测方案,在连续4帧中如果有3帧检测到目标才给出目标出现信号。

2.6 信号处理机的实现

本文设计的雷达数字信号处理机为基于DSP和FPGA的单板机,根据以上设计,该信号处理机有8路ADC转换电路、2片FPGA、数据存储器、DSP处理和外围电路以及对外接口电路组成。

ADC转换器件选用TI公司的ADS2806,它为双路ADC转换器件,可以保证I、Q两路信号的一致性,采样率为36MS/s,转换位宽为12位,满足系统要求。

脉冲积累和存储控制采用一片FPGA实现,FFT处理器采用一片FPGA实现。FPGA选用了Xilinx公司的Virtex II系列FPGA实现。脉冲积累和存储控制FPGA选用XC2V250-6FG456,FFT处理FPGA选用XC2V1000-6FG456。两片FPGA均采用VHDL语言按自顶向下的方法进行设计。设计文件经过仿真、综合、映射、布局、布线及仿真,达到设计要求。

数据存储器采用有掉电保护功能的NOVSRAM。NOVSRAM的读写控制时序与普通SRAM一样,其内部含有锂电池和保护电路,可以在断电情况下保存数据。

DSP处理器选用ADI公司32位浮点处理器ADSP21060(SHARC)。其外围电路有FLASH存储器,用于存储固化程序;上电复位和看门狗电路,用于监测程序的运行等。

信号处理机对外接口有数据传输接口和遥控接口。数据传输接口用于输出存储器存储的目标回波数据,采用USB2.0接口,其传输速度可达480Mb/s,可以满足数据高速传输的要求。USB2.0接口芯片采用Philips生产的ISP1581实现。遥控接口用于接收遥控指令并返回处理机工作状态信息,采用并行接口实现,由中断信号实现握手。

3 恒虚警检测算法分析

恒虚警检测算法为整个雷达信号处理机的核心算法,算法采用单元平均恒虚警及二元检测方案,在FFT处理结果上以频率分辨单元为基础进行检测[4]。

由于杂波多普勒频率比目标多普勒频率低,FFT处理结果中杂波数据主要集中在低频部分,需检测的运动目标多普勒频率范围位于频域无杂波区,因此在FFT处理结果中剔除存在杂波分量的低频部分即可降低杂波对目标检测的影响。

接收机噪声可以看作高斯白噪声,无目标回波数据则为高斯白噪声的采样,假设其方差为σ2。如果数据中存在目标回波信号,回波信号幅度为A,则其信噪比为:

经N点FFT运算后,信号分量幅度为NA,噪声方差为Nσ2,信噪比为:

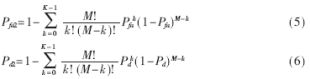

这样利用R个频率分辨单元以阈值T进行目标检测的虚警概率和检测概率分别为[4]:

本文测量雷达目标为过靶段的反舰导弹,其回波在连续数帧内都应该存在,为了进一步降低虚警概率,提高检测概率,可以采用二元检测方案,即在连续M帧内如果有多于K帧检测到目标,则判断为目标存在。采用二元检测方案的检测概率和虚警概率如下[5]:

实际设计中,设定单次检测虚警概率小于10-5,二元检测策略为在连续4帧内有3帧检测到目标,FFT点数N为512,频率分辨单元个数R为100。由(3)式可得检测阈值T为0.194,由(5)式可得二元检测的虚警概率为4×10-15,由(4)式可得目标信噪比为0dB时单次检测的检测概率0.96,由(6)式可得相应的二元检测,检测概率为0.99。

本文讨论了一种脉冲多普勒雷达信号处理机的设计与实现,用于在雷达回波中自动检测运动目标并录取目标回波数据。该处理机采用“ADC+FPGA+DSP+存储器”结构实现,降低了电路设计的复杂度以及信号处理机的体积、重量、功耗等,有效提高了系统可靠性,且具有一定的灵活性和可扩展性。该信号处理机已经在某型对海矢量脱靶量测量雷达上得到应用,取得了很好的效果。

参考文献

[1] MERRILL I S.Introduction to Radar System(Third Edition)[M].Boston,McGraw-Hill,2001.

[2] 赵保军.可适用于多种模式的雷达视频信号处理研究[R].北京:北京理工大学博士后研究工作报告,1998.

[3] 韩颖.高速专用FFT处理器的设计与实现[R].北京:北京理工大学硕士学位论文,2003.

[4] DILLARD G M,SUMMERS B F.Mean-level detection in frequency domain[J].IEE Proc-Radar Sonar Navigation,

1996,143(5):307-312.

[5] 何友.雷达自动检测与恒虚警处理[M].北京:清华大学出版社,1999.