箭载遥测变换器测试台的设计与实现

2008-07-30

作者:袁伟涛, 张斌珍, 刘文怡

摘 要: 针对箭载数字量" title="数字量">数字量变换器" title="变换器">变换器性能参数要求,开展了其相应测试设备即测试台" title="测试台">测试台的设计与研究。给出了测试台各路信号的具体设计方法,阐述了以单片机80C196KB、CPLD和可编程M82C54计数器/定时器为核心的实现原理。

关键词: 测试台; 数字量; 计算机字; CPLD

在火箭发射试验中, 常用遥测系统获取其内部各系统的工作状态参数和环境数据,为评定火箭的性能及故障分析提供依据。数字量遥测变换器作为遥测系统箭上设备的核心,它的主要功能是控制接收箭上各种飞行参数。数字量遥测变换器的可靠性是影响遥测结果的核心环节,其精度关系到火箭研制和实验过程中的实验数据可信度,其性能关系到实验的成败。如何准确、客观、高效地评价数字量遥测变换器的性能,是数字量遥测变换器生产中的重要环节。数字量变换器测试台是遥测设备专用的测试设备,它是集信号自动发生、自动检测、自动计量和数据分析于一体的大型应用系统,是专门针对数字量遥测变换器检测用的测试系统。

本课题就是针对某型号火箭数字量遥测变换器进行相应数字量变换器测试台的设计与研究。

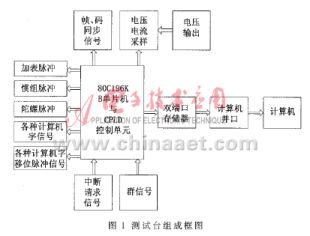

1 系统原理设计

测试台组成框图如图1所示。当系统上电后,单片机开始复位,此时单片机执行一系列的初始化操作,然后以非屏蔽中断信号(即帧同步信号)作为系统程序操作循环执行的触发源,在每一帧的循环中,主程序通过判断路同步信号一边读群信号,一边进行查询操作,在查询过程中不停地对双端口存储器中放置系统工作状态的单元进行查询,把查询的结果与系统的设定相比较,从而进行相应的操作。

当读出电压检测代码操作后,就转向电压操作子程序。

当读出电压拉偏试验时,就转向相应的拉偏电压输出子程序。

当读出的是系统设定代码时,系统等待计算机向双端口存储器中写入操作代码后,转向相应的程序。

当读出的是系统自检代码时,系统执行自检操作。

当读出的是系统脉冲信号" title="脉冲信号">脉冲信号代码时,系统执行发送脉冲信号操作。

当接收到计算机字中断后,系统执行相应的计算机字操作。

2 源电压检测电路的设计

根据要求,测试台能对供电电压进行实时检测和显示。在本系统中使用80C196KB中的内置10位A/D" title="A/D">A/D转换器。由于供电电压的变化范围为28~31V,而A/D变换器的量程为0~5V,所以必须通过分压电路才能输入到A/D中。为了防止由于继电器接通后电压的波动而损害单片机,在芯片的模拟量输入端加了5V稳压二极管来实现过压保护。

在工作时,控制软件启动A/D变换器进行采集,经过若干时间(>A/D转换时间)后再读入A/D转换结果,并将其写入规定的存储器单元中。计算机在每次读入群信号的同时也读入了电压值,并加以显示。

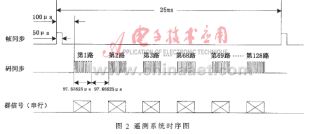

3 帧路码同步信号设计

由系统输出的信号的波形及时序要求(图2)可以知道,帧、码同步信号是2路勤务信号,用于数字量变换器内部的时序控制。根据这2路信号,变换器进行群信号的编码以串行的形式发送给测试台以供读取。所以在设计过程中测试台也需要相应的副帧、路、码同步信号来配合群信号的读取。根据群信号的时序特征和副帧、路、码同步信号生成一个数据时序文件。然后将其写入一片EPROM存储器28C64,28C64共有13位地址线,可以计算出存储单元为8 192个,如果通过地址推进来输出这些同步信号,可以得出地址推进速度为:25ms/8 192=3μs。地址推进采用具有异步复位端的二进制计数器4024来完成。4024的时钟源是用CPLD对4.096MHz的晶振信号进行12分频得到的。

开始工作时, 4024在时钟信号的推动下进行地址的循环,从而在28C64的D0、D1、D2数据端输出3路勤务信号。4024的异步复位端直接接地。2片4024级联后连续的地址推进可实现连续的勤务信号输出。具体电路设计如图3所示。

设计完毕后,经测试,得到图4帧、路、码同步信号波形,满足了系统要求。

4 脉冲信号设计

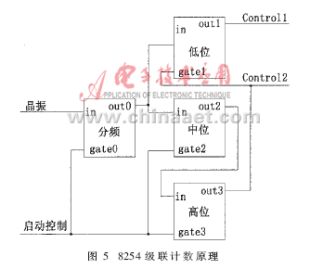

由于本测试系统的信号是多路、不同频率、不同个数,且可以同时发出单个脉冲和组脉冲,互不影响,实现起来有一定的难度。因此采用以80C196KB单片机为控制核心,以8254计数器/定时器为主要实现芯片,采用CPLD为逻辑控制单元。

4.1 加表脉冲信号

加表脉冲信号共6路,正表和负表各占3路,正负表的频率和脉冲数均可以通过计算机进行预置。计算机通过双端口存储器与单片机的通信对8254编程来预置加表脉冲信号的频率和脉冲数。

由于加表脉冲可预置范围在0~224个,这样至少需要24位计数器,但1片8254中每个计数器是16位的,因此采用了3片8254,共计9个16位计数器,在功能分配上,1个用于产生3μs的时钟信号,2个用于控制奇数和偶数路的频率,3个级联用于产生奇数路的脉冲个数,3个级联用于产生偶数路脉冲个数,如图5所示。将8254作为任意分频器使用,通过对8254计数器初始值的设置就实现了惯组脉冲频率的设定。

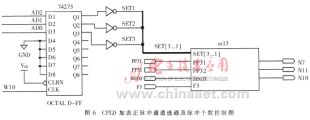

对计数的每个计数器来说,必须有初始值,且初始值不能为0,即低位、中位和进位必须有初始不为0的数。这样才能保证计数的顺利进行。当脉冲个数设置为1时,中位和进位必须为0,这时就需要修改计数器的工作模式,只需把低位计数器改为模式五(硬件触发的选通信号发生器),初始值设为10即可。此时发出的脉冲是单脉冲,其脉冲宽度为一个时钟周期,经示波器观察,其宽度为250ns左右。CPLD加表正脉冲通道选通及脉冲个数控制如图6所示。

加表负脉冲、惯组正负脉冲和陀螺正负脉冲与加表正脉冲实现方法一致。

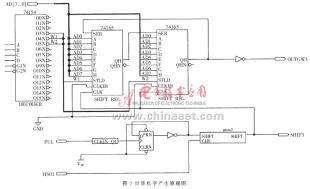

4.2 计算机字信号的设计

由技术要求知计算机字信号是一路串行输出的“0”、“1”码。计算机字信号共9个字节72位。因此选用了可以移位/置数的8位移位寄存器74165,计算机字共72位,需9片74165移位寄存器。每片的移位/置数端由译码器74154产生的译码信号控制,而74154的地址输入端为80C196KB单片机的高4位地址线。工作时测试台先通过单片机对译码器进行控制来产生控制信号对74165进行并行置数,然后将PL端变低进行移位操作,移出计算机字。原理图如图7所示。

利用系统计算机字的实现方式与箭机计算机字实现方式相似,这里不在赘述。

5 双机通信接口电路的设计

此系统包括软件和硬件两大部分,硬件靠软件支持工作。计算机和单片机不仅能向各部分硬件电路预置各种状态,而且还能从硬件电路中读出各种输出信号、数据,加以判断、识别。这就需要有一套在软件和硬件中进行联络的电路,由此以双端口存储器作为主要元件,实现了计算机和单片机的数据交换。

双机通信接口电路如图8所示,单片机的地址和数据由双端口RAM IDT7130的A口进行读写操作,计算机的地址/数据则由B口进行读写操作,二者可以实现异步读写操作,单片机通过握手信号来与计算机实现数据交换。

测试台通过与变换器联试,满足了系统提出的各种要求,能够对变换器的各项性能进行检测。检测结果:预设置频率与实现频率的误差在±0.02%以内,脉冲个数准确率达100%。

参考文献

[1] 张文栋.存储测试系统的设计理论及其在导弹动态数据测试中的实现[D].北京:北京理工大学,1995.

[2] 任勇峰.飞航导弹遥测匹配装置自动监测系统研究[D].太原:华北工学院,2000.

[3] 陆航局.记录参数测试系统研制方案.北京:北京航空航天大学出版社,1999.

[4] 肖明清,宋凯,张弘,等.多路ADC、DAC在空空导弹发射架自动测试系统中的应用.测试技术学报,1996,(3).