卷积码是一种性能优良的差错控制编码。本文阐述了卷积码编解码器的基本工作原理,在MAX+PLUS2软件平台上,给出了利用复杂可编程逻辑器件设计的(2,1,6)卷积码编解码器电路,并进行了编译和波形仿真。

综合后下载到复杂可编程逻辑器件EPM7128SLC84-15中,测试结果表明,达到了预期的设计要求。

数字通信系统进行数据传输时,由于噪声干扰的影响,不可避免地会在接收端产生差错。为了在已知信噪比的情况下达到一定的误码率指标,在合理设计基带信号,选择调制、解调方式,并采用均衡措施的基础上,还应采用差错控制编码等信道编码技术来降低误码率。分组码和卷积码是差错控制编码的两种主要形式,在编码器复杂程度相同的情况下,卷积码的性能优于分组码,因此,在诸如GSM、IS95和CDMA2000等无线通信标准中,都应用了卷积码。

CPLD是复杂可编程逻辑器件的简称,它是20世纪90年代初期出现的高密度可编程逻辑器件,采用E2CMOS工艺制作,一般由三种可编程电路组成,即可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线。它可利用EDA技术中的MAX+PLUS2作为开发工具,将设计的电路图或硬件描述语言编写的程序综合成网表文件写入其中,制成ASIC芯片。CPLD的突出优点是可反复编程,集成度非常高,数据速率快,同时具有较大的灵活性。

1、卷积码编码器

卷积码(又称连环码),是由伊莱亚斯(P.Elis)提出的一种非分组码。它把k比特信息段编成n比特的码组,该码组不仅同当前的k比特信息段有关,而且还同前面的(N-1)个信息段有关联(N为大于1的整数)。通常,把卷积码记作(n,k,N),其中k为输入码元数,n为输出码元数,N为约束长度,表示编码器的存储器级数。卷积编码属于信道编码,主要用来纠正码元的随机差错,它是以牺牲效率来换取可靠性,利用增加监督位,进行检错和纠错。

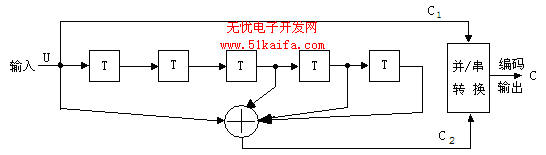

卷积码编码器是一个由k个输入端、n个输出端,且具有(N-1)节移位寄存器构成的有限状态记忆系统,通常称为时序网络。卷积码的编码方法有三种运算方式:离散卷积法、生成矩阵法和多项式乘积法。此外,卷积码的编码过程还可以用状态图、码树图和网格图来描述。本文设计的编码器原理图如图1所示,它为(2,1,6)卷积码编码器(图中T为移位寄存器)。

|

|

图1 卷积码编码器原理图 |

由图1可知,该编码器是一个(2,1,6)卷积编码器,即k=1(一个输入端)、n=2(两个输出端)、N=6(5级移位寄存器)。

若输入信息序列为:U=(u0 u1 u2 …),则对应输出为两个码字序列:

C1=(c0(1)c1(1)c2(1)…) C2=(c0(2)c1(2)c2(2)…)

其相应编码方程可写为:C1 = U * G(1) C2 = U * G(2)

式中“*”表示卷积运算,G(1)和G(2)表示编码器的两个冲激响应。编码输出可由输入信息序列U和编码器的两个脉冲冲激响应的卷积得到,故称卷积码。由于编码器有5级寄存器,所以冲激响应至多可持续到6位,图1所示卷积码编码器的两个冲激响应可写成:

G(1)=(100000) G(2)=(100111)

若输入信息序列为:U=(11010101),则:

C1=(11010101)*(100000)=(1101010100000)

C2=(11010101)*(100111)=(1100010001011)

经过并串转换,最后输出的码字为:C=(11110010001100100001000101)

2、卷积码解码器

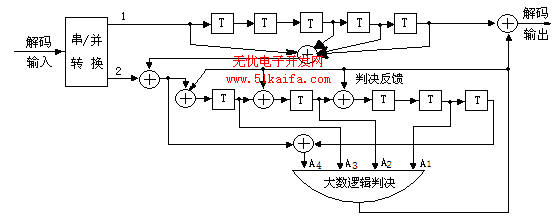

卷积码的解码可分为代数解码和概率解码两类。大数逻辑解码器是代数解码最主要的解码方法,它即可用于纠正随机错误,又可用于纠正突发错误,但要求卷积码是自正交码或可正交码,对于(2,1,6)卷积码大数逻辑解码器原理图如图2所示。

|

|

图2 (2,1,6)卷积码大数逻辑解码器原理图 |

图2中,输入的数字序列,经串/并转换为两路,1路输出信息码元,2路输出校验码元。解码器把接收到的1路中的每一段信息元送入编码器求出本地校验元,与其后面收到的校验元模2加。若两者一致,则求出的伴随式分量为0,否则为1。把加得的值送入伴随式寄存器中寄存。当接收完码段后开始对第0码段纠错,若此时大数逻辑门的输出为1,则说明第0码段的信息元有错。这时正好第0子组的信息元移至解码器的输出端,从而纠正它们。同时,纠错信号也反馈至伴随式寄存器修正伴随式,以消去此错误对伴随式的影响。如果大数判决门没有输出,则说明第0子组的信息元没有错误,这时从编码器中直接把信息元输出。

3、利用CPLD实现的卷积码编解码器

3.1 利用CPLD实现的(2,1,6)卷积码编码器

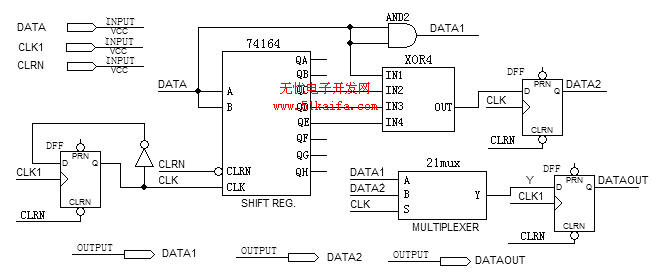

基于CPLD设计的(2,1,6)卷积码编码器电路如图3所示。

|

|

图3 基于CPLD设计的(2,1,6)卷积码编码器电路 |

图3所示卷积编码器的引脚关系为:引脚DATA表示数据输入,引脚CLK1表示“并串转换”输入时钟,引脚CLK表示数据时钟输入引脚(它可由CLK1二分频得到),引脚DATA1表示卷积编

码器输出码C1的数据,引脚DATA2表示卷积编码器输出码C2的数据。引脚DATAOUT表示卷积编码器经过并串转换,最后输出的码C的数据。

5级移位寄存器从MAX+PLUS2器件库中调用一个串入并出移位寄存器74164实现;4级模2加从MAX+PLUS2器件库中调用一个4级异或门“XOR4”组成;“21mux”实现2位并串转换;编码器的两个输出码和并串转换后的输出码之后各增加了一个D触发器“DFF”,其作用是利用D触发器的输入端对毛刺信号不敏感的特点,去处CPLD器件输出引脚上可能产生的毛刺。

3.2 利用CPLD设计(2,1,6)卷积码解码器

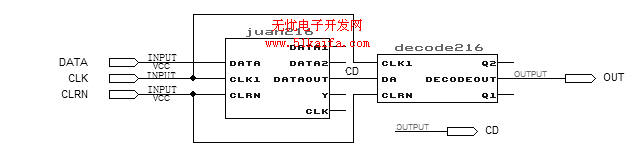

基于CPLD设计的(2,1,6)卷积码大数逻辑解码器如图4所示。

|

|

图4 基于CPLD设计的(2,1,6)卷积码大数逻辑解码器 |

(2,1,6)卷积码大数逻辑解码器由2位串/并转换电路,监督码产生电路,校正子计算电路和大数逻辑电路组成。

2位串/并转换“chuanbing12”是从MAX+PLUS2器件库中调用4个D触发器“DFF”,2个非门设计成一个二分频电路和一个一输入二输出串/并转换电路并进行元件包装入库而形成,其中时钟CLK由CLK1二分频得到。

监督码产生电路是从MAX+PLUS2器件库中调用一个串入并出移位寄存器74164,一个4级异或门“XOR4”组成。

校正子计算电路是从MAX+PLUS2器件库中调用5个D触发器“DFF”,4个异或门“XOR”设计组成电路。

大数逻辑电路是从MAX+PLUS2器件库中调用4个与非门“NAND3”,1个与非门“NAND4”和1个异或门“XOR”设计组成电路。

3.3 利用CPLD设计(2,1,6)卷积码编解码器

将设计的(2,1,6)卷积码编码器进行元件包装入库为“juan216”,将设计的(2,1,6)卷积码解码器进行元件包装入库为“decode216”,之后将它们连接在一起,可组成的(2,1,6)卷积码编解码器如图5所示。

|

|

图5 (2,1,6)卷积码编解码器 |

(2,1,6)卷积码编解码器的引脚关系为:引脚DATA表示数据输入,引脚CLK表示输入时钟(其速率是数据速率的二倍),引脚CLRN表示清零端,引脚CD表示(2,1,6)卷积码编码器输出,引脚OUT表示(2,1,6)卷积码解码器输出。

4、实验结果

利用MAX+PLUS2开发工具进行编译和仿真,(2,1,6)卷积码编解码器仿真波形如图5所示。

|

|

图6 (2,1,6)卷积码编解码器仿真波形 |

其中“DATA”是数据输入端,系统输入的数据比特若为“11010101”,经卷积码编码器后,延时约150ns后“CD”输出的数据比特为“11110010001100100001000101”;再经卷积码解码器,延时约1us后“OUT”恢复输出数据比特为“11010101”。仿真结果表明:编码器输出数据与理论计算完全一致。然后将综合后生成的网表文件通过ByteBlaste下载电缆,以在线配置的方式下载到CPLD器件EPM7128SLC84-15中,从而完成了器件的编程。上电后,在输入端加入待编码信息,用数字存储示波器测试编码器输出,实测结果完全正确,达到了设计要求。

5 结论

本文阐述了卷积码编解码器的工作原理,利用CPLD器件,设计出了(2,1,6)卷积码编解码器。本文作者创新点是利用了EDA技术中的MAX+PLUS2作为开发工具,将设计的电路图综合成网表文件写入其中,制成ASIC芯片,突出优点是可反复编程,集成度非常高,数据速率快,自顶向下设计,查找和修改错误方便,同时先仿真,正确后再下载测试并应用,因而具有较大的灵活性;根据本文提出的设计思路,可方便的设计其它卷积码编解码器,有广阔的应用前景。

[参 考 文 献]

[1]谢平,陈建辉,胡记文.基于CPLD的模数转换组合研究[J].微计算机信息,2005,26:153-155.

[2]龙光利.CDMA手机卷积码编码器的设计与FPGA的实现[J].陕西工学院学报,2005,21(2):1-3.

[3]王新梅,肖国强.纠错码——原理与方法.修订版[M].西安:西安电子科技大学出版社,2001.

[4]赵曙光,郭万有,杨颂华.可编程逻辑器件原理、开发与应用[M].西安:西安电子科技大学出版社,2001.

[5]樊昌信,张甫翊,徐炳祥等.通信原理.第五版[M].北京:国防工业出版社,2002.

[6]阎石.数字电子技术基础[M].第四版.北京:高等教育出版社,1999.