CobraNet网络音频路由器的设计

2008-07-30

作者:祁才君, 赵 凡, 王培良

摘 要:论述了CobraNet网络音频技术的发展,分析了嵌入CobraNet技术的CS1810xx网络音频处理芯片,并给出了应用CS1810xx设计CobraNet网络音频路由器" title="网络音频路由器">网络音频路由器的方法和硬件结构。着重讨论了CS1810xx的以太网控制接口设计,CS1810xx的固件" title="固件">固件装载,主机接口的软件设计" title="软件设计">软件设计等。

关键词:CobraNet;专业音频;MCU;网络协议

目前,CobraNet技术已成为专业音频领域实时网络传输的一种标准,不同厂商的CobraNet产品可以无缝连接。

CobraNet技术解决了专业音频信号" title="音频信号">音频信号在以太网平台上传输时的实时性、时钟同步、流量控制和传输控制等关键问题[1,2,4]。CobraNet技术采用等时同步传输技术在数据链路层传输音频数据包,等时延时最低等于 ms。它将局域网内的CobraNet设备分成Conductor(主设备,一个系统仅有一个)和Performance(从设备,数量不限)设备,主设备等时发送时钟节拍包(beat pack),从设备从节拍包中解析主设备的时钟并用其同步本地时钟,时钟同步算法产生的时钟跳变(jitter)小于25ppm。每个CobraNet设备在发送或接收音频数据包前必须向主设备发出请求包,主设备汇总局域网内所有请求,根据流量分析结果决定该音频包能否发送或接收,从而避免网络堵塞。音频数据包支持点对点、点对多点和广播三种发送方式。应用CobraNet技术在一根CAT-5类线上最多可传输64个通道的专业(采样率48kHz,分辨率20/24bit)数字音频信号。

ms。它将局域网内的CobraNet设备分成Conductor(主设备,一个系统仅有一个)和Performance(从设备,数量不限)设备,主设备等时发送时钟节拍包(beat pack),从设备从节拍包中解析主设备的时钟并用其同步本地时钟,时钟同步算法产生的时钟跳变(jitter)小于25ppm。每个CobraNet设备在发送或接收音频数据包前必须向主设备发出请求包,主设备汇总局域网内所有请求,根据流量分析结果决定该音频包能否发送或接收,从而避免网络堵塞。音频数据包支持点对点、点对多点和广播三种发送方式。应用CobraNet技术在一根CAT-5类线上最多可传输64个通道的专业(采样率48kHz,分辨率20/24bit)数字音频信号。

2000年,美国专业音频芯片制造商Cirrus Logic收购了peakaudio公司,并将CobraNet技术芯片化,开始批量生产CS1810xx和CS496xx(带DSP处理功能)两个系列的CobraNet网络音频处理器" title="音频处理器">音频处理器。

本文研究应用网络音频处理器CS1810xx设计CobraNet网络音频路由器的方法。

1 CS1810xx网络音频处理器[5]

CS1810xx是内嵌TCP/IP协议栈、可以运行CobraNet技术固件(音频包的编解码算法、时钟同步算法等)的音频处理器。CS1810xx采用LPQF144脚封装,引脚可分为处理器外部总线、主机接口HMI(Host Management Interface)、数字音频和异步通信等。

1.1 处理器外部总线

处理器外部总线相关引脚包括16根数据线DATA15~DATA0;20根地址线ADDR19~ADDR0;存储器选通信号#CS1、#CS2,读写信号#WE、#OE和外设等待信号IOWAIT等。

利用总线可以扩展外部存储器或扩展带微处理器接口的以太网控制器。

1.2 主机接口控制

主机接口是CS1810xx的主要外设(主机控制有motorola和intel两种读写时序),主机控制信号相关引脚:

(1) 读写方向控制HR#W、主机使能#HDS、主机选通#HDS、主机端口数据请求输出#HREQ、主机端口中断请求输出#HACK。

(2) 主机控制数据线HDATA7~HDATA0,宽度8位。

(3) 主机低位地址4位,对应HADDR3~HADDR0。

1.3 数字音频

数字音频相关引脚:

(1) 时钟类:主时钟(通常是512倍帧时钟)DAO-MCLK,移位时钟DAI1-SCLK/DAO1-SCLK,帧时钟DAI1-LRCK/DAO2-LRCK。

(2) 同步串行音频输入数据(每根2个通道)DAI1_DATA3~DAI1_DATA0。

(3) 同步串行音频输出数据(每根2个通道)DAO1_DATA3~DAO1_DATA0。

串行音频输入有两种模式。模式1如图1,一帧内每根同步串行输入/输出内部包含两个通道(一个立体声)音频信号。模式2如图2,一帧内每根同步串行输入/输出内部包含四个通道音频信号。

1.4 其他

异步通信由UART_TXD、UART_RXD和UART_TX_OE组成。

信号DBCK和DBDATA提供I2C接口,主要用于引导程序(bootloader)的装载。

2 CobraNet网络音频路由器的硬件设计

图3是CobraNet网络音频路由器的硬件设计框图。

2.1 CS1810xx部分电路

CS1810xx部分电路主要有以太网接口、并行FLASH接口、串行音频数据输入/输出和下载接口等。

CS1810xx内部并没有集成以太网控制器,为此选用带通用微处理接口、包含MAC控制器并集成10/100MPHY接口的以太网接口单芯片DM9000E作为CS1810xx的接口芯片。DM9000E的PHY输出直接与磁芯变压器一体化的RJ45网头相连,原理设计如图4。

并行FLASH用于存储处理器的固件,选用1MB的AM29LV800DB-90EC。AD选用Cirrus Logic公司CS5396[6],DA选用Cirrus Logic公司CS4396[7]。

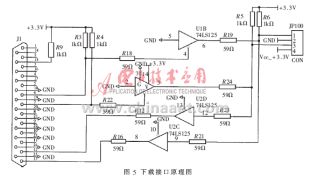

下载接口用于处理器装载引导程序,其接口原理设计如图5所示。

2.2 MCU部分

MCU通过CS1810xx处理器提供的主机接口与处理器进行通信。考虑CS1810xx提供8位主机接口数据宽度,MCU选用Philipp公司的P89V51RD2八位微控制器,MCU相关接口有RS232异步通信、LCD液晶显示、键盘输入等,其中LCD选用144X32的内嵌汉字字库的点阵液晶LM3037。CS1810xx地址锁存和译码、MCU地址锁存和译码等逻辑控制选用Xilinx公司的CPLD XC9572-100PQ实现。

3 CobraNet网络音频路由器的软件设计

软件设计包括CS1810xx固件装载和MCU软件设计两部分。

3.1 CS1810xx固件装载

CS1810xx固件装载[3]由bootloader装载和应用程序装载两部分组成。

用电缆将计算机的并口和目标板的下载接口相连,运行Cirrus Logic公司提供的windows环境下的DOS应用程序CID,执行命令“e lcm2.cmd”实现bootloader装载,完成以太网接口和主机接口等驱动安装。将目标机接入以太网并重新启动,运行Winows环境下的另一个工具软件Discovery,该软件会自动查找局域网内的CobraNet设备,给目标机分配IP地址,并利用工具选项update firmware下载处理器的最新应用软件。

3.2 MCU软件设计

MCU软件设计包括液晶显示控制、RS232通信协议制订和处理、键盘扫描和与CS1810xx之间的主机接口通信等。其中,最关键部分是与CS1810xx主机接口部分程序的编写。

MCU与CS1810xx之间通信的实质是对处理器CS1810xx内存映射存储单元的读写。HMI主机接口的数据宽度是8位,而CS1810xx内部核心是数据宽度等于32位的Motorola定点DSP处理器。

CS1810xx内部主机接口部分提供8个8位寄存器,其地址由基址HMI-BASE,即CS1810xx的主机选通或使能信号 (#HDS、#HEN)地址,和低位HADD3~HADD0之和决定。0~8位地址分别对应信息寄存器MSG_A(MS)、MSG_B、MSG_C、MSG_D(LS)和数据DATA_A(MS)、DATA_B、DATA_C、DATA_D(LS)。

主机可以向CS1810xx发送10种消息。消息功能和对应信息寄存器的值如表1所示。

CS1810xx收到消息后,将主要处理结果存放在信息寄存器MSG_D中,MSG_D中各位对应的状态是:bit0——信息翻转位,bit1——接收包有效位,bit2——包发送完成位,bit3——地址转换完成位,bit4——可写区位。

主机读写过程如图6,设置地址过程如图7,程序代码如下:

void SendMessage(uchar message )

{

int msgack = ReadRegister(HMI_BASE+MSG_D); //保留原信息

WriteRegister(HMI_BASE+MSG_D, message);

//写入新消息

while(!((msgack^ReadRegister(HMI_BASE+MSG_D))

& 0x01)) //等待第0位翻转

}

void SetAddress(ulong address )

{

//设置第16~23位、第8~15位、第0~7位地址

WriteRegister(HMI_BASE+MSG_A,(uchar)((address&0xff0000)

>>16));

WriteRegister(HMI_BASE+MSG_B,(uchar)((address&0xff00)

>>8));

WriteRegister(HMI_BASE+MSG_C, (uchar)(address&0xff));

SendMessage(0xB3);

//发地址转换消息,并等待CS1810xx响应

while( !(ReadRegister(HMI_BASE+MSG_D) & 0x08);

//等待地址写入转换结束,开始读地址转换消息

WriteRegister(HMI_BASE+ MSG_C, 0x0 );

//信息寄存器MsgC写入0

SendMessage(0xB5); //发送消息,结束地址设置

ReadRegister(HMI_BASE+DATA_D); //清除数据管道

}

MCU微控制软件由主循环、按键中断和串行接收中断等组成。

PC机通过SNMP协议发送命令改变CS1810xx中的接收或发送音频通道的BUNDLE编号,改变音频路由状态。MCU在主循环中还不断扫描CS1810xx各音频通道的音量,然后将音量值以音量柱的形式在LCD界面上显示。

路由控制还可以通过按键中断和串行中断实现。收到中断路由命令后MCU直接通过CS1810xx的主机接口改变CS1810xx的路由,这种路由方式的响应速度要快于SNMP协议的网络命令,尤其是按键控制可以脱离PC对CobraNet网络音频路由器实施路由控制。

本文研制的具有8个通道输入和8通道输出的CobraNet网络音频路由器已经批量生产,并以多个硬件设备为基础构建了网络音频系统,配合控制软件,实现了音频信号的全数字化传输、交换、监测、智能切换等功能。

参考文献

[1] GROSS K P. Media access control for isochronous data packets in carrier sensing multiple access systems, Patent No. US 5,761,430, Jun. 2, 1998.

[2] GROSS K P. Exploiting shortest path for improved network clock distribution, Patent No. US 6,973,152,B2, Dec.6, 2005.

[3] Cirrus Logic, Inc. CobraNet programmer’s reference version 2.5, Feb, 2006.

[4] Cirrus Logic, Inc., Audio Networks An Overview, 2001.

[5] Cirrus Logic, Inc.,CobraNet Silicon Series Hardware User’s Manual Version 2.2, Mar., 2006.

[6] Cirrus Logic, Inc.,192 kHz D/A Converter for Digital Audio-CS5396/7,Sep.,1997.

[7] Cirrus Logic, Inc., 24-Bit, 192kHz D/A Converter for Digital Audio-CS4396,Jul.199924-Bit.