当今生活的时代,多媒体通信的出现和流行是大势所趋。随着数字电视(DTV)、IP视频传输、数字相机、无线视频、医疗图像和视频监控等应用的兴起,目前提供音频和数据服务的许多系统都会随实时视频技术的应用而有不同程度的扩展。在最近的技术发展表明,芯片逻辑门密度和嵌入式功能的极大提高为多媒体处理设计提供了激动人心的设计可能性。同时,还可以利用可重配置芯片所提供的额外灵活性来提供具有吸引力的解决方案。本文中,我们将考察多媒体系统的要求以及多媒体处理所需要的一些基本构建模块。然后,我们将讨论将实时视频应用的抽象描述转换为采用FPGA技术有效实现的设计所需要的设计流程。最后,我们将考察新兴压缩标准JPEG2000和MPEG-4的需求。在多媒体处理解决方案领域,FPGA技术能够以合适的价位点提供实现下一代多媒体算法所需要的带宽、设计工具和芯片,从而满足多媒体设计人员的要求。

多媒体通信

由于新兴压缩和通信技术的快速应用,对多媒体通信的需求每年都在提高。这些技术大部分都被ISO、ITU、SMTPTE和IEEE等标准机构所采纳。多媒体压缩对于有效地使用可用的存储和带宽资源非常关键。ISO MPEG和J

PEG工作组和ITU一起开发了可满足音频、视频和系统压缩需求的标准。两个最近完成的标准JPEG2000 和 AVC (高级视频编码解码器, MPEG-4 Part 10/H.264)标准,提供了前所未有的性能水平,但密集的计算需求比较有利于FPGA技术,而不是传统基于处理器的解决方案。

这些压缩标准致力于满足范围广泛的应用领域,并按运算的"类"(profile)和"级"(level)来划分。类定义了编码解码器中所使用的标准算法功能集合。级则定义了特定类中的参数选择集合,如帧大小和速率。这些标准服务的多样化市场包括数字视频广播、IP多媒体传输、无线多媒体传输、视频监控、医疗图像和数码相机。这些市场在采集、计算和显示方面有着非常不同的要求。

压缩芯片市场预计到2006年时将从目前的15亿美元增长到28亿美元。这一发展趋势与1990年代音频无线应用大变革时的情况类似。今天的许多系统都提供音频和数据服务,我们在文中将考察视频服务的兴起,以及新带来的计算需求挑战。

多媒体系统的要求

多媒体系统的要求高度依赖于最终应用。例如,视频点播(VOD)对延迟的要求相对较高,而视频会议则对延迟有精确的高要求。视频监控在延迟方面的要求则介于在这两个极端之间。实时多媒体系统可能需要也可能不需要实时编码。MPEG标准的开发主要着眼于降低解码器的复杂性,以提供成本经济的方案。相对而言,MPEG编码器的复杂程度是MPEG解码器的10倍左右。不需要实时效果的应用,如视频点播可以采用两步算法进行离线编码以获得最佳的效果。视频监控和视频会议则是需要实时编码的例子。在针对多媒体压缩的标准中,解码器功能规定了严格的标准兼容性规则,而编码器相对则自由多了。换句话来说,视频编码器只要能够生成符合标准的正确位流就可以,而兼容解码器则必须能够解释标准定义的特定"类"和"级"中所允许的任何正确位流。

图像数据库存储要求与压缩视频传输的要求绝缘不同。ISO JPEG工作组通常以压缩比率来衡量不同的压缩方案,而ISO MPEG通常采用固定位速率做为衡量参数。只要我们谈到多媒体通信,这些系统在数据传输过程中都需要通信信道能够保证固定的位速率。这导致一个问题,因为压缩比率是序列相关的,因此为了获得可接受的结果,必须在质量方面有所折衷。很明显,在编码器方面如果严格遵循固定位速率生成数据位流,那么就会导致帧之间质量的变化,有时可能会变得无法接受。这一问题可以通过下面的方法来减轻,在类编码器的后面指定一个缓冲存储区,这样就可允许编码器以可变数据速率填充缓冲区,而通信信道则可以以固定速率读取并清空缓冲区。这意味着多媒体压缩系统需要存储器。为了提高或增强质量所需要的额外预处理和后处理也提高了对存储器的需求。例如,在MPEG-4编码器的情况下,典型情况下需要3~10 MB的存储器,而解码器只需要1~3 MB。

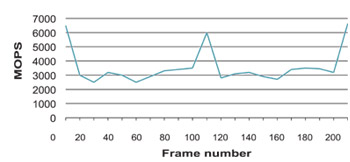

对任何系统来说,一个主要的要求是为达到实时操作而需要的每秒运算次数。对于多媒体压缩来说,这确实是一个需要量化的具有挑战性的数字。由于工作点很多,计算所需要的MOPS数值可能很大。图1 给出了几个MPEG-4"类"以及达到这些工作点所需要的相对MOPS数值,其中一级简单类归一化值为1。一个分辨率为640x480、每秒30帧的JPLEG2000视频监控应用视频流大约需要4200 MOPS,而分辨率为1024x1024、 每秒 60帧的医疗图像无失真码流在采用JPEG2000标准编码时则需要29000 MOPS。利用JPEG200 0标准的4096x2048分辨率24 帧每秒的数码相机需要93000 MOPS。使问题更复杂的是,在整个视频流运算过程中,所需要的MOPS数值并不是固定值,而是依赖于图像内容的。在图2中我们看到在视频序列的播放过程中,峰值MOPS数值是需要确定的关键要求。

图1 不同MPEG"类"编码所需要的计算MOPS要求

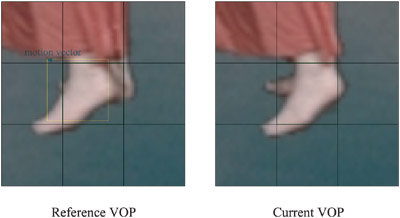

对于多媒体压缩来说,人们可能会问,到底哪些功能是计算密集的呢?信息理论的基础告诉我们,无损失压缩就是在信源编码过程中不影响图像集的数值。在现在的多媒体压缩编码解码器中,这是通过可变长度编码和算术编码实现的。在图像本身所提供的信息量之外则进入不相干信息处理领域,通常利用运算预测(Motion Estimation)算法来消除暂时冗余,通过离散余弦变换(DCT)或离散小波变换(DWT)进行能量压缩,对视频流中包含的高频项进行比例压缩。这两项都会影响到解码序列的质量,因为对于有损压缩来说,理想的图像重构是不可能的。对于MPEG编码,MOPS和运算图像预测算法以及结果的质量目标之间影响很大。运算图像预测需要从一个帧搜索下一个帧(图3)以找到空间元素的最小误差,从而来确定运动 向量。这一运动向量加上不同的数据被一起编码,这可大大提高压缩比、降低位速率。

图2 MOPS数值变化

图 3 暂时冗余和运动预测

在多媒体系统,多媒体接口也扮演了相当的角色。ANSI/SMPTE 259M-1997标准规定了如何通过视频同轴电缆串行传输数字视频内容。通常称为SDI的这一标准现在被广泛用来在电视演播室和视频生产中心通过原来用于传输模拟视频的视频同轴电缆来传输数字视频数据,数字音频被插入数字视频流的非活动部分。计算出的错误检测数据包(EDH)也被插入视频数据流中。然后,数字视频内容被编码、串行化并通过同轴电缆发送。在接收端,数据和时钟从串行位流中恢复出来,位流被解码、成帧和去串行化。最后,在对数字视频数据解码以前,对位流进行错误检测和分析。

多媒体解决方案

在今天成本敏感的环境中设计多媒体系统是一项颇具挑战性的任务。从技术的观点来看,芯片逻辑门密度不断提高可支持更复杂的算法。更多嵌入式功能也降低了系统设计师所面临的设计挑战。新的芯片集成努力也似乎可将最终设计的尺寸降到尽可能小。 要找到一个合适的解决方案需要理解计算、存储器和接口方面存在的各种选择。

多媒体处理对计算性能的要求从数千MPOS至数万MOPS不等。如果我们考察一下可用于完成计算功能的芯片解决方案,我们可以看到有通用处理器、DSP、媒体处理器、FPGA、SIC和ASSP。集成多媒体扩展功能的通用处理器可达到数百MOPS的性能,当应用中不需要太强的计算能力时,通用处理器提供了一个很好的解决方案。当多媒体仅是整个系统环境中需要提供的众多功能中的一项时,通用处理器非常具有吸引力。数字信号处理器可提供5000 MOPS左右的性能,应用范围更广,并且可很好地在嵌入式应用中工作。媒体处理器的计算能力更进一步,达到约2万MOPS,而很多嵌入式功能专门针对多媒体处理器而优化。此类功能的例子有芯片中做为硬件加速器而集成的嵌入式位处理器和特殊的MPEG功能。FPGA的计算性能可达到10万MOPS,并可处理高速接口。计算能力的提升源于分布式逻辑、MAC和本地存储器,可以根据特殊应用高效率地使用这些资源。通过在平台FPGA中引入嵌入式处理器(如PowerPC),代码可编程能力和硬件可编程能力都是可能的。ASIC可达到数十万MOPS的计算性能,并曾广泛用于嵌入式应用。但是,ASIC也有缺点,那就是ASIC需要极高的NRE成本,因此仅适用于大批量应用。ASSP专门针对一种特定应用,如果应用于其它应用中,则通常在质量方面会有所折扣。

多媒体应用对存储器的需求依据应用不同可能从数千字节到数M字节。大多数应用都可以按照需要存储的帧数来衡量。作为参考,720x480x24位的一帧NTSC数据需要341 KB的存储空间。如果仅需要存储少量帧的话,片上集成的存储器大概可以满足要求。高分辨率720行逐行扫描(1280x720x24)需要900 kb才能存储一帧数据,而 1080i (1080x1920x24)的一帧将需要2.025 MB的存储空间。大体上,一旦达到数兆字节的存储量,那么就需要外部存储器了。目前,外部存储器的流行选择是同步DRAM和ZBT存储器。ZBT存储器的优点是可交叉访问、存储器控制器简单,但容量较小,只有2~8MB,而且相应地,其成本也比DRAM要高。同步DRAM在读写间切换时有延迟,需要更复杂的存储器控制器。其容量为32~128MB,有双倍和四倍数据速率的产品型号,可以提高连续数据猝发读取时的存储器带宽。

多媒体应用设计工具

芯片逻辑门密 度的提高对于设计工具行业提出了困难的挑战。随着100万门的设计非常普通,而1000门的设计也已达到,工程师如何应付设计单块芯片上的一亿逻辑门系统这些样的设计复杂性?对于通用处理器和数字信号处理器来说,软件编程环境为设计人员提供了一个很好的环境,帮助他们利用所提供的计算能力。对于多媒体系统,问题变得更为复杂,因为缓存尺寸变得更大,而且还要满足更强的实时处理要求。我们期望多媒体扩展处理能力变得更为普遍,从而使设计人员从实现实时处理目标所需要的细节中解脱出来。额外的IP库对于减轻与设计复杂性相关的问题也扮演了一个关键的角色。媒体处理器的嵌入式功能在通用编程环境中的使用稍微困难一些。FPGA和ASIC的吸引力在于其计算能力提升了数个量级,这要归功于其并行机制。充分发挥其计算能力的关键在于能否拥有一个高效率的编程环境。C语言和逻辑设计工具的最新发展,以及几家供应商新发布的工具承诺在明年可解决这一问题。

在开发新的编码解码器时,C编程环境对于标准的应用是一个关键的出发点。在开发AVC编码解码器的过程中,参考软件为开发人员提供了解释编码解码器中每种技术相对参数的参照标准和方法。当一

种标准被接受时,这一参考软件扮演了一个有用的角色,可以为设计人员提供一个参考点。这意味着,通常设计的起点就是从理解参考软件以及相应的复杂性瓶颈开始的。特征描述工具也开始出现,这些工具可快速揭示出存储带宽和计算问题。

我们也看到,市场上也开始出现了针对特定领域应用的专用工具,它们可以提高多媒体系统设计的抽象水平。Mathworks 提供了一个大多数DSP设计人员非常熟悉的算法探索/开发环境。Xilinx System Generator for DSP就基于这一框架,提供了一种探索/研究算法、进行行为仿真并生成最终FPGA设计的方法。图4示意出了在Xilinx System Generator for DSP表达的一个边沿检测系统。这一仿真框架还可提供在仿真循环过程中通过硬件来加快仿真速度的可能。在针对特定领域的工具方面,更高层次的抽象使得更容易跟上芯片逻辑门密度增长的步伐。

结论

在本文中,我们讨论了多媒体通信以及目前多媒体行业所面临的问题。同时也讨论了多媒体系统的要求和处理需求,并探讨了可用来满足这些要求的器件。最后,我们指出多媒体设计工具需要不断提高抽象水平,才能为高效率地使用数百万系统门的芯片资源提供支持。

图4 Xilinx System Generator for DSP