现代无线通信系统中,越来越大的业务量与越来越少的频率资源之间的矛盾显著,而且以视频、数据为主的通信内容使得在分配信道资源时留给话音业务的资源非常有限,采用G.729A低速率的话音编码技术可降低编码速率,提高频率利用率。

ML7204专用语音处理器可提供多种速率的编解码功能,包括A律和U律2种不同的PCM和G.729A低速压缩话音编解码。该器件内置FIF0缓存器,具有合成语音质量高、抗误码性能好等特点,并在语音通信,特别是VoIP系统中应用广泛。基于8051构架的开源微处理器内核PicoBlaze配合FPGA解决常量编码可编程状态机(KCPSM)问题,可以使系统同时具备处理复杂控制和时序逻辑的能力。这里介绍了ML7204的基本性能和工作原理,微处理器内核PicoBlaze的开发流程及其使用方法,并且给出通过PicoBlaze配置、控制ML7204实现单路G.729A语音编解码的系统设计方案。

1 ML7204功能简介

ML7204具有如下特点:内置640字节FIF0,为数据收发提供缓存;支持ITU的G.711、G.729A等分组语音处理标准;回音抵消和抑制、静音检测和舒适噪音等提高分组语音处理性能;收、发增益控制;以数据、地址总线方式访问控制寄存器。

ML7204分组语音处理器件的接口是从硬件连接和功能两方面考虑,包括语音、PCM、中断、时钟、处理器等接口。其中,语音接口(Voice I/F)模拟话音信号的输入输出,内置可调增益放大器和A/D和D/A转换器;PCM接口(PCM I/F)用于非压缩语音信号的输入输出,为64 kb/s率或a率压扩的PCM信号;中断接口(INT I/F)提供异常状况的信号指示;时钟接口(CLK I/F)既可外置晶体,也可直接输入时钟信号,时钟频率12.288 MHz;处理器接口(MCU I/F)包括8位数据、地址总线以及读、写使能、片选信号,实现微处理器与ML7204的通信,并实现微处理器对ML7204的控制、以及ML7204的状态检测。ML7204有复位、初始化配置、运行3种工作模式,如图1所示。ML7204上电后,复位信号有效(PDNB=0)时,内核重启,则ML7204进入复位模式(Power Down State);初始化配置模式(Initial State)是当复位信号释放(PDNB=1)时,所有状态重置等待处理器配置。处理器通过修改控制寄存器完成器件的初始化配置;初始化完成后器件进入运行模式(OperationState),开始正常运行,此时通过设置PDNB或控制寄存器的软复位信号使ML7204重新进入复位模式等待初始化。

2 微处理器内核PicoBlaze简介

PicoBlaze的特点如下:Xilinx公司专为Virtex、Spartan系列FPGA和CoolRunner系列CPLD设计的嵌入式专用8位微处理器IP Core;占用逻辑资源少,只占96 slices(Sparta-3X(22S200E资源的5%):运行速度快,最高可达40 MI/s;指令集丰富,包括逻辑操作、输入,输出、算术运算等指令;开源、免费的编译器kcpsm3。

PicoBlaze微处理器接口从数据和控制两方面考虑,包括复位、时钟、读信号、写信号、数据输入、数据输出等接口。如图2所示。

复位接口(reset)是异步复位、高有效、清除PicoBlaze内核所有状态,但不清除程序代码;时钟接口(clk)是输入主时钟,最高速率35 MHz;地址总线接口(port_id[7:0])为PicoBlaze内核的地址总线,持续2个时钟节拍有效;数据总线接口(out_port[7:0])是PicoBlaze内核的数据总线,持续2个时钟节拍有效;读信号接口(read_strobe)是读脉冲信号,当该信号为高时,port_id[7:0]输出有效数据;写信号接口(write_strobe),写脉冲信号,当该信号为高时,port_id[7:O]输入有效数据。

3 系统硬件设计

图3为基于PicoBlaze软核处理器和ML7204编解码器的单路低速话音编解码系统的框图。

该系统主要由话音信号处理、系统逻辑控制、传输复分接、时钟处理4个单元组成。其中,话音信号处理单元主要由ML7204和简单外围器件组成,完成模拟话音信号与G.729A压缩编码信号之间的相互转换;系统逻辑控制单元由PicoBlaze内核组成,完成与ML7204的数据传输;传输复分接单元由FPGA片内逻辑单元组成,完成拆、组帧及并、串转换。时钟处理单元为ML7204提供高稳定时钟信号。

由话机模拟电路输出的模拟话音信号经话音信号处理单元,实现PCM编码、G.729A压缩编码,再通过并行MCU I/F接口输出速率为8 kHz的G.729A压缩编码数据,系统逻辑控制单元读取压缩编码数据,并送往传输复分接单元,进行组帧、并串转换,最终输出成帧的串行码流。相应地成帧的串行码流先进入传输复分接单元进行帧同步检测,读取真正的话音数据,串并转换后,再传输至系统逻辑控制单元,由PicoBl-aze内核将并行话音数据发送至话音信号处理单元,话音数据经解压缩、PCM解码,恢复模拟话音信号。

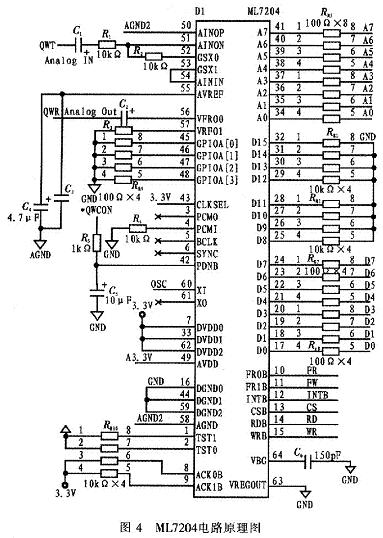

ML7204的数据传输采用总线方式,即A[7:0]、D[7:0]分别是8位数据、地址总线;FROB、FRlB、INTB、CSB、RDB、WRB分别为读使能、写使能、中断、片选、读信号、写信号。ML7204有10 ms帧和20 ms帧两种数据帧格式,这里采用10 ms帧格式。ML7204以10 ms为周期全双工并行工作。每隔10 ms,ML7204拉低读使能信号FROB,表示已经准备好完整的一帧数据,外部PicoBlaze微处理器通过连续10次拉低片选信号CSB、读信号RDB读出一帧数据。相应,每隔10 ms,ML7204拉低写使能信号FRlB,表示解码处理新的一帧数据,外部PicoBlaze微处理器可以通过连续10次拉低片选信号CSB、写信号WRB写入一帧数据。图4是ML7204电路原理图。

4 系统软件设计

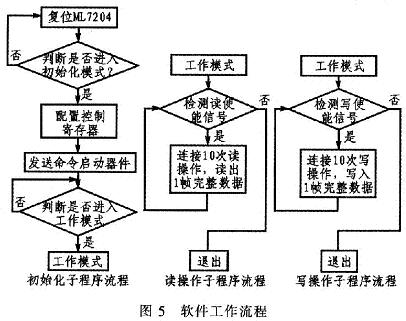

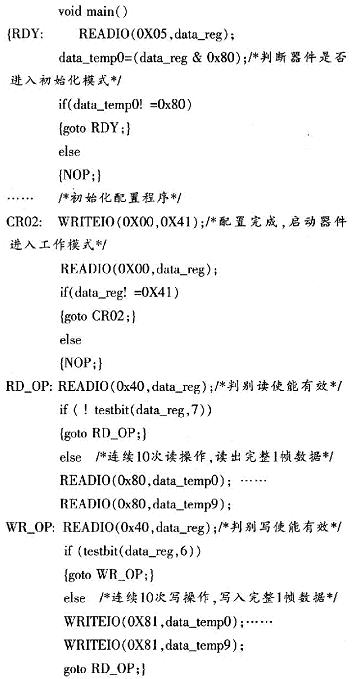

该系统软件主要是对ML7204初始化配置、工作状态控制.ML7204的配置方式是修改控制寄存器。工作时,FPGA内嵌PicoBlaze内核首先对ML7204复位,复位成功后,PicoBlaze内核通过MCU I/F接口修改控制寄存器,设置其工作方式,包括语音编码方式、语音信号幅度、数据帧长度等,最后FPGA内部逻辑处理单元配合PicoBlaze内核完成分组语音数据的读写及传输。ML7204共有48个控制寄存器CR0~CR47,分别对应于地址00H~2FH,每个控制寄存器有8 bit数据,分别标识不同的配置选项。保留地址80H、81H分别对应分组话音编解码数据的读、写地址。图5为软件工作流程。

以下给出软件程序的核心代码:

5 结束语

ML7204是一个功能强大的语音信号处理器,可提供多种速率语音编解码功能,操作方便。PicoBlaze是一个典型的8位软核处理器,便于在各种FPGA上实现,设计灵活。本文采用PicoBlaze与ML7204协同工作。构建低速率语音通信的编解码系统。相比传统的语音编解码系统设计方案,此方案无需单独微处理器、Flash、SDRAM、PCM编解码等器件,只需单片ML7204和单片小容量FPGA即可完成全部功能,设计简单、成本低廉、合成语音质量高,能有效提高带宽利用率,在频带有限的无线通信系统中具有较大优势。

电路设计时需特别注意:考虑模拟信号与数字信号的隔离,应减少数字噪声对模拟话音的干扰,减少背景噪声。PicoBlaze微处理器初始化配置ML7204的控制寄存器时会出现错误。为避免错误配置,应在每次修改控制寄存器后读回此控制寄存器的值,并判别是否与预期一致。若一致则配置下一个控制寄存器,否则继续配置,直到一致为止。