ADSP-21535 Blackfin的Mem DMA高速通信

2008-08-27

作者:杨 波 邢克飞 杨 俊 王

摘 要: 针对ADSP-21535 Blackfin 的Mem DMA 高速通信" title="高速通信">高速通信中的关键技术进行了讨论,分析了系统的内存管理" title="内存管理">内存管理,对DMA的相关寄存器的配置进行了详细讲解,并给出了具体实例。对多种内存之间的DMA列出了实际的指标评测,为该系列DSP工程应用的高速通信设计提供了重要参考。

关键词: ADSP-21535 Blackfin Mem DMA

ADSP-21535 Blackfin 是美国AD公司和Intel 公司于2001年底联合推出的一款定点DSP, RISC指令结构,运作高效,具有十分优异的性能。该DSP具有300MHz的主频,2个40bit的MAC(乘加器)和2个32bit的ALU(算术逻辑单元),4个8bit的视频处理单元,16个地址寻址单元。该DSP内部集成了308KB的RAM,并具有丰富的外部接口,如PCI、USB、SPI、同步和异步串口等。同时,芯片内部设计了看门狗和多种定时器,充分满足软件工程稳定性的设计要求。值得一提的是,21535可以动态地控制电压输入,调整运行频率,减少芯片功耗,十分适用于移动产品的设计。

2002年底,AD公司在中国开始大规模推广Blackfin系列的DSP,21535成为该系列的旗舰产品。由于该DSP推出时间不长,相关文献几乎没有报道;而且,在许多接口性能方面,AD公司也没有对其给出准确的指标。根据通常的设计经验可知,新产品通常在某些方面没有达到设计要求。笔者所设计的高速通信板数据交换速度必须达20M Word/s以上,因此对该DSP的高速通信必须进行准确仔细的评估和设计。

ADSP-21535的内存访问支持I/O方式、内存映射和多种DMA方式,其中Mem DMA(Memory to memory DMA)方式是最快的一种并行通信方式。因此,笔者在设计时选择了Mem DMA作为高速通信方式。由于21535支持多种内存,因此在设计Mem DMA时,必须对21535的内存管理有一个详细的了解。

1 ADSP-21535的内存管理

21535的内存管理十分强大。它把存储器视为一个统一的4GB的地址空间,使用32位地址。所有的资源,包括内部存储器、外部存储器、PCI地址空间和I/O控制寄存器,都具有独立的地址空间。此地址空间的各部分存储器按照分级结构排列,以提供较高的性能价格比。一些快速、低延迟的存储器(如L1)的位置接近处理器核心,而低成本低性能的存储器远离核心。 芯片内部的308KB RAM中,其中L1(一级缓存)52KB,L2(二级缓存)256KB;外部地址访问空间可以高达768MB,通过EBIU(External Bus Interface Unit,外部总线接口单元)进行管理。EBIU支持多种内存,如SDRAM、SRAM、ROM、EPROM、FLASH、FIFO等。内存地址的具体配置空间如图1所示。

L1作为DSP的一级缓存,可以与DSP的内核一样,运行在300Mbps的高速上。它分为三部分:16KB的Instruction Ram(指令存储器)、,两块16KB的Data Ram(数据存储器)、4KB的Scratchpad Ram(中间结果缓存)。指令存储器既可以作为SRAM,也可以配置为4路联合设置的Cache。数据存储器能够配置成双路联合设置的Cache或者SRAM;中间结果缓存只能作为SRAM使用。指令缓存和数据缓存都可以通过DMA方式灌入数据,但是对于中间结果缓存这种方式不能使用。

L2作为DSP的二级缓存,是一个统一的指令和数据存储器,能够根据系统设计要求同时存放代码和数据。L2具有DSP核心同样的带宽,但是延迟时间较长,访问L2单个独立的地址时系统需要经过7个周期的延时,这时它的访问速度在42.8Mbps左右。所以如果程序比较大,必须在L2中编写程序时,通常将L1配置为L2的Cache,这样,速度可以大大加快。

21535支持的片外存储器种类很多,值得一提的是它的SDRAM控制器。21535集成的SDRAM控制器能够以fSCLK(系统时钟,为核心时钟的若干分频)的速度,与多达4个Bank的工业标准SDRAM或者DIMM接口。每个Bank可以配置为16MB~128MB的存储器,符合PC133 SDRAM的标准。

存储器的DMA控制器提供高带宽的数据传输能力,它能够在内部L1/L2存储器和外部存储器(包括PCI存储空间)之间执行代码或者数据的块传输。

2 DMA寄存器的配置

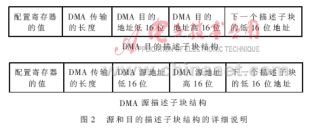

为了描述Mem DMA序列,DMA控制器使用一套名为描述子块" title="子块">子块(Descriptor)的参数。当需要后继的DMA序列时,这些描述子块被链接起来。这样,一个DMA序列完成时能够自动初始化下一个序列,并将其启动。如果不需启动下一个序列,只要将其指向一个内容为0的地址空间即可。如果下一次链接指向原描述子块,则DMA完成后暂停。为访问整个ADSP-21535的地址空间,源地址和目的地址描述子块采用了全32位地址的基指针。两个描述子块均为5个字的连续空间,需要注意的是该连续空间必须定义在L2范围内。描述子块内包含的内容如图2所示。

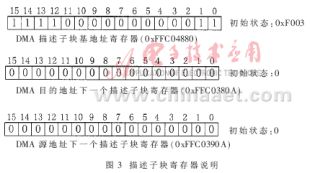

Mem DMA规定,描述子块所在的首地址必须传入相关的寄存器。描述子块首地址的高16位装入DMA_DBP寄存器(DMA Descriptor Base Pointer Register,DMA描述子块基地址寄存器)内。由于该寄存器严格限定必须在0xF000~0xF003,这就限定了源和目的地址描述子块只能定义在L2存储器内,并且高16位地址相同。

描述子块首地址的低16位放在两个寄存器中,源地址描述子块低16位装入MDS_DND寄存器(Source Memory DMA Next Descriptor Pointer Register,DMA源地址下一个描述子块寄存器),而目的地址描述子块低16位装入MDD_DND寄存器(Destination Memory DMA Next Descriptor Pointer Register,DMA目的地址下一个描述子块寄存器)。其说明如图3所示。

在描述子块的地址传入相应寄存器后,后面的四项先配置,然后设置第一项。也就是对管理DMA启动参数的寄存器进行参数配置。两个配置寄存器" title="配置寄存器">配置寄存器的详细内容如图4所示。例如当目的地址寄存器为0x8003,源地址寄存器为0x8001时,传输的数据总长=DMA传输的长度×字。需要注意的是,虽然此时传输以16位(字长)传输,但DMA的带宽是32位,剩下的带宽资源将被浪费。8位传输时,带宽资源利用率更低。

下面,以一个具体的32位DMA例子说明上面的描述子块和多个寄存器的使用方法。

3 32位DMA的例程

R0.H = 0x8009; //DMA源配置字,设置为32位传输

R0.L = 0x800; //DMA长度

R1.L = 0x2000; //DMA源地址低16位

R1.H = 0xf000; //DMA源地址高16位,这里指向L2

R2.L = RAM_READ; //DMA源描述子块首地址低十六位,DMA读

R2.H = 0x800b; //DMA目的配置字,设置为32位传输

R3.L =0x0000; //DMA目的地址低16位

R3.H =0xff90; //DMA目的地址高16位,这里指向L1数据存储器-Bank B

R4.L = RAM_WRITE; //DMA目的描述子块首地址低十六位,DMA写

P0.L = RAM_READ; //将32位的源描述子块的地址载入P0

P0.H = RAM_READ;

P1.L = RAM_WRITE; //将32位的目的描述子块的地址载入P1

P1.H = RAM_WRITE;

W[P0+0x2] = R0; //将DMA长度写入源描述块第二个字中

[P0+0x4] = R1; //将DMA的32位源起始地址写入源描述块第三第四个字中

W[P0+0x8] = R2.L; //将下一个源描述子块的地址写入源描述块第五个字中

W[P1+0x2] = R0; //将DMA长度写入目的描述块第二个字中

[P1+0x4] = R3; //将DMA的32位目的起始地址写入目的描述块第三第四个字中

W[P1+0x8] = R4; //将下一个目的描述子块的地址写入目的描述块第五个字中

W[P0] = R0.H; //将DMA源配置字写入源描述块第一个" title="第一个">第一个字中

W[P1] = R2.H; //将DMA目的配置字写入目的描述块第一个字中

R6 = P0; //将P0的值同时存在R6内

P2.L = 0x390A; //将DMA源描述子块配置寄存器的地址传给P2

P2.H = 0xFFC0;

W[P2] = R6.L; //将DMA源描述子块所在地址的低16位传给P2指向的地方

P3.L = 0x4880; //将描述子块基地址寄存器的地址传给P3

P3.H = 0xFFC0;

W[P3] = R6.H; //将DMA源描述子块所在地址的高16位传给基地址寄存器

P4.L = 0x380A;

P4.H = 0xFFC0; //将DMA目的描述子块配置寄存器的地址传给P4

R6 = P1; //将P1的值转存到R6

W[P4] = R6.L; //将目的描述子块所在地址的低16位传给配置目的地址寄存器

P5.L = 0x3902

P5.H = 0xFFC0; //将DMA源地址配置寄存器所在地址传给P5

R6 = W[P5];

BITSET(R6,0); //设置R6的最低位为1,表示准备启动读DMA

I0.L = 0x3802;

I0.H = 0xFFC0; //将DMA目的地址配置寄存器的地址传给I0

R7.L = W[I0];

BITSET(R7,0); //设置R7的最低位为1,表示准备启动写DMA

W[P5] = R6; //将R6和R7的低16位写入两个配置寄存器中,真正启动DMA

W[I0] = R7.L;

DMA_WAIT: //等待DMA结束

R6 = W[P1]; //根据写描述子块第一个字的最高位判断描述子块的所有权

cc = bittst(R6,15);

IF cc JUMP DMA_WAIT; //如果为1,表示还在DMA状态,继续判断,等待

RTS;

.align 4; //在L2空间范围内定义两个描述子块,要求4个字节对齐

.BYTE2 RAM_READ[5];

.align 4;

.BYTE2 RAM_WRITE[5];

值得注意的是,在上述DMA例程中,笔者使用了查询等待方式,但中间完全可以插入其他指令,例如DSP还可以同时作双乘加和两次32位取数。只要不访问正在DMA读写的地址区域,没有任何影响。这意味着,在系统DMA的同时,DSP可以同时进行其他操作,这一点对于提高DSP的效率至关重要。

4 各种内存空间的DMA访问指标测试及分析

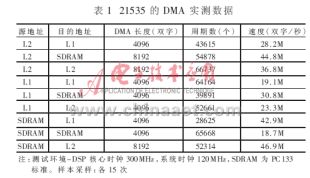

根据以上配置,笔者对ADSP-21535的DMA性能进行了比较详尽的测试。测试数据如表1所示。

从表1中的实测数据可以看出,DMA的速度均在18.7M双字/秒以上,最高速度达46.9M双字/秒,可以满足工程中高速采集的需要。从表中数据可以得出以下结论:

(1)DMA双向速度不对称,将源地址和目的地址交换后,速度会发生变化;

(2)低速向高速区域传输时,要比反向传输快;

(3)同类区域DMA一般比区域之间DMA要慢。如L1 DMA到L1,比L1 DMA到L2和SDRAM都要慢一些。其它区域也有类似现象。

(4)高速区域DMA速度并不一定快,如L1区域DMA速度总体表现反而最低。

参考文献

1 AD公司. ADSP-21535 Blackfin DSP Hardware Reference. 2002

2 AD公司. Blackfin DSP Instruction Set Reference. 2002