随着微机应用和计算机网络的发展,计算机与外界之间的信息交换变得越来越重要,为了保证串行通信的正常进行,提高串行通信的效率和CPU的利用率,在微机系统中采用专用的大规模集成电路来完成这些工作,这就是串行通信接口。通用异步接收发送器UART(Universal asynchronousreceiver/transmitter)主要用于控制设备之间的串行通信。广泛应用于调制解调器Modem、手持工业设备、条形码阅读器、测试设备、消费产品与计算机PC、微处理器以及小型通信网络之间的通信等。在SOC设计中,异步串行通信接口已成为不可缺少的一部分,它的性能优劣将直接影响相应电子系统的性能和指标。

1 UART原理

串行通信是指外部设备和计算机间使用一根数据线(另外需要地线,可能还需要控制线)进行数据传输的方式。数据在一根数据线上一位一位传输,每一位数据都占据一个固定的时间长度。与并行通信方式相比,串行通信方式的传输速度较慢,但这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,因此得到了广泛的应用。

基本的UART只需要发送和接收两条数据线就可以完成数据的全双工通信,其基本功能是在发送端将控制器通过总线传过来的并行数据,以设定的格式,设定的频率串行地传输出去,并同时在接收端将串行接收到的数据,转换成相应的并行数据发送出去。UART的基本帧格式如图1所示。其中,起始位总是逻辑O状态,停止位总是逻辑l状态,其持续时间可选为1位、1.5位或2位,其数据位可为5、6、7、8位,校验位可根据需要选择奇校验位,偶校验位或无校验位。

2 UART的设计

现今复杂的数字系统的设计往往采用自顶向下的设计方案,利用层次化结构化的方法,将一个设计方案划分为若干模块,在不同层次的模块都可以进行仿真,可以很方便地查看某一层次的代码以改正仿真时发现错误。在本设计中UART主要由波特率发生器、接收模块、发送模块3部分组成,并具有l位停止位和无校验位。波特率发生器实现波特率的变换,利用外部时钟信号产生一个所需波特率16倍的波特率时钟,用来控制UART的接收与发送。接收模块是用于接收串行信号,并将其转化为并行数据;而发送模块则将准备输出的并行数据按照UART的帧格式转化为串行数据输出。图2为UART结构图。

2.1 波特率发生器

波特率表示的是每秒钟传送的二进制数据的位数,即单位时间内传送的信息量。在串行异步传送中,常用到的波特率为1 200、2 400、4 800、9 600、19 200等。波特率发生器实际上是一个分频器,主要是产生和。RS-232通信所采用的波特率同步的时钟。由于串行数据帧与接收数据时钟是异步的,所以存 UART的接收端在什么时刻将数据移入寄存器,怎样选择可靠的采样点是非常关键的。一般采用高速时钟对串行数据采样是非常有效的方法。在实际设计中,一般最大选择16倍于波特率的时钟频率。实现波特率时钟的基本思路就是设计一个计数器,该计数器工作在速度很高的系统时钟下,通过总线写入不同的数值到波特率发生器保持寄存器中,然后用计数器的方式生成所需要的各种波特率就能得到所需的波特率时钟,仿真如图3所示。

2.2 接收模块

接收模块是整个UART的设计的重点,其主要功能是检测数据的起始位,并对接收的数据进行串并转换,并将接收好的数据储存等待微机处理。由于串行数据帧与接收数据时钟是异步的,接收功能实现的关键是接收器与每个接收字符同步。要保证异步通信的双方准确无误地交换信息,必须有效控制采集通信线路上的电平信号的时机。由异步串行通信的特点可知,接收同步是通过低电平起始位实现的。而为了保证采样的正确性,采样在数据位的中间进行,并且接收单元采样数据的频率与发送单元发送数据的频率相同,是波特率时钟周期的16倍,这样可以有效地降低由于时钟不匹配而导致的误采样。接收模块的设计主要由状态机实现其核心功能,采用独热编码方式,虽然独热编码多用了两个触发器,但所用组合电路可节省一些,使电路的速度和可靠性有显著提高。控制接收器的起始/停止位检测,接收数据的计数,移位寄存的功能。状态机分为5个状态,分别为:IDEL,CENTER,WAIT,SAMPLE,STOP。状态转换图如图4所示。

1)IDLE状态 系统被复位后,接收状态机进入IDLE状态,等待起始位到来,输入数据在空闲时保持为1,当输入由“l”跳变为“0”时,状态机跳转到CENTER状态。

2)CENTER状态 启动起始位检测电路,为排除噪声干扰,状态机等待8个脉冲,如果数据线上仍为低电平,则状态机跳转到WAIT状态,并启动采样电路。如果是噪声干扰,则转入IDLE态。

3)WAIT状态 状态机WAIT状态,判断数据接收是否完毕,若未完成采样,则转入SAMPLE状态进行数据位的采样检测,同时启动位计数器,用来控制数据接收的位数。无论停止位是几位,状态机只对停止位作一次采样。接收完毕,转入STOP状态。

4)SAMPLE状态 在此状态对串口输入数据进行采样,每次采样均位于数据位的中心。并每接收完一位数据,状态机转入WAIT状态。

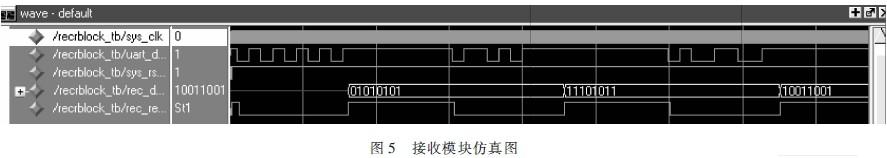

5)STOP状态 接收停止位,完成一个数据帧的接收,并将rec_ready置为1,表明收据接收完毕,待微机读取。其仿真结果如图5所示。

2.3 发送模块

发送模块的设计相对简单,其功能是将要发送的并行数据转换成串行数据,并且在输出的串行数据流中加入起始位和停止位。发送器首先将要发送的8位数据寄存,并在最低位后添加起始位‘0’,在最高位前添加停止位‘l’,组成10位要发送的数据,然后根据UART内核模块的计数值将相应的数据送入移位寄存器输入端。UART内核模块输出的计数值是从0依次计到9,即先将要发送数据的最低位送入移位寄存器。仿真结果如图6所示。

2.4 UART各个模块的整合

在各模块功能实现的基础上,把它们有机地整合在一起,使波特率发生器能够按照UART通讯的要求正常工作,接收模块和发送模块能够根据各自的复位信号使整合模块具有发送或接收功能。仿真结果如图7所示。

3 结束语

本文介绍了基于Verilog HDL设计的UART模块,采样点选择可靠,其可以准确判断接收数据的起始,接收器与接收数据实现同步,串行数据能被准确接收,并通过在ModelSim下的仿真,可下载至可编程逻辑器件中实现UART功能。