摘要:低功耗是嵌入式系统的发展趋势,也是便携式嵌入式设备设计中要解决的关键问题之一。对影响嵌入式系统功耗的因素进行了分析,指出了降低系统功耗的途径,从硬件设计和软件设计两个方面阐述了超低功耗嵌入式系统设计的技巧。

关键词:超低功耗;嵌入式系统;硬件设计;软件设计

无论是在军事还是在商业上的应用,便携式嵌入式系统一般是由可充电电池来供电的,因此,采用有效的节能技巧来改进系统的软硬件设计,降低系统的功耗以增加电池供电设备的使用时间,是便携式嵌入式系统设计中需要研究和解决的关键问题。

1 影响功耗的因素

1.1 集成电路功耗

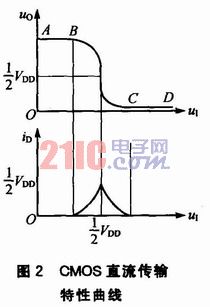

CMOS倒相器在集成电路分析中具有非常重要的意义,常用它来进行集成电路延迟时间和功耗的分析。CMOS倒相器如图1所示,图2是倒相器的直流传输特性曲线。

若电路处在静态(不发生状态翻转)并忽略漏电流的前提下,反相器的功耗几乎为零,如图2中的AB段和CD段。当电路发生状态翻转时,N管和P管具有同时导通的一段时间,此时从电源通过2个管子流向地的电流iD达到一个很高的峰值,如图2对应于BC段的电流。很大的电流意味着较高的功率消耗和热能的损失,这在时钟频率较高时尤为突出。时钟速度越高意味着每秒钟状态的切换次数就越多,也意味着更多的电能损耗。除此之外,在工作时还存在着静态漏电功耗,下面对这2类功耗分别进行分析。

1.1.1 动态功耗

CMOS倒相器从一种稳定工作状态突然转变到另一种稳定状态的过程中,将产生附加的功耗,称之为动态功耗。这一功耗是由2部分组成的,一部分是瞬时导通功耗PT,另一部分是对负载电容充放电所消耗的功率PC,其表达式为:

![]()

式(1)中,VDD为电源电压;ITC为2个管同时导通所产生的瞬时电流,不是固定的数值,如图2所示;a为活动因子,表示电容充放电的平均次数相对于开关频率的比值;CL为进行充放电的等效负载电容,包括栅电容、节点电容、互连电容等;f为开关频率,即电路的工作频率。

1.1.2 静态漏电功耗

静态漏电功耗是由亚阈值电流和反向偏压电流造成的。在集成电路中,动态功耗是整个CMOS集成电路功耗的主要组成部分,一般约占电路总功耗的90%以上,静态漏电功耗占电路总功耗的1%以下,因而在大多数情况下可以忽略。

1.2 其他功耗

①纯电阻元件上消耗的功率。电阻为耗能元件,只要电路中使用电阻,就存在着能量消耗。

②有源开关器件在状态转换时,电流和电压比较大,将引起功率消耗。

③非理想元件由于等效电阻的存在而消耗的功率。如电路中的储能元件电感和电容,理想情况下它们是不消耗能量的,但是实际使用的电感和电容都存在着等效串联电阻(ESR),就意味着能量的消耗。

④印制电路板中的走线上消耗的功率,如电源线由于电阻的存在会造成电能的损耗,实际中地线上也存在着电流的流动。由于导线阻抗的存在,串联单点接地的不同接地点之间会存在着电位差,因此在这些地线上也存在着能量的消耗。

2 降低系统功耗的途径

①降低集成电路的动态功耗。根据式(1)可知,要降低集成电路的动态功耗,途径有:a.降低活动因子,也就是降低电容充放电的平均次数。b.降低电源电压。因为动态功耗与电压的平方成正比,瞬时导通功耗与电压成正比,因此在满足电路速度的前提之下,降低电源电压是降低电路功耗的最有效的办法。c.降低负载电容。为了减小负载电容,在工艺方面可以选择小的器件,物理实现时减小连线的长度。d.降低开关频率,在式(1)中,电路的功耗与工作频率成正比,因此降低时钟频率可以直接降低动态功耗。

②尽可能选用静态功耗小的CMOS集成芯片,以降低系统的静态漏电功耗。

③尽可能地减少纯电阻的使用。纯电阻是耗能元件,电能直接转化为热能消耗掉了,所以要尽可能地避免电阻的使用。

④减少有源开关器件的使用。有源开关器件(如晶体管)在状态转换期间有比较大的电流消耗,减少这类器件的使用有助于减小功耗。

3 设计技巧

3.1 硬件方面

在器件选择上,要尽量实现全CMOS化的硬件设计。在设计超低功耗系统时,要对电源电压、时钟频率以及静态功耗进行控制,并遵循系统硬件设计的4项基本原则:电压能低就不高,频率能慢就不快,系统能静(态)就不动(态),电源能断就不通。

3.1.1 微处理器选择

随着低功耗系统需求的增加,很多单片机厂商都推出了自己的低功耗产品,如Philips公司的P8XLPC系列,TI公司的MSP430系列,Micro-chip公司的PIC单片机以及NXP公司的ARM Cortex-M0系列。如果处理器本身具有超低功耗特性,首先必须能在低电压和低频率工作,其次还要看单片机自身的特性,看是否是面向超低功耗应用而设计的单片机,需要对处理器的工作模式、工作电流、休眠电流、掉电电流作详细的统计。

Microchip公司采用nanoWatt XLP(eXtreme Low Power)极低功耗技术的MCU的典型电流消耗为:掉电电流小于100 nA;看门狗电流消耗小于800 nA;实时时钟和日历电流消耗小于800 nA。该公司的PIC24F16KA系列的MCU,典型休眠电流可以低至20 nA,实时时钟电流490 nA,看门狗定时器电流370 nA。该系列的MCU可使应用连续运行20年以上而无需更换电池。

NXP公司采用ARM Cortex-M0内核的LPCllxx系列32位处理器的能耗仅为85μW/MHz,此系列处理器的功耗统计如表1和表2所列。

3.1.2 外围集成电路

与TTL数字集成电路相比,CMOS数字集成电路在低功耗特性上具有无可比拟的优越性能。在存储容量需求较小的条件下,采用FRAM代替一般的Flash或E2PROM,将会节省很多电能,因为FRAM的写入功耗是Flash和E2PROM的1/1 000~1/100 000。

3.1.3 低电压供电

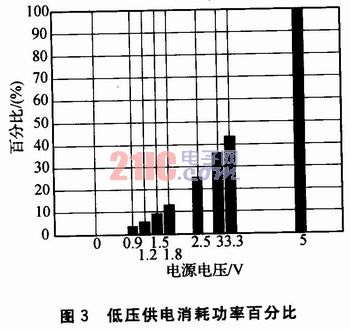

目前许多芯片的电源电压范围都比较宽,系统的功耗和系统的供电电压存在着一定的函数关系。对于纯电阻电路,功耗为P=V2/R;对于容性负载电路,动态功耗为,见式(1)。从以上2式可以看出,系统的功耗与系统供电电压的平方成正比。当供电电压由5 V降到3.3 V时,功耗将减少50%以上;当电压降到1.8 V时,功耗将减少80%以上,如图3所示。

3.1.4 分区供电

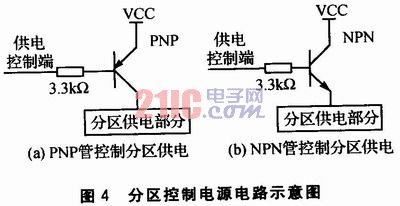

分区供电就是要控制电源供电部分,需要对电源进行分割,使系统功能模块的电源供电相对独立,同时实现其可控设计,便于独立供电和动态管理;在闲置时利用开关控制各个部分的关断,以节省电能。在系统休眠或掉电工作时关掉外围电路的电源,仅仅保留CPU和定时器电路的电源。分区控制电源电路示意图如图4所示。

图4中的晶体管用作电源开关,控制电源VCC向分区供电部分供电,供电控制端接到处理器的输出引脚上。对于图4(a)中的PNP管,高电平切断分区供电部分的电源,低电平使PNP晶体管导通,此时VCC向分区供电部分供电;对于图4(b)中的NPN管,供电情形则相反。

3.1.5 低频工作方式

低功耗微处理器中几乎全部采用CMOS器件,而CMOS集成电路的结构决定了它的静态功耗几乎为零,仅在逻辑状态发生翻转的过程中电路中有电流流过。所以它的动态功耗和它的逻辑转换频率成正比,和电路的逻辑状态转换时间成正比。所以CMOS集成电路从降低功耗的角度上来说应当快速转换,低频工作。

当程序在Flash中运行,VDD=3.3 V时,LPCllxx处理器功耗如表2所列。

3.1.6 电源转换芯片选择

手持设备一般是由电池供电,为获得较长的电池使用时间,一般采用DC/DC开关电源或LDO(Low Drop Outregulatot,低压差线性稳压器)。在价格允许的前提下,最好选择那些效率高、静态电流小,并且有使能端的芯片。效率高是为了减少电池能量在转化的过程中造成的损失。静态电流小可以减小芯片在待机状态的漏电流功耗。选择具有使能端的芯片可以利用微处理器进行关断控制,有利于独立供电支路功耗的管理。凌力尔特公司的DC/DC芯片LTC3417具有高达95%的效率和低于1μA的静态电流,已经在作者的有源手持机项目中得到了应用,取得

了显著的低功耗效果。

3.1.7 I/O引脚供电

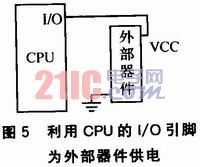

可以直接利用嵌入式微处理器的I/0引脚为外部设备提供电源,如图5所示,只要这些I/O接口的驱动能力足以驱动外部设备。

3.1.8 MCU时钟

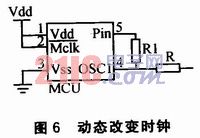

单片机的工作频率和功耗的关系很大,频率越高功耗越大。处理器动态改变CPU时钟的具体做法是:在CPU等事件发生时,引脚输出低电平,增大电阻将会降低内部的时钟的频率;当需要处理事务时,输出高电平减小电阻,提高时钟频率。实现这一技术的方法如图6所示。当CPU处于等待状态下可以将I/O引脚输出低电平,此时内部时钟频率降低;当CPU需要处理事务的时候,通过将I/O引脚设定为输出高电平,电阻Rl的加入将提高时钟频率。

3.1.9 未用引脚

处理好处理器和CMOS芯片未用的输入引脚。若未用的处理器引脚不加以处理,很容易造成电荷积累。根据电量与电容C和电压U的关系Q=C·U可知,当电荷的累积Q与电容C可比的情况下,就会产生影响引脚电平状态的U,这个电平会随着电荷的累积而导致数字逻辑状态在“O”和“1”之间变化,当输入引脚电平处于O、1之间的过渡区时,会使电路中反相器的P管和N管都处于导通状态,导致功耗大大增加。

CMOS电路未用的引脚,一般采取加上拉电阻(1~10 kΩ)的方法处理,为节能起见,阻值要取大一些。

3.1.10 局部电路的节电技巧

①采用RC振荡器比晶体振荡器或锁相环更省电。

②接口电平要尽量匹配,以减少电平匹配电路带来的额外功耗。

③在保证驱动能力的前提下,电路中应尽可能采用阻值较大的上拉/下拉电阻,以减小在电阻上的能量消耗。

④如果允许,适当降低外部驱动引脚的电压。

⑤选择合适的驱动接口参数,以减小缓冲器的使用量。

⑥少用驱动电阻或双极晶体管,这些器件需维持恒定的电流,从而增加了电能消耗。

3.2 软件方面

3.2.1 避免查询方式和延时

A/D转换器在采集少量的数据时,MCU读取A/D转换数据的方式有2种:查询方式和中断方式。查询方式和中断方式的低功耗特性相差甚远:使用中断方式,MCU可以什么都不做,甚至可以进入待机或者停止模式;而查询方式下,MCU必须不停地读取I/O端口寄存器,消耗很多额外的功耗。

如果系统的定时器资源充裕,在需要定时的场合,最好采用硬件定时器,当定时器到了定时时间后,向MCU发出中断请求信号,这样可以减少MCU的工作时间,进而可以节省功耗。

3.2.2 运行管理

①动态电源管理(Dynamic Power Management,DPM)。有选择地把闲置的系统部分置于低功耗状态,从而有效地利用电能。充分利用处理器和外围电路的低功耗工作模式,当系统和外围电路不工作的时候,软件设计时应该使处理器和外围电路及时地进入待机或者休眠模式。可选择关断CPU时钟或系统时钟,对时钟的控制要做到忙时多用、闲时少用、不用关断。

②间歇性使用电路的控制。对于间歇性使用的外围电路,在软件控制中通过片选使能端控制其工作时间。在某些功能没有使用到时,适时地将嵌入式处理内部电路的全部或部分关断,或者进入睡眠或待机状态,同时关闭不用的外围接口电路,如串口、ADC/DAC、I2C、SPI、PWM等电路。

③未用I/0引脚的软件处理。对于未用的处理器I/O引脚,软件中也要进行初始化,若不进行初始化,将有可能会增加单片机的漏电流,最好将其设置为输入或者输出,且接一个固定的电平。

3.2.3 用宏代替子程序

宏是在编译器预处理阶段进行替代,而子程序调用中MCU需要进行现场保护。进入子程序之前要将当前的MCU寄存器压入RAM中分配的栈,在离开的时候,要把栈中的内容弹出来恢复MCU的寄存器,这样至少会带来2次对RAM的操作。尽管用宏增加了代码的长度,但是加快了代码执行的速度,对于目前很多MCU来说,代码的Flash空间根本不是大问题,这种做法将会在一定程度上降低系统功耗。

3.2.4 采用高效率算法

①用查表的方法代替实时的计算。特别是在没有硬件浮点处理单元的MCU进行浮点处理的时候,直接用MCU进行浮点处理将会消耗大量的时间。如果将一些运算的结果事先计算好,存储在程序存储器的代码段中,在需要某个数据时用查表的办法把数据取出来,可以减少MCU的运算量,有效地降低MCU的功耗。这种处理方法在离散余弦变换和A/D数据采集中能够带来可观的效率提升。

②用移位运算代替乘除法运算。用MCU计算乘除法也是非常耗时的事情,如果尽可能避免直接的乘除运算,而采用左移和右移的办法来实现,将会减少运算时间,进而节省功耗。如要进行y=x·15的运算,可以转化为x<<4-x。对于特殊的除法,要采取右移的办法。如3000÷256可以直接转化为3 000>>8。当然,除法的移位计算只能针对除数比较特殊的时候。

③采用快速算法。在搜索算法中,使用二分搜索算法和分段查找算法的效率是不同的。理论上可以估算,在1 024个测量值的查找中,二分搜索最坏情况下10次可以查找到结果,顺序搜索最坏可能需要1 024次。这个在测量数值更多的情况下更为突出,一个高效率的查找算法有

助于减小程序运行功耗。数字信号处理中的运算,采用FFT和快速卷积等,可以节省大量运算时间,从而减少功耗。

④在精度允许的情况下,使用简单函数代替复杂函数作近似也是减少功耗的一种方法。