基于TMS320C64X协处理器TCP的Turbo译码实现

2008-09-12

作者:李佳宁, 于宏毅

摘 要: 介绍了TMS320C64X系列DSP内部Turbo码协处理器" title="协处理器">协处理器(TCP)的结构和算法。给出了使用TCP实现符合3GPP" title="3GPP">3GPP协议的Turbo译码的程序流程,实现了一种使用中断服务程序控制的高效处理流程,最后给出了TCP译码性能与处理时延" title="时延">时延的硬件实现结果,并做出了一定的分析。

关键词: TMS320C64X TCP Turbo Decoding 性能

自1993年Turbo编码理论提出以来,有关Turbo码设计及其性能的研究已经成为国际信息与编码理论界最为重要的研究课题之一。Turbo码在低信噪比下所表现出的近Shannon限的性能使得它在深空通信、移动通信等领域中有着广阔的应用前景。由于Turbo码编码方式灵活、译码算法复杂,不适合在传统硬件电路如FPGA上实现。TMS320C64X是TI公司推出的高性能定点DSP系列,片上除了高性能的C64x数字信号处理内核外,还集成了Turbo码协处理器(TCP,Turbo Coder Coprocessor),用于对符合3GPP协议以及IS2000协议的Turbo编码进行高速译码。

1 TCP的基本结构

TMS320C64X是TI公司最新推出的处理能力高达4800MIPS的高性能DSP,内部嵌入了Turbo译码协处理器(TCP)和Viterbi译码协处理器(VCP),专门用于无线通信中的高速数据处理。 片上的TCP能够对多达36路的384kbps或6路2Mbps的Turbo编码信道在迭代6次的情况下进行译码,其高速并行结构能够在小于2ms的时间内完成3GPP协议中的2Mbps业务迭代译码,并且能够通过编程控制性能进一步减少处理时延。

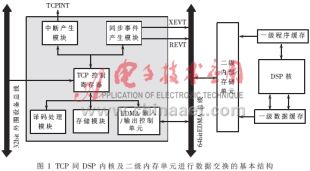

TCP通过EDMA(增强型DMA)同L2存储器(二级内部存储单元)进行数据交换" title="数据交换">数据交换,其基本结构如图1所示。TCP控制寄存器" title="控制寄存器">控制寄存器控制整体工作状态,包含相关编码信息、DSP总线传输能力、译码性能等信息;EDMA输入/输出单元控制EDMA总线实现二级内部存储单元同TCP之间的数据交换;同步事件产生模块产生EDMA读/写同步事件;内部存储模块和译码处理单元负责数据存储与译码计算。

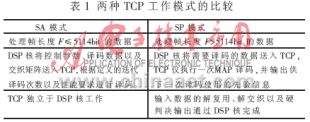

TCP有两种工作方式:Standalong(SA)模式与Shared Processing(SP)模式。在SA模式下,TCP完成编程规定次数的迭代译码并输出硬判决结果;在SP模式下,TCP仅完成一次MAP算法并输出供下一次译码使用的先验信息。表1示出了两种工作方式的区别。

3GPP协议中支持Turbo码的信道最大编码块的大小为5114bit,所以在实现上选择TCP工作在SA模式。

2 TCP的译码算法

MAP算法[1]是一种对具有有限状态马尔可夫特性的码及离散无记忆特性的信道提供逐符号或逐比特似然值的最优算法。Log-MAP算法[2]将标准算法中的似然值全部用对数似然值表示。这样乘法运算就变成了加法,加法变成了ea+eb=emax{a,b}+ln[1+exp(-a-b)],这里的对数项可通过一次查表和一次加法运算实现。Max-Log-MAP算法[2]在上述对数域的算法中,将似然值加法表示式中的对数分量忽略掉,使似然加法完全变成求最大值运算。

由于Turbo码编码方式灵活、译码算法复杂,所以在传统硬件电路上实现Turbo译码比较复杂。

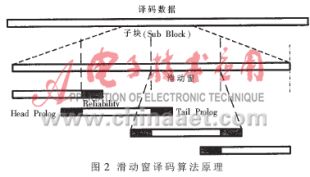

TCP很好地解决了算法实现中存在的问题。TCP使用滑动窗译码算法[5],将接收序列分割成子块(Sub block)送入结构相同的多个并行译码器进行处理,分割数量的原则是保证多个译码器并行度达到最大。每个子块通过多个滑动窗使用Max-log-MAP算法进行译码,译码过程中产生的临时数据α和β保存在内部存储模块的α单元和β单元中,需要时再通过计算得到先验信息或译码结果。滑动窗译码算法的原理如图2所示。

Turbo码编码时,编码器的状态转换关系是连续的马尔科夫过程。在译码时,需要确定编码器的初始状态和终止状态以及状态之间的转换关系。接收序列被分割为多个子块之后,状态的连续性被打断。这样,对于输入到一个译码器中的子块就不能确定其初始状态和终止状态。因此,把一个子块分为三个部分:头延伸(Head Prolog)、可信部分(Reliability)和尾延伸(Tail Prolog)。Head Prolog初始状态和Tail Prolog终止状态都设为等概率,然后根据接收序列以及编码器状态转换规律逐步计算Reliability。在Reliability部分、起始时刻值和终止时刻近似调整为分割前的状态时,Head Prolog和Tail Prolog为冗余重叠的部分,此时计算译码输出只需考虑Reliability部分,所以算法在译码性能上没有什么影响,但是能够极大地减少处理时延。另外,TCP还提供停止迭代译码标准Stopping Criteria,可通过对外信息信噪比(SNR)的估计来判断是否需要继续进行迭代。如果当前信息已经不能再提供编码增益,则立刻输出硬判决结果而不考虑剩余的迭代次数。

3 TCP的编程实现

3.1 输入数据的量化

TCP要求输入数据为8bit的有符号数,并认为其格式为:SIIII.FFF(S为符号位,I为整数位,F为小数位)。假设接收信号可以表示为:Ri=![]() ×ui+ni。其中,ui=±1;ni为发送端经过BPSK映射的原始数据;Esymbol是发送端符号能量,数据量化时需要去掉这个能量,同时将数据恢复成BPSK映射之前的形式。而一个分量译码器产生的先验信息[2~3]可以表示为:Wk=

×ui+ni。其中,ui=±1;ni为发送端经过BPSK映射的原始数据;Esymbol是发送端符号能量,数据量化时需要去掉这个能量,同时将数据恢复成BPSK映射之前的形式。而一个分量译码器产生的先验信息[2~3]可以表示为:Wk=![]() xk+

xk+![]() zk+Wk(

zk+Wk(![]() yk)。其中,

yk)。其中,![]() xk由系统比特xk产生,

xk由系统比特xk产生,![]() zk由上级译码器生成的先验信息zk产生,Wk(

zk由上级译码器生成的先验信息zk产生,Wk(![]() yk)由校验比特yk产生,σ2为高斯白噪声的方差。通常情况下,为了方便计算,去掉其中的系数

yk)由校验比特yk产生,σ2为高斯白噪声的方差。通常情况下,为了方便计算,去掉其中的系数![]() 。于是输入信号的量化因子可以表示为:ScaleFactor=

。于是输入信号的量化因子可以表示为:ScaleFactor= 。其中,

。其中, 可以通过计算信号幅值的均值得到:

可以通过计算信号幅值的均值得到:![]() 通过计算接收信号幅值的方差得到:

通过计算接收信号幅值的方差得到:![]()

![]() 。

。

3.2 控制寄存器的配置

TCP中包含12个控制寄存器,这些寄存器分为三类:基本参数寄存器、EDMA接口参数寄存器以及尾比特寄存器。

基本参数:控制编码信息以及译码的相关标准;

EDMA接口参数: EDMA通道的相关参数;

尾比特:确定编码器最终状态的信息。

3.3 EDMA配置以及DSP核同TCP之间的数据交换

EDMA是C6000系列DSP中的一个重要单元,负责二级内存(L2 存储器)同各个外设之间的数据交换[7~8]。

C64X系列DSP的EDMA通道共有64条,其中31/30(读/写)专门用于DSP核同TCP之间的数据交换。EDMA完成参数配置并启动之后,EDMA通道进入使能状态等待触发。TCP启动后,产生相应的读/写同步事件TCPXEVT/TCPREVT触发EDMA通道进行数据传输。一次简单译码处理中的完整触发过程如图3所示。

结合TCP控制寄存器中的EDMA接口参数使用提供的API函数[9]配置EDMA通道传输参数 [7] 。

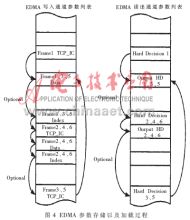

3.4 高效的TCP处理模式

通常情况下并不满足于对一段编码数据实现译码,而是希望DSP满负荷地工作,对连续到达的各种编码格式(已知)的数据完成译码。在这里设计了一种奇偶交替的译码模式:将译码数据按照到达顺序分为奇数组和偶数组,生成满足编码格式的TCP控制寄存器参数以及相应的EDMA配置参数。TCP进行第N个编码数据译码处理的同时,EDMA写通道向TCP传输第N+1个编码数据控制参数和译码数据,EDMA读通道将第N-1个编码数据的译码结果输出,同时利用译码完成产生的中断服务程序处理第N+2个数据的相关参数配置以及数据量化。EDMA的RAM中的参数存放格式如图4所示。

3.5 TCP程序实现流程

总之,TCP程序实现应包括以下步骤:

(1)数据量化;

(2)构造TCP控制参数以及EDMA配置参数;

(3)启动并配置EDMA通道;

(4)启动TCP产生同步事件触发EDMA通道;

(5)接收硬判决结果。

(因本文篇幅偏长,本刊删去了“TCP程序实现流程图”。如读者感兴起,可向作者索取。)

4 TCP译码性能硬件实现与分析

4.1 TCP译码性能

使用TMS320C6416 7E3(CPU时钟为705.6MHz),对原始长度为336bit和3840bit的符合3GPP协议的码率为1/3的Turbo编码数据进行译码。译码性能如图5和图6所示。

4.2 TCP译码处理时延

使用TMS320C6416 7E3(CPU时钟为705.6MHz),对原始长度为336bit和3840bit的符合3GPP协议的码率为1/3的Turbo编码数据进行译码。考虑迭代次数I=6、8、16;Prolog长度P=24(未经速率适配)、48(经过速率适配)时得到的处理时延结果如表2和表3所示(只考虑译码处理时延,参数配置以及EDMA通道进行数据传输所用时间不计算在内)。

通常情况下,Turbo码的性能同交织长度有很大关系,交织长度越大,性能越好,但所需处理时延也就越高。使用TCP译码,长度为336bit的短数据帧经过8次迭代,在信噪比(SNR)为2dB下误码率(BER)达到10-7量级,所需处理时延大概为50~60μs;长度为3840bit的数据帧,经过8次迭代,在信噪比为0.8dB下误码率达到10-8量级,处理时延大约为300~350μs。可以认为TCP在译码性能与处理时延两个方面都能够比较好地满足3G系统对于译码模块的要求。TCP作为C64X系列DSP的一个协处理器,相关的速率适配、数据量化等一系列工作都可以通过DSP核完成,较传统的硬件电路有很大优势。

参考文献

1 Claude Berrou and Alain Glavieux.Near Optimum Error Correcting Coding And Decoding:Turbo-Codes.Texas Instrument,1996

2 Patrick Robertson. Optimal and Sub-Optimal Maximum A Posteriori Algorithms Suitable for Turbo Decoding.Texas Instrument,1997

3 TMS320C6000 Peripherals Reference Guide.Texas Instrument,2001

4 TMS320C64x DSP Turbo-Decoder Coprocessor (TCP) Reference Guide. Texas Instrument,2003

5 Using TMS320C6416 Coprocessor Turbo Coprocessor. Texas Instrument,2003

6 TMS320C6416 Coprocessors and Bit Error Rates. Texas Instrument,2003

7 TMS320C6000 DSP Enhanced Direct Memory Access (ED-MA) Controller Reference Guide. Texas Instrument,2002

8 Applications Using the TMS320C6000 Enhanced DMA.Texas Instrument,2003

9 TMS320C6000 Chip Support Library API User’s Guide.Texas Instrument,2003