摘要:基于FPGA的三相函数信号发生器以DDS为核心,在Altera公司CycloneⅡ系列EP2C8T144C8上实现正弦波、方波、三角波和锯齿波信号的产生,利用单片机PICl8F4550控制波形的频率及相位差。同时单片机通过DAC0832控制波形数据转换DAC902参考电压实现在波形幅度的控制,D/A输出的波形经过放大、滤波后输出。波形参数的输入输出通过触摸屏和液晶屏实现,测试结果显示该系统具有较高的精度和稳定性。

模拟函数信号发生器输出波形易受输入波形的影响,难以实现移相控制,移相角度随所接负载和时间等因素的影响而产生漂移,频率、幅度的调节均依赖电位器实现,因此精度难以保证,也很难达到满意的效果。基于FPGA的数字式三相信号发生器,精度较高,移相控制方便,实现频率为1 Hz~10 MHz、幅度0.1~10 V,分辨率为1°,频率和幅度的调节均可程控的三相函数信号发生器。系统还具有输出灵活、易于系统升级等优点。

1 函数信号发生器的原理

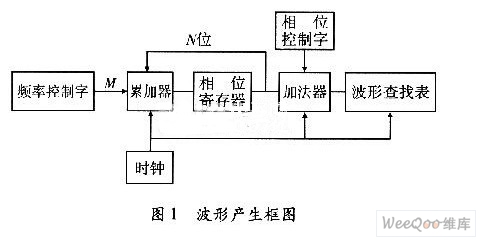

基于DDS原理,频率控制字M和相位控制字P分别控制DDS输出波形的频率和相位。相位累加器是整个波形产生的核心,它有一个累加器和一个N位相位寄存器组成。每来一个时钟脉冲,相位寄存器以步长M增加,如图1所示。相位寄存器的输出与相位控制字相加,其结果作为波形查找表的地址。波形查找表由ROM构成,内部存有一个完整周期的波形的数字幅度信息,每个查找的地址对应波形中0°~360°范围的一个相位点。查找表输入的地址信息映射达成波形幅度信号,同时输出到数模转换器的输入段,DAC输出的模拟信号经过程控滤波器,可得到一个频谱纯净的波形。

相位寄存器每经过2N/M个fc时钟周期后回到初始装状态,相应地波形查表经过一个循环回到初始位置,DDS输出一个波形。输出的波形周期为Tout=(2N/M)Tc,频率为

DDS的最小分辨率为fmin=fc/2N,当M=2N-l(即一个周期内只取两个点)时,DDS最高的基波合成频率为foutmax=fc/2,根据取样定理,这在理论上是可行的,考虑到失真度的问题,取i(i>2)个点,则最高频率为当M=2N-3时,foutmax=fc/i。

2 系统总体设计

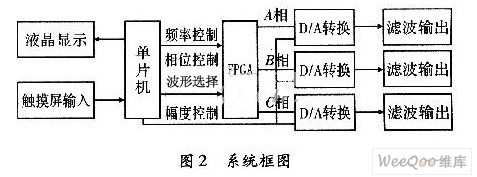

系统由单片机控制模块、FPGA波形产生模块、数模转换模块、滤波输出模块、触摸屏输入和液晶显示模块组成,单片机控制FPGA产生输入频率和相位差的三相正弦波、方波、三角波和锯齿波,经过D/A转换后滤波输出,三相波形的幅度也由单片机通过改变D/A的参考电压控制。具体系统框图,如图2所示。

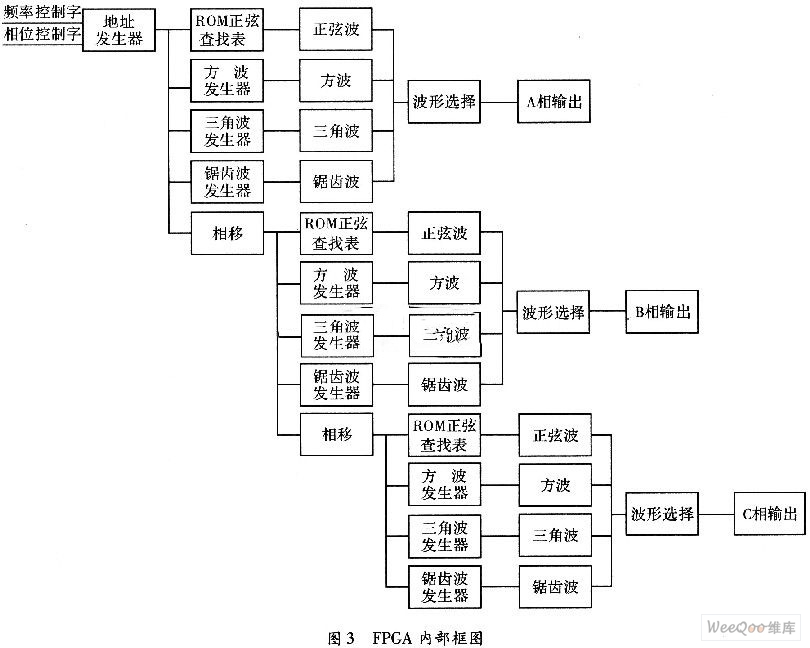

FPGA部分具体框图,如图3所示,基于DDS原理,主要由相位累加器、正弦波ROM查找表、方波发生器、三角波发生器、锯齿波发生器和波形选择模块组成。根据单片机设置相移值调整三相波形的相位差,波形选择也由单片机控制。

2.1 分频模块设计

为了对波形频率精确控制,不同频率段需要不同的输入频率。项目设计中采用50 MHz外部有源晶振,利用FPGA内部锁相环将频率锁定在40.96 MHz,然后该频率进行10 MHz,100 MHz,1 000 MHz,10 000 MHz,如图4所示,这样就得到了5个不同的频率区间,最后通过5选1数据选择器由单片机选择所需要的时钟频率。时钟频率与输出波形频率之间具体关系,如表l所示。

2.2 波形产生模块设计

2.2.1 正弦波

正弦波的数据需要转换为*.mif文件后存放到ROM中,mif文件有固定格式规定了每个字的位宽WIDTH、总字数DEPTH、地址进制基数ADDR-ESS_RADIX和数据进制基数DATA_RADIX。在Matlab环境中编程计算出正弦波数据,然后生成mif文件。

EP2C8T144C8拥有较充裕的存储空间。因此,设计中为了提高精度在ROM中存放4 096个正弦数据,频率控制字、相位控制字由单片机控制产生,经过相位累加器组成地址发生器,产生的地址连到ROM的地址线上进行查表得到波形数据。

2.2.2 方波

方波算法比较容易实现。由于其只有高低电平两种状态。因此,只需要在一个周期的时间中间位置翻转电平即可。由于相位累加器的值是线形累加的,地址address的值也是线形累加的,对所给地址值address进行判断,当地址值的最高位为O时,便将波形幅值各字位赋值1,否则赋值0。就可以实现最简单的占空比50%的方波。

为了实现占空比可调,设计中增加一个变量PWM_zkb[11..0],让地址值与WM_zkb[11..O]比较,Adress[11..0]

2.2.3 三角波

三角波的生成原理与方波生成原理相似,也是对地址Address的值进行判断,当其最高位为0时,取其O~ll位为三角波的波形幅值,即令Data_out[11..0]=Address[11..0]。当其最高位为l时,对其0~1l位的值取反后再作为三角波的波形幅值,即令Data_out[11..0]=not(Address[11..0])。

2.2.4 锯齿波

锯齿波的产生也是基于上述原理,是对地址Address的值进行判断,当其最高位为O时,取其0~ll位为三角波的波形幅值,即令。Data_ out[11..0]=Address[11..0]。当其最高位为1时,对其最高位的值取反后作为锯齿波的波形幅值,即令Data_out,[11..0]=Address[11..0]and“011111111111”。

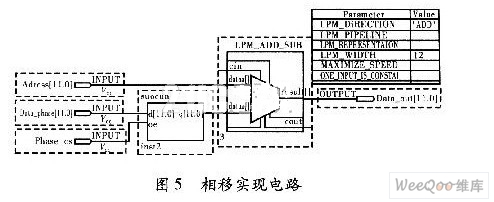

2.3 相移的实现

在A相地址的基础上,增加一个累加器,输入段分别是A相地址和偏移值,经过累加之后得到B相波形地址,然后根据此地址对ROM寻址或者在地址的基础上生成方波、三角波和锯齿波。如图5所示,A相、B相及B相、C相之间的偏移量有单片机控制,数据经过锁存后送入累加器。

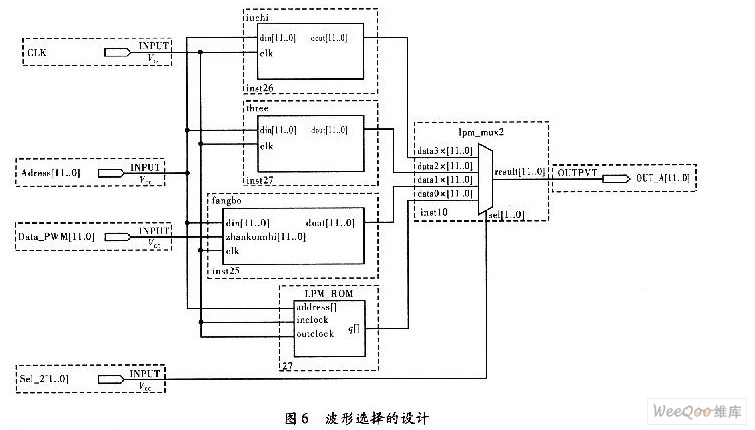

2.4 波形选择的实现

根据设计要求,每一相都可以实现正弦波、方波、三角波和锯齿波任意一种波形的输出,设计了一个4选1数据选择器,控制端Sel[1.-.0]与单片机IO口相连,如图6所示,以A相为例。

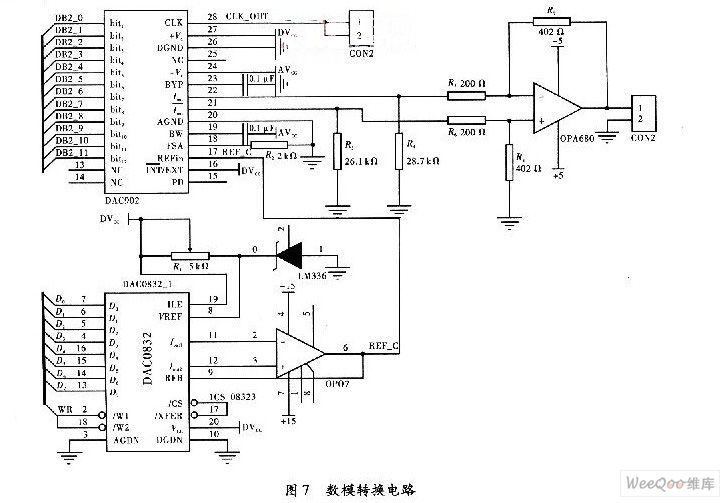

2.5 幅度控制的实现

参考电压可通过INT/EXT端选择内部和外部。当该端口为高电平时选择外部参考电压,只要改变参考电压,就可以改变输出波形的幅值。DAC902外部参考电压范围0.10~1.25 V,因此只需采用8位D/A既可实现0.01 V的步进。如图7所示,DAC0832输出接到DAC902参考电压输入端REFin,通过单片机控制DAC0832输出,进而控制DAC902参考电压。

3 系统测试

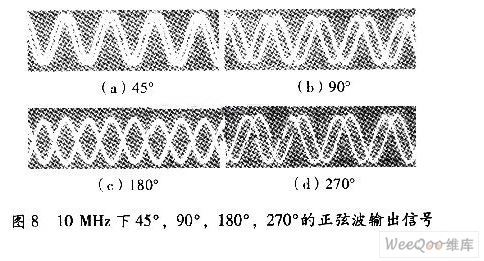

本系统波形参数设置通过触摸屏输入完成,用示波器测试50 Ω负载下的输出波形,比较设置值与测试值之间的误差,图8为信号源输出频率为10 MHz,峰峰值为5 V,两路信号相移分别为45°、90°、180°、270°时,在使用Fluck PM3394B 200 MHz Combiscope Instrument的“Analog”模式下,用数码相机拍摄的正弦波的输出波形。

经过多次测试和反复改进,最终实现了如下技术指标:

(1)输出波形:正弦波、方波、三角波、锯齿波。

(2)输出波形频率范围:0.1 Hz~10 MHz。

(3)输出频率调节步长:0.01 Hz~10 kHz。

(4)输出电压范围:10 mV~10 V(峰峰值)可调,幅度步进最小10 mV。

(5)方波占空比调节范围:1%~99%。

由于示波器只有两个通道,因此只能测量两项信号之间的相位差。

在频率稳定度方面,正弦波、三角波、方波和矩形波输出波形稳定,这正是体现了DDS技术的特点,输出频率稳定度和晶振稳定度在同一数量级。由于采用了FPGA的内部时钟,在倍频分频的结果后还是无法达到计算的时钟,因此存在着误差,但在频率较高部分误差稍明显,因此设计中采用了软件修正,从而减少了频率较高部分的误差。

对于波形幅度的控制上,由于波形在电路网络存在一定的衰减,因此在程序中采用软件补偿进行修正。从测试结果可以看书软件补偿做得越细致误差越小。

4 结束语

本项目以多功能、低功耗、操作方便、结构合理、易于调试为主要设计原则,在系统设计过程中,力求硬件线路简单,充分发挥软件编程方便灵活的特点,并最大限度挖掘FPGA片内资源,来满足系统设计要求。

利用硬件描述语言VHDL编程,借助Ahera公司的Quartus II软件环境下进行了编译及仿真测试,在FPGA芯片上设计了函数发生器,产生正弦波、三角波、方波等多种波形,系统的频率分辨率高,频率切换速度比较快。设计采用了EDA技术,缩短了开发研制周期,提高了设计效率,而且使系统具有结构紧凑、设计灵活、实现简单、性能稳定的特点。