引言

ADC 采用逐次逼近型(SAR)结构,具有125kHz采样速率,12位精度。电容电荷重新分布D/A技术采用电荷按比例缩放子DAC组合,进而大大减小了芯片电容面积,也避免了采用像电阻阵列结构所带来的固有直流功耗,通过对DAC级间耦合电容值的优化设计,提高了ADC精度。比较器采用自消除失调电压的开关电容比较器。

据调研,市场上现有触摸屏控制器芯片主要来自ADI公司(如AD7843、AD7873、AD7877)和TI公司(如ADS7843、TSC2046、TSC2003),对其性能进行对比,如表1所示。

表1触摸屏控制器芯片性能对比结果

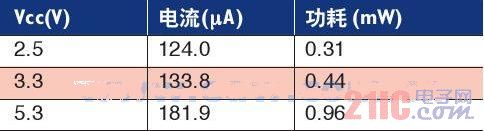

通过对ADC电路进行优化设计,可使触摸屏控制器的功耗不足1mW,低于表1中现有芯片的功耗。

因此本设计的侧重点是在满足工作电压、工作温度的基础上,使ADC工作在睡眠/唤醒两种工作模式下,以大大降低功耗。为了实现这一目的,芯片中设计了电压基准电路模块,以控制ADC的开启和关闭。

电路设计与分析

ADC的整体结构设计

SAR ADC包括采样保持电路、比较器、DAC、逐次逼近寄存器、时序产生及数字控制逻辑电路。模拟输入电压(vin)由采样/保持电路保持,N位SAR ADC需要N个比较周期,同时在当前一位转换完成之前不得进入下一次转换。因此该类ADC能够有效节省功耗和空间,该结构中DAC和比较器设计的好坏对整个ADC转换精度起关键性的作用。

DAC的设计

DAC结构设计

由于在CMOS集成电路中,制造电容比制造电阻更节省芯片面积,而且电容上没有功率损耗,另外,开关电容网络可以完成采样保持的功能,节省了单独的采样保持电路。因此,本文选择采用开关电容网络构成电荷按比例缩放式DAC。

电荷按比例缩放式DAC主要由按照二进制加权排列的电容阵列组成。电容是CMOS工艺兼容的,而且相对精度高,所以电荷按比例缩放式DAC在CMOS工艺中容易实现。然而当其精度提高时,一方面所需的大电容导致芯片尺寸过大,而且大电容需要大充电电流,充电时间过长;另一方面最高权位和最低权位的电容比例变得很大,比值越大,电容匹配越差。所以高精度DAC通常由低精度DAC通过电容耦合来实现。这种耦合结构成功的关键之一是确定耦合电容值。只有选择合适的耦合电容值,才能保证各位间的权重关系,并实现D/A转换,如图1所示。

图1 电荷按比例缩放式DAC组合的实现

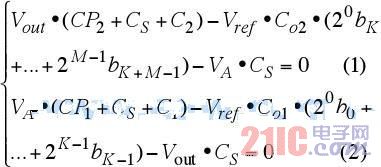

设图1中A点到地的电容为CA,DAC的缩放通过电容CS实现,CS和LSB阵列的串联组合必须接于MSB阵列的左侧,因此可得:

版图设计时,为了消除介电松弛对转换精度的影响,消除电荷扩散和介电极化效应,减少噪声干扰,电容上极板上会加静电屏蔽层,并接地。为了消除衬底噪声,将电容做在阱里,阱接地。电容阵列极板和屏蔽层或阱间形成的寄生电容,使电路中耦合电容两极板地的寄生电容值增大,使得在确定耦合电容值时,必须考虑寄生电容的影响。

DAC级间耦合电容值的优化设计

图1中CP1、CP2分别为A、B两点到地的寄生电容。转换过程中A、B电荷守恒,于是可得:

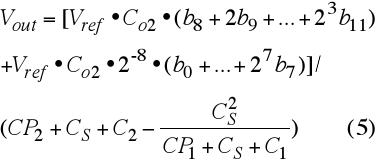

C1、C2分别为低权位和高权位子DAC的总容值;CO1和CO2分别是低权位和高权位子DAC的单位容值;K=8,M=4。解方程组,得到输出电压为:

由电路参数可知:C02=4C,C01=2-2C=2-4C02,所以:

以高权位DAC为基准,输出应有如下表达式:

比较式(4)和式(5),可得:

比较式(4)和式(5),可得:

分析耦合电容公式(6)可知,耦合电容大小与低权位寄生电容有关,而与高权位寄生电容无关。高权位DAC的寄生电容不影响高低权位间的比例关系,只影响最终输出电压的绝对值。从输出表达式(5)中可以看到,高权位寄生电容出现在分母中,它会使输出绝对值变小,所以应该尽量减小高权位寄生电容值。低权位寄生电容也会使输出绝对值变小,但这个影响很小,和高权位寄生电容的影响相比,几乎可以忽略不计。根据(6)式,低权位寄生电容出现在耦合电容表达式的分子上, 所以低权位寄生电容越大,耦合电容值也越大,通过增大耦合电容值就可以消除低权位寄生电容的影响。

寄生电容通常由电容极板和屏蔽层或阱形成,因此寄生容值和高低权位寄生电容大小有关系。所以,为了减小高权位寄生电容对输出电压的影响,在版图设计时,应尽量减小寄生。

综合考虑输入电容要求及电容匹配精度后,选取做在N阱里的双poly电容。单位电容取为400fF ,权位电容采用单位电容并联结构,以提高匹配性。采取中心对称布局,电容上覆盖metal2作静电屏蔽层;N阱和metal2均接地。寄生电容主要包括电容上极板和metal2之间、走线与metal2之间的寄生电容等。虽然高4位子DAC的寄生电容不影响权位间比例关系,但它会使输出电压值降低,以致需要更高精度的比较器。所以将覆盖在高4位子DAC电容上的metal2开孔,减小其寄生容值。

比较器的设计

由于DAC模块采用的是开关电容网络,在此将设计一个可消除直流失调电压的开关电容比较器。开关电容比较器使用组合开关电容和开环比较器。它的优点是,差分信号可用单端电路进行比较,且可对开环比较器直流失调电压自动校零。

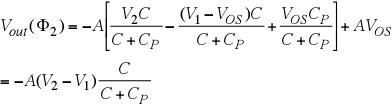

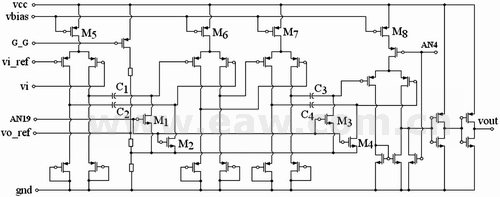

本文采用如图2所示结构设计SAR ADC中的开关电容比较器。

图2 开关电容比较器电路图

当图2中的开关φ1关闭时,输入失调存储在输入串联的电容C上,电容C将对比较器的输入失调电压VOS自动校零。电容CP表示比较器输入到地的寄生电容。在φ1相位周期结束时,C和CP上的电压为:

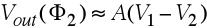

开关φ2关闭时,

如果CP小于C,那么上式可以简化如下:

因此电压V1和V2的差值通过比较器的增益得到放大,后面的锁存器根据比较器A的输出产生逻辑电平,输出Vout,直流输入失调电压自动校零。

比较器A电路实现如图3所示。

图3 自消除失调电压比较器电路实现方案

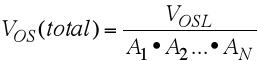

N级比较器的最终失调电压可表示为:

其中A1~AN为各级的放大倍数,VOSL为锁存器的失调电压。根据整个电路的增益要求和失调要求抑制的强度来取值,这里取N=4。

该比较器由三级差分放大器和一个输出级组成,管子M1、M2、M3、M4在采样期间导通,通过对电容C1、C2、C3、C4充电,对第二、三、四级差分放大器定静态工作点,管子M0~M4在比较转换期间不导通。由于在采样期间,各级差分输入端都接静态工作点电压,相当于交流地,失调电压引起的输出储存在电容C1、C2、C3、C4上,比较时输入电压跟存储在电容上的失调电压串联输入,这样可以使输入端的失调电压不被一级级放大输出,从而减小失调的影响。输出级由一个双端变单端的差分放大器和两个非门组成,其功能相当于前述的锁存器。

比较器的工作时钟fCLK=2MHz,因此电流源提供的电流要相对大一些,管子M5、M6、M7、M8充当电流源,由vbias控制开关,以确定电路的直流偏置。vbias是比较器电压基准电路的输出。

电压基准电路的设计

由于比较器电路中电源电压VCC的变化范围为2.5V~5.3V,其变化范围较大,因此对于比较器而言,使所有管子都处于饱和状态的直流工作点并不多。当电源电压变化时,希望得到稳定的直流偏置电流,即要为图3中偏置管M5、M6、M7、M8提供一个稳定的基准电压。理想的基准电流或电压是与电源和温度变化无关的,因此采用自举基准技术,设计如图4所示。

图4 阀值基准电路

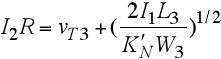

图4中管子M5、M6使得电流I1、I2相等。I1流经管M3产生电压VGS3,I2流过R产生电压I2R。因为这两个电压连在一起,就确定出一个平衡点,用Q表示。描述这个平衡点的方程式为:

因为I1=I2=IQ,可以解出:

首先,I1和I2都不作为VCC函数而随其改变,于是IQ对VCC的灵敏度基本为零,作用于一个电阻就得到一个基准电压。

但是,图4中有两个可能的平衡点。一个在Q,而另一个则在原点。为了避免电路选择错误的平衡点,必须有一个启动电路。图4中的虚线框内即为启动电路。启动电路的开启和关闭由数字信号AN1和AN2控制,为了控制功耗,启动电路开启后会马上关闭。

通过信号sel-y开关控制比较器电路,即sel-y=1时,比较器关闭,sel-y=0时,比较器开启,使ADC工作在睡眠/唤醒两种工作模式下,在没有触摸事件时,直流功耗大幅度降低。

版图实现及电路仿真分析

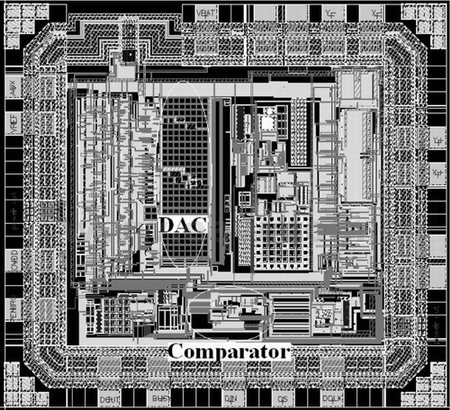

如图5所示,版图采用SMIC 2P2M 0.35μm CMOS工艺实现,面积为1600x1700um2。

图5 触摸屏控制器版图设计结果

采用Cadence环境下的Spectre和Spectre Verilog仿真工具进行仿真。提取版图寄生参数,得到图1中A、B点的寄生容值分别为212.11fF、278.53fF。根据式(6)可得优化后的耦合电容值CS为1.72pF。

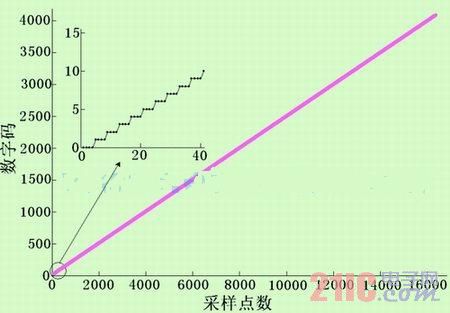

为了测量ADC的DNL和INL,给ADC加了斜波信号。可以从仿真图中输出数字码的文本文件,利用该文件可以通过Matlab程序绘图并计算其DNL和INL值。绘图结果如图6所示,经计算DNL为1/4LSB,INL为-1LSB。

图6 ADC全范围仿真图

从图6中可见,ADC输出了4096个台阶,即完成了12位的A/D转换。

对SAR ADC功耗进行测试,测试结果如表2所示。

表2不同电压下SAR ADC功耗测试结果

结语

通过对电荷按比例缩放式DAC组合结构中寄生电容对耦合电容影响的分析,给出了耦合电容值的优化设计方法,通过开关电容比较器结构,消除了比较器的失调电压。优化后的SAR ADC电路满足二进制权重关系,转换结果达到了12位的转换精度。并且成功利用电压基准电路模块,使ADC工作在睡眠/唤醒两种工作模式下,电路功耗大大降低。在时钟频率为2MHz情况下测试,SAR ADC功耗小于1mW。结果表明,本文设计的基于触摸屏控制器的SAR ADC电路功耗低并具有较高精度,可以应用在任何中等精度、中等转换速率的场合,并且对触摸屏控制器的优化设计具有很好的指导作用。