数字调制解调器在点对点的数据传输中得到了广泛的应用。通常的二进制数字调制解调

器是建立在模拟载波上的,在电路实现时需要模拟信号源,这会给全数字应用场合带来不方便。本文分析了MSK(最小频移键控)数字调制信号特征,提出一种全数字固定数据速率MSK调制解调器的设计方法,应用VHDL 语言进行了模块设计和时序仿真。硬件部分在Altera公司 EP2C15AF256C8N FPGA 上实现了MSK 数字调制解调器,并在常州市科技攻关项目:粮库储粮安全网络智能监测系统的嵌入式测控部分应用。实测表明,数字MSK 调制解调器具有络恒定,相位连续,频带利用率高的优点。并且在FPGA 上实现时设计效率高,可与其他模块共用片上资源,对于全数字系统中的短距离数据通信是较好的解决方案。

1 数字MSK 调制的载波频率与相位常数

最小频移键控MSK ( Minimum Frequency Shift Keying ) 是二进制连续相位FSK 的一

种特殊形式。有时也称为快速频移键控(FFSK)。MSK 调制方式能以最小的调制指数(0.5)获得正交信号, 同时MSK 比2PSK 的数据传输速率高,且在带外的频谱分量要比2PSK 衰减更快。

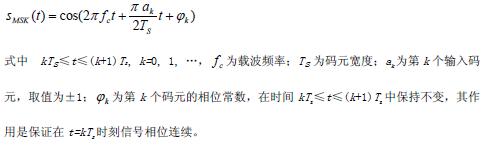

MSK 是恒定包络连续相位频率调制,其信号的表示式为

MSK 调制必须同时满足调制指数0.5 和相位连续条件,由MSK 信号表示可知,为了使调

制指数为0.5,MSK 信号的两个频率应分别为:

上式反映了MSK 信号前后码元区间的约束关系。MSK 信号在第k 个码元的相位常数不仅与当前码元的取值有关,而且还与前一个码元的取值及相位常数有关。在数字载波的情况下,上述条件等同于根据前一码元的相位,选择当前码元的相位是同相或反相,以保证数字MSK信号的相位连续。

2 数字MSK 调制解调器FPGA 模块实现

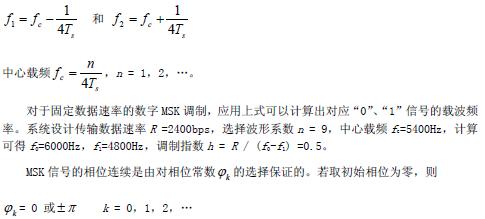

用FPGA 实现的MSK 调制器模块如图1 所示。

图1 MSK 调制器模块

图中预分频器和“0”、“1”码分频器组成载波发生器,在输入码序列同步信号的控制下

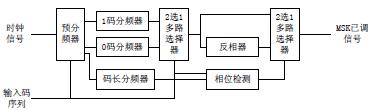

分别产生“0”码和“1”码的数字载波。为了方便设计与调整,预分频器设置2 级分频电路,分频系数分别为D1 和D2,从分频效率考虑,D1 和D2 的乘积应为总分频系数的最大公共因子。“0”码和“1”码分频器的分频系数C1、C2 的设置必须满足调制指数0.5 的条件。输入调制信号数字序列控制2 选1 多路选择器,选出对应输入码流中“0”、“1”码元的数字载波。相位检测模块与第二级2 选1 多路选择器、码长分频器和反相器组成连续相位形成电路。在前面确定“0”、“1”码元的数字载波时,每个码元的载波周期数也随之确定, 其中“0”、“1”数字载波相位差固定为180°,因此可以简单地用0、1 来表示2 个载波相位。在相位检测模块中,码长分频器作为1bit 延时的时钟信号,输入数字信号延迟一码元信号D-1 与前次产生的2 选1 选择器控制信号S 比较,得到前一码元结束时的相位Q-1,其结果如表1 所示。

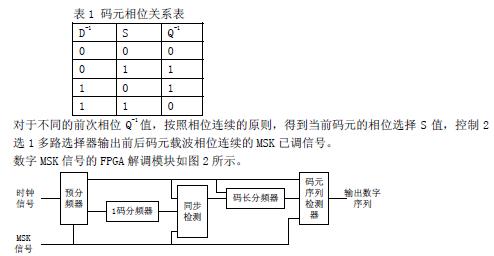

图2 MSK 解调器模块

数字MSK 信号的解调是由码元同步和码序列检测二部分实现的。预分频器、“1”码分频器和同步检测模块组成码元同步电路,通过对输入信号中的“1”码检测建立码元同步。在同步检测模块中,“1”码分频器的同相和反相码同时与输入信号比较,并由同步码长计数器计数,当计数长度等于码元长度时输出同步信号。进入码元同步状态后,在码长分频器输出的码元同步信号控制下,码序列检测器对输入信号中的“1”码(同相及反相码)进行检测并输出解调数字序列。解调模块中的预分频器和“1”码分频器和在半双工通信方式中可与调制模块合用以减少目标器件片上资源的占用。MSK 调制/解调器的FPGA 模块中,计数器、分频器和多路选择器用VHDL 程序可以简单

实现,码元序列检测器的部分VHDL 结构描述如下:

architecture behav of codesdect is

signal m : integer range 0 to 3;

signal sdata : std_logic_vector(2 downto 0);

begin

cdata<= wavenum;

process(clk,clr)

begin

if clr='1' then m<=0;

elsif clk'event and clk='1' then

case m is

when 0 => if datain = cdata (2) then m<=1; else m <= 0 ; end if;

…

when 2 => if datain = cdata (0) then m<=3; else m <= 0 ; end if;

when others => m <= 0;

end case;

end if;

end process;

process(m)

begin

if m=3 then outputt<='1';

else outputt<='0';

end if;

end process;

end behav;

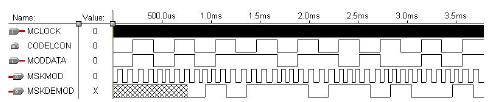

数字MSK 调制/解调器模块在Altera 公司FPGA:EP2C15AF256C8N 上实现。EP2C15 是Altera 公司基于90nm 工艺的第二代Cyclone 器件(CycloneⅡ),片内集成14,448 逻辑单元(LE),240Kb 嵌入式RAM 块,26 个18×18 乘法器,4 个锁相环(PLL),具有高速差分I/O能力,在音视频多媒体、汽车电子、通信及工业控制领域等有广泛的适用性,是一款高性能低成本器件。图3 是MSK 调制/接解调器的时序仿真结果。

图3 MSK 调制/解调器时序仿真

由图中可见,数字基带调制信号MODDATA 经过MSK 调制器被调制到高频数字载波上,形成MSK 已调信号MSKMOD,其中“0”码为2.5 个载波周期,“1”码为2 个载波周期,调制指数为0.5,同时载波相位连续。MSKDEMOD 为接收端MSK 解调后的信号,除了传输时延,解调信号完全恢复了发送端数字基带调制信号。

3 结论

MSK 调制具有载波相位连续,频带利用率高的优点,在通常的应用中需要专用集成电路

构成调制/解调电路。基于硬件描述语言用FPGA 实现MSK 调制/解调器,可充分利用FPGA片内资源,使数据采集测量控制与传输集中于单一芯片,有利于提高系统的经济性和可靠性,具有一定的应用价值。本文作者创新点在于提出了一种保证调制指数为0.5 同时载波相位连续的数字MSK 信号的设计方法,用VHDL 语言设计了调制/解调模块并在FPGA 器件上实现。