如今越来越多的视频设备以千兆位速率运行,它们通过相对较大的同轴BNC连接器互连。虽然这些连接器一般都具有良好的质量,但它们在设备中的性能表现却取决于它们在PCB上贴装得如何。非优化的连接器占位设计会导致阻抗失配、反射、信号损耗,并降低设备的信号保真度。BNC占位PCB布局设计任务,一般由线路布线设计师和硬件工程师负责,但他们通常没有时间或适合的工具顺利完成任务。本文介绍了BNC占位设计中的几个常见问题,并以插图说明了边缘贴装和插入式连接器的占位设计示例。这些连接器可与美国国家半导体的LMH0384 3G/HD/SD自适应电缆均衡器、LMH0303电缆驱动器及LMH0387可配置I/O器件搭配使用。

BNC的类型

视频设备在历史上一直将BNC与75?同轴电缆搭配使用。视频画面过去以标清速率(270Mbps)传输,后来升至高清速率(1.485Gbps),现已转换到3Gbps。BNC连接器须在信号损耗最小的情况下支持3Gbps的信号传输,同时还要保持75?的特征阻抗,并将反射降至最低。

许多连接器供应商都根据PCB上的贴装方式提供不同类型的BNC。基于机械方面的考虑,这些连接器可以采用垂直贴装、直角贴装或边缘贴装。在电气方面,信号引脚要么表面贴装在电路板顶层的连接焊盘上,要么焊接在金属化通孔内,信号布线则位于电路板的另一面。图1显示了一些插入式BNC的示例。图2是具有表面贴装信号引脚的边缘贴装BNC示例。图3是具有表面贴装信号引脚的直角BNC示例。

插入式BNC 示例

图1:插入式BNC 示例。

图2:边缘贴装BNC 示例。

图3:表面贴装BNC 示例。

BNC的测试

BNC是一种同轴连接器,专为支持高达3Gbps的视频传输而设计,其性能主要取决于BNC内的同轴结构,从BNC连接器至PCB的转换将严重影响BNC的性能。设计良好的BNC占位对保持BNC带宽及其特征阻抗必不可少。

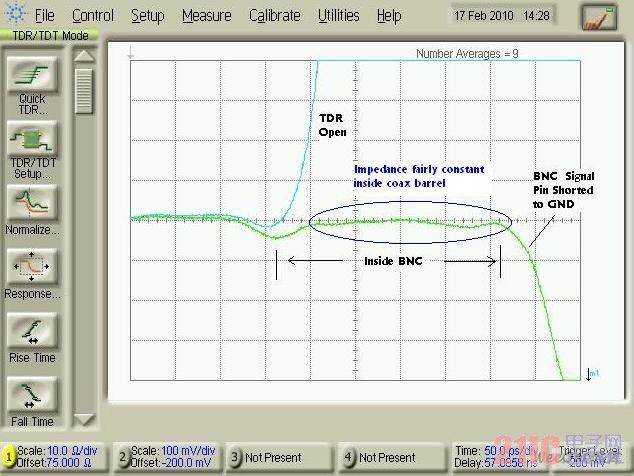

时域反射计(TDR) 是快速检验无信号引脚或占位的BNC同轴结构内部性能的一个很好的工具。进行该测试的简单方法是用扁平金属片使BNC的信号引脚与其屏蔽引脚短路,然后向 BNC内发射TDR阶跃脉冲。通过测量从发射的TDR阶跃脉冲反射回的信号,仪表即可测出在阶跃脉冲传输期间的阻抗。

图4显示了良好BNC的阻抗曲线。此直角BNC具有均匀的同轴结构,其75Ω特征阻抗在BNC内几乎保持不变,因此其占位应设计成具有与BNC相同的特征阻抗。

良好BNC的阻抗曲线

图4:良好BNC的阻抗曲线。

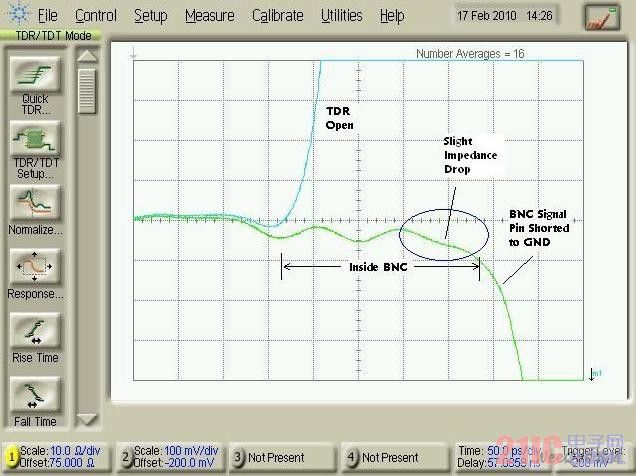

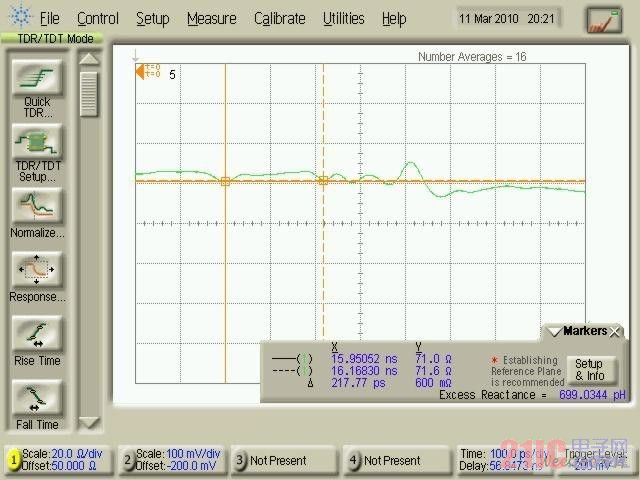

图5是一般BNC的阻抗曲线。此直角BNC的同轴结构有不均匀的征兆,在直角弯曲处,特征阻抗从标称的75Ω开始下降。在此情况下,其占位可以设计相对略高的特征阻抗以弥补BNC的缺陷。

一般BNC的阻抗曲线(阻抗下降)。

图5:一般BNC的阻抗曲线(阻抗下降)。

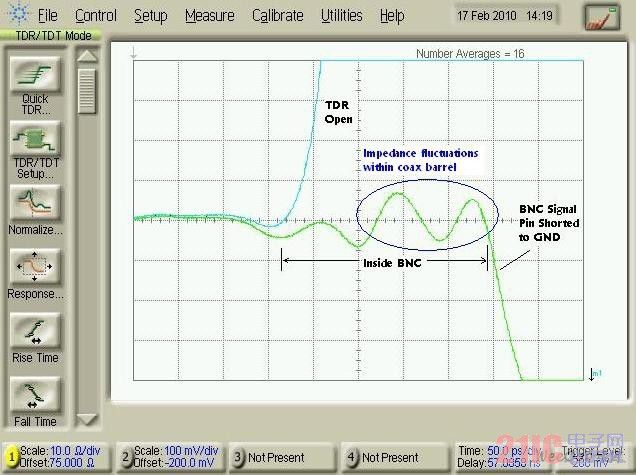

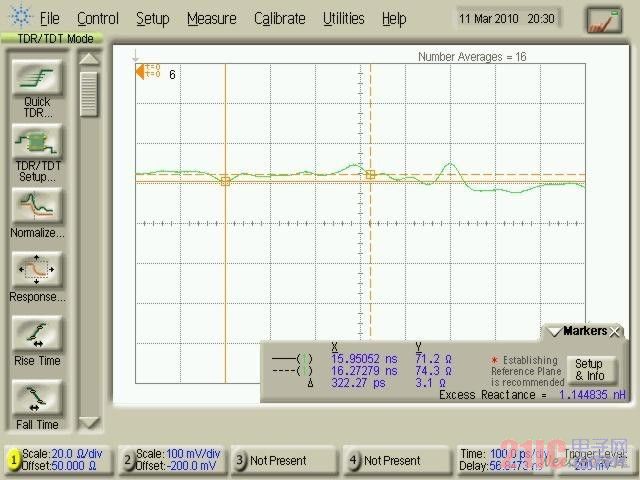

图6给出了不良BNC的阻抗曲线。此直角BNC说明其同轴结构有多种不均匀的征兆,在直角弯曲处,它难以保持其特征阻抗。在此情况下,很难为BNC提供具有良好回波损耗性能的占位。

不良BNC的阻抗曲线(阻抗波动)

图6:不良BNC的阻抗曲线(阻抗波动)

BNC至电路板连接中的常见问题

大多数表面贴装BNC连接器具有直径大约为30~40mil的大信号引脚。为将信号引脚正确焊接在PCB上,需要宽约50mil的连接焊盘。为便于布线,通常会使用8~15mil的较细表面走线,将信号从BNC连接器传送至多引脚数量的集成电路。

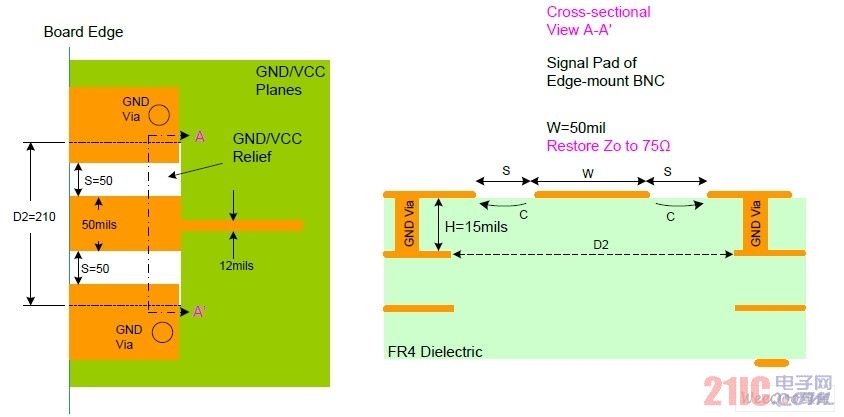

图7显示了未经优化的边缘贴装BNC占位的俯视图和截面图。为实现75?特征阻抗,专门设计了一条12mil的微带线,安置在GND层上方 15mil处。BNC的连接焊盘相当于50mil的微带线。由于在焊盘下方15mil处有GND层,所以焊盘的特征阻抗大大低于走线的特征阻抗。焊盘导致阻抗大幅下降,这将会影响信号质量并增加寄生电容,从而减小BNC带宽。

未经优化的边缘贴装BNC 占位的俯视图和截面图

图7:未经优化的边缘贴装BNC 占位的俯视图和截面图。

大多数视频设备会使用插入式BNC,因为它具有更好的贴装鲁棒性。BNC通常会贴装在电路板的顶层,其信号引脚焊接在较大的金属化通孔内,信号布线则位于电路板的底层。图8显示了未经优化的插入式BNC占位的俯视图和截面图。内部接地层和电源层与金属化通孔隔离,以免信号引脚短路。金属化通孔的圆柱形金属柱会产生少量电感。每个内部电源层都会为金属化通孔提供寄生电容,具体容量取决于内部电源层与金属柱之间的间隙。间隙小的大金属化通孔会产生过高的电容,从而导致阻抗大幅下降。如果信号布线在BNC的同一层,金属化通孔就会成为悬挂在信号走线上的残端,并产生较大的寄生电容,甚至导致更大幅度的阻抗下降。

插入式BNC 占位的俯视图和截面图

图8:插入式BNC 占位的俯视图和截面图。

未经优化的信号发射带来的影响

美国电影与电视工程师协会(SMPTE)发布了多个标准,用于管理通过同轴电缆的数字视频传输。这些SMPTE标准包括输入和输出回波损耗要求,主要规定了输入或输出端口与75Ω网络的匹配度。图9显示了回波损耗规格的相关SMPTE要求。不良BNC或未经优化的BNC占位会导致阻抗失配,使其难以通过SMPTE回波损耗限制。

视频端口的SMPTE 回波损耗要求

图9:视频端口的SMPTE 回波损耗要求。

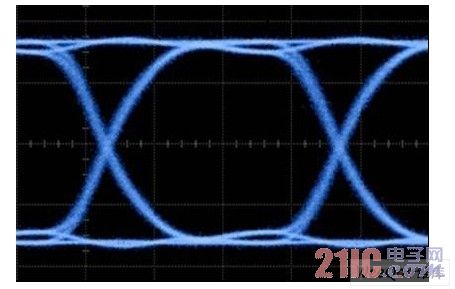

严重的阻抗失配会导致反射,从而对信号质量产生不良影响,并且还会缩小数据眼图的电压或时序裕度。信号发射中的过高寄生电容会降低信号路径的带宽,并导致符号间的干扰和抖动。图10给出了因非优化信号发射而降级的信号波形示例。

因非优化信号发射而降级的信号波形

图10:因非优化信号发射而降级的信号波形。

BNC的选择

如何选择BNC主要取决于BNC的机械结构,以及与设备外壳的兼容性。在电气方面,要求BNC能在插入损耗较低的情况下支持高达3Gbps的传输,同时还要求在其同轴结构内保持均匀性和几乎恒定的特征阻抗。它们最好具有较小的信号引脚,这样可在进行占位设计时尽量使用最小的通孔或连接焊盘,以便将阻抗的不连续性降至最低。

透明的BNC占位——表面贴装BNC

透明的占位(transparent footprint)是指其具有与BNC连接器相同的特征阻抗,且不会显着增加影响BNC带宽的电路寄生值。下面探讨几种方法,其中一种有效方法是排查信号路径、寻找偏离目标阻抗的电路板几何图形,并提出将阻抗恢复至目标值的方法。

如果是图7 所示的表面贴装BNC,则大的连接焊盘将导致阻抗大幅下降。提高其阻抗需要使用较大的电介质间隔(H>>15mil),但这并不是可选方案。提高焊盘阻抗的方法之一是移除焊盘下方的一个或多个层,以消除过高的寄生电容。开口尺寸通常设计为能提供刚好足够的边缘电容,以将连接焊盘的阻抗恢复至其目标值。图11 描述了在焊盘下方移除层的技术。占位取决于第一个GND 层的位置,以及电路板中电源层的位置和数量。

针对表面贴装BNC 占位移除焊盘下方的电源层

图11:针对表面贴装BNC 占位移除焊盘下方的电源层。

图12 给出了改进的占位示例。在此示例中,移除焊盘下方所有的层。此步骤会将焊盘的特征阻抗提高到75Ω(此示例的目标阻抗)以上。为了使阻抗恢复至目标值 75Ω,在焊盘的两端增加了接地金属片。这些接地片安置在焊盘预先定义的距离处,这样就能产生刚好足够的接地耦合以实现所需的阻抗。该结构的优点是与电路板堆叠完全无关,因此可在多层电路板设计中重复使用。

针对表面贴装BNC 占位采用GND 移除和GND 保护片方法

图13:针对插入式BNC 占位在引出线上方使用GND 接地片。

图12:针对表面贴装BNC 占位采用GND 移除和GND 保护片方法。

透明的BNC 占位--插入式BNC

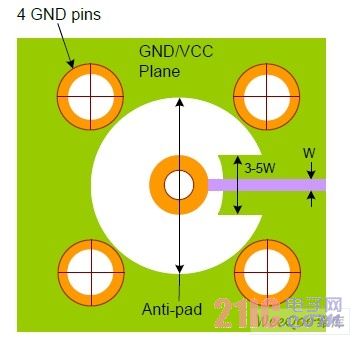

对于插入式BNC,其占位由金属化通孔及其引出线两部分结构组成。金属化通孔直径通常为30~50mil。为使金属化通孔的阻抗保持为75Ω,在电源层中需要使用大间隙(反焊盘)。反焊盘尺寸决定于金属化通孔直径以及电路板中的电源层数量。使用大的反焊盘后,反焊盘区域内的引出线将丧失其GND 参考,其阻抗就会增加。为解决此问题,需要将短金属片延长至反焊盘内,以保证引出线的阻抗。底层引出线上方的第一个电源层需要延长金属片,其宽度通常为走线宽度的3~5 倍。图13 是采用此技术的BNC 占位。另一种常用技术是加宽反焊盘区域内的引出线以降低其阻抗,图14 是采用此技术的BNC 占位。

针对插入式BNC 占位在引出线上方使用GND 接地片

图13:针对插入式BNC 占位在引出线上方使用GND 接地片。

针对插入式BNC 占位使用更宽的引出线

图14:针对插入式BNC 占位使用更宽的引出线。

图15 给出了改进的占位设计。在此示例中,底部金属层上加宽的引出线任意一侧都安置了两个GND 接地片。这些接地片安置在引出线预先定义好的位置上,这样就能产生刚好足够的接地耦合以实现短引出线所需的阻抗。该结构的优点是能独立调节电源层中的反焊盘以控制金属化通孔阻抗,且能独立调节接地保护片间隙以控制引出线阻抗。

针对插入式BNC 占位在引出线侧边使用GND 接地片

图15:针对插入式BNC 占位在引出线侧边使用GND 接地片。

BNC 占位设计优化

BNC 占位设计涉及在GND 和VCC 内层安置反焊盘或移除层,或安置表面GND 接地片,以产生刚好足够的寄生电容来保证所需的特征阻抗。占位取决于BNC 的信号引脚直径,以及电路板中的电源层数量。在某些情况下,占位可以设计成偏离标称的75Ω 以弥补BNC 本身轻微的缺陷。硬件工程师必须根据以往的经验来优化BNC 占位,在多数情况下,常常会进行多次电路板重设计。

使用三维电磁仿真可以优化BNC 占位设计。从BNC 的三维模型(机械维度和材料特性)开始, 将建议的占位结构和电路板特性(走线宽度、层叠和材料特性)输入3D EM 仿真器。执行频域仿真以确保符合有关回波损耗和插入损耗的设计目标,还可以执行仿真TDR 来检查BNC 和占位的阻抗曲线。

BNC 供应商有完整的BNC 模型,在客户输入电路板堆叠的情况下运行此仿真,是全面了解BNC 模型的最好方法之一。本部分给出的仿真示例由连接器供应商Samtec 公司提供。

Samtec 直角BNC 及其在PCB 上占位的3D 模型

图16:Samtec 直角BNC 及其在PCB 上占位的3D 模型。

BNC 及其占位的仿真回波损耗

图17:BNC 及其占位的仿真回波损耗。

BNC及其占位的仿真插入损耗

图18:BNC及其占位的仿真插入损耗。

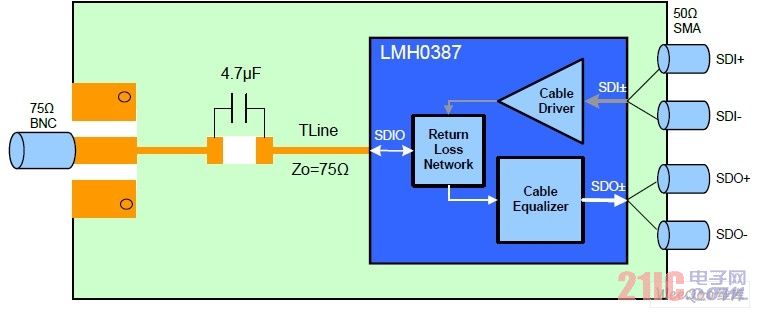

使用美国国家半导体的LMH0387测试BNC

现在已使用3D EM仿真器优化了BNC占位。为验证其系统性能,将在LMH0387*估板上采用多种BNC类型及优化占位。

LMH0387是行业首款单芯片自适应电缆均衡器和电缆驱动器,允许将一个BNC共享为输入端口或输出端口。它具有内置端接和回波损耗网络,补偿集成电路电容,并可简化高速电路板布局,以良好的裕度满足SMPTE回波损耗要求。

图19显示了此*估板的简化电路。LMH0387通过交流耦合电容器(4.7μF)连接至BNC。为达到良好的回波损耗,将LMH0387安置在靠近BNC端口的位置,并使用75Ω走线将其连接至BNC。为将阻抗的不连续性降至最低,还要为4.7μF交流耦合电容器的大连接焊盘采用接地层移除技术。

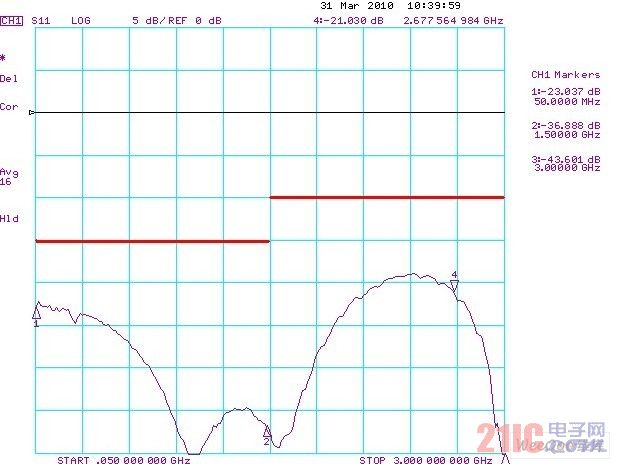

在BNC端口上将同时执行TDR阻抗测量和回波损耗测量。图20是贴装有垂直和直角插入式BNC的两块*估板示意图。图21是使用TDR为其测量的阻抗曲线。图22是其回波损耗图,表明离SMPTE的限制有5~10dB的裕度。

图23~25是边缘贴装和表面贴装BNC的另一组测量图。

LMH0387 可配置I/O 的简化示意图

图19:LMH0387 可配置I/O 的简化示意图。

LMH0387 可配置I/O 的性能图

图20:贴装有垂直和直角插入式BNC 的LMH0387 示意图。

图21:LMH0387 的BNC、占位和走线的阻抗曲线。

图22:以良好裕度满足SMPTE要求的BNC端口回波损耗图。

图23:采用边缘贴装和直角表面贴装BNC的LMH0387示意图。

图24:LMH0387的BNC、占位和走线的阻抗曲线。

本文小结

本文讨论了BNC占位设计中的几个常见问题,并介绍了透明的占位设计的几种设计方法。最佳的设计是使用具有最小信号引脚的连接器,从而无需设计任何特殊电路板结构。对于信号引脚较大的连接器,无论是边缘贴装还是插入类型,均可采用具有良好性能的受控阻抗占位。请务必使用最小的焊盘或孔。排查信号路径、逐一检查电路板结构、寻找路径中的寄生电感和电容,并找出消除过高阻抗以及将阻抗恢复至目标值的方法。

本文所用的原则不仅适用于占位设计,对其它元件的连接焊盘也同样有效。高速电路板设计不再是点A至点B的简单连接。许多细微的布局决策都会影响电气性能。三维电磁仿真工具可帮助工程师进行重要布局决策,并实现目标电气性能。时域反射计是进行电路板调试和识别阻抗变化位置的有用仪表。良好的信号发射是获得良好信号质量,以及满足回波损耗要求和电路板上其它电路要求的基本。