很久没有写博文了!确实有点过意不去。最近两个多月以来,由于公司的需要,我不得不学习Cadence16.2的使用方法——用它来画高速板子。目前白天又在忙着一块以FBGA484为核心芯片的6层板,因此只好晚上利用一些时间来写博文了。

笔者写这篇博文的初衷:一是小小地总结一下我在这两个月以来使用Cadence16.2的过程中所遇到的一些问题,并给出解决方法;二是想选几个问题,把它们写成文章,和网友分享一下,希望能给将要或者正在学习Cadence的网友提供一些好的帮助信息,少走一些弯路。

事先注明笔者所使用的子软件分别是:

(1)原理图设计软件:OrCAD Capture CIS;

(2)PCB设计软件" title="PCB设计软件" target="_blank">PCB设计软件:Allegro PCB Design GXL;

(3)Pad制作:Pad Designer;

TROUBLE ONE:从何入手?

SOLUTION:如果真想学Cadence的话,该从何入手呢?我在这里推荐一个很好的网站:http://www.sig007.com/,笔者从这个网站中得到了很多益处。只不过需要提醒的是:这个网站里讲的东西全都是针对Cadence15.7而言的,So,需要注意这两个版本之间的差异。还有就是可以逛逛Cadence的官方网站:http://www.cadence.com/us/pages/default.aspx,有时间可以去欣赏一下里面的那些Blogs,绝对称得上是:Short and to the point!

TROUBLE TWO:自建分裂元件Capture封装时该如何区分Homogeneous和Heterogeneous?

SOLUTION:刚开始接触这个软件时,笔者也是为此分不清,后来在做实际项目的过程中,终于能够加以区分并运用了。

创建分裂元件时,会出现如下对话框:

想必初学者遇到这两个英文单词时最初的“本能反应”就是努力想起或者去查询它们的中文意思。用字典软件翻译之后,可以看到它们都有若干个几个近似的意思。笔者作为“过来人”(呵呵,JK),觉得初学者完全不需要理会这些近似的意思——因为它们根本没有透露出最关键的信息。笔者觉得可以用一种更直白的方式来理解它们,

(1)Homogeneous:前缀Homo-在英语里有“同”的意思,由此可以说明这种分裂元件里的所有PART都是一摸一样的!当然除了一个参数是不同的,即

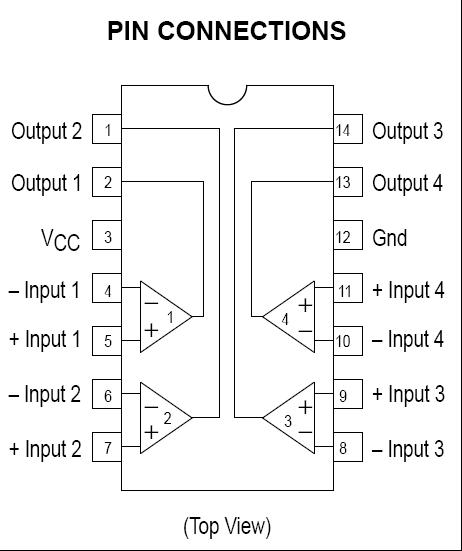

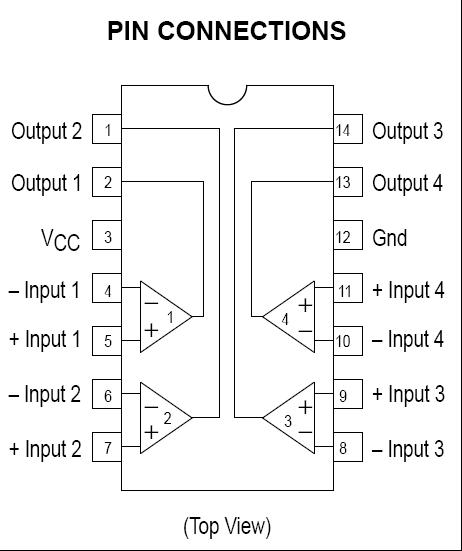

举个例子(LM339芯片):

这个比较器的芯片内部有4个完全一样的放大器,所以制作像LM339这样的元件Capture封装时,应选择Homogeneous。

(2)Heterogeneous:前缀Hetero-在英语里有“异”的意思,由此可以说明这种分裂元件里的各个PART是有区别的。其实这种TYPE更为常用,因为现实情况下内部都是相同PART的IC并不那么常见,

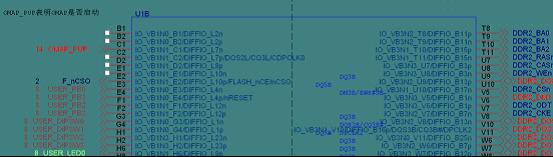

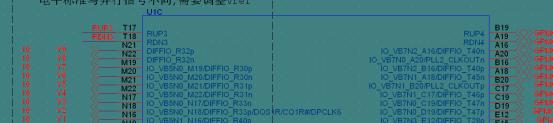

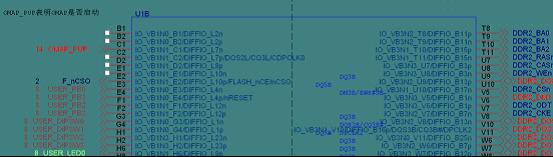

举个例子(EP3C40F484芯片),

PART B:

PART C:

笔者觉得如果要很好地区分这两种PACKAGE TYPE,最好还是亲力亲为一遍或多遍,这样印象更深刻。

很久没有写博文了!确实有点过意不去。最近两个多月以来,由于公司的需要,我不得不学习Cadence16.2的使用方法——用它来画高速板子。目前白天又在忙着一块以FBGA484为核心芯片的6层板,因此只好晚上利用一些时间来写博文了。

笔者写这篇博文的初衷:一是小小地总结一下我在这两个月以来使用Cadence16.2的过程中所遇到的一些问题,并给出解决方法;二是想选几个问题,把它们写成文章,和网友分享一下,希望能给将要或者正在学习Cadence的网友提供一些好的帮助信息,少走一些弯路。

事先注明笔者所使用的子软件分别是:

(1)原理图设计软件:OrCAD Capture CIS;

(2)PCB设计软件:Allegro PCB Design GXL;

(3)Pad制作:Pad Designer;

TROUBLE ONE:从何入手?

SOLUTION:如果真想学Cadence的话,该从何入手呢?我在这里推荐一个很好的网站:http://www.sig007.com/,笔者从这个网站中得到了很多益处。只不过需要提醒的是:这个网站里讲的东西全都是针对Cadence15.7而言的,So,需要注意这两个版本之间的差异。还有就是可以逛逛Cadence的官方网站:http://www.cadence.com/us/pages/default.aspx,有时间可以去欣赏一下里面的那些Blogs,绝对称得上是:Short and to the point!

TROUBLE TWO:自建分裂元件Capture封装时该如何区分Homogeneous和Heterogeneous?

SOLUTION:刚开始接触这个软件时,笔者也是为此分不清,后来在做实际项目的过程中,终于能够加以区分并运用了。

创建分裂元件时,会出现如下对话框:

想必初学者遇到这两个英文单词时最初的“本能反应”就是努力想起或者去查询它们的中文意思。用字典软件翻译之后,可以看到它们都有若干个几个近似的意思。笔者作为“过来人”(呵呵,JK),觉得初学者完全不需要理会这些近似的意思——因为它们根本没有透露出最关键的信息。笔者觉得可以用一种更直白的方式来理解它们,

(1)Homogeneous:前缀Homo-在英语里有“同”的意思,由此可以说明这种分裂元件里的所有PART都是一摸一样的!当然除了一个参数是不同的,即

举个例子(LM339芯片):

这个比较器的芯片内部有4个完全一样的放大器,所以制作像LM339这样的元件Capture封装时,应选择Homogeneous。

(2)Heterogeneous:前缀Hetero-在英语里有“异”的意思,由此可以说明这种分裂元件里的各个PART是有区别的。其实这种TYPE更为常用,因为现实情况下内部都是相同PART的IC并不那么常见,

举个例子(EP3C40F484芯片),

PART B:

PART C:

笔者觉得如果要很好地区分这两种PACKAGE TYPE,最好还是亲力亲为一遍或多遍,这样印象更深刻。

TROUBLE THREE:倘若原理图结构非常大,如何更加有效率地添加元件的Footprint信息?

SOLUTION:在这种情况下,如果一个一个地给元件添加Footprint信息,那将是非常耗费时间的。笔者发现了一个操作方法,可以大幅提高工作效率。

方法如下:在OrCAD Capture CIS的File界面下,

鼠标单击DSN文件或者相应的PAGE文件,并且鼠标右击,选中其中的Edit Object Properties选项,出现如下对话框:

可以看见里面有一列“PCB Footprint”,这样就可以成批量的添加元件的Footprint信息了。

SOLUTION:有些情况下,我们在布局、布线的时候可能会遇到有的Pin Header中的PIN引脚是可以任意顺序的,但是在布线时我们所看到的大都是非常杂乱无章的飞线,为此,笔者可以提供一个好的方法来解决这个问题:先在OrCAD Capture CIS里修改Netlist,然后再导入Allegro。However,需要注意的是,只能在原理图中改变Pin Header中PIN的顺序,千万别改变与之相连的芯片的引脚序号(当然还是有特殊情况的)!这个应该不难理解,就不多说了。

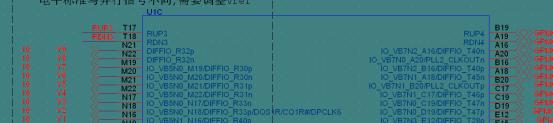

举个例子:一个六层板最初导入Netlist后的局部飞线情况如下,

但是在修改了Netlist之后,结果发现布线非常简洁,同时也有效地减少了板子过孔的数量,如下图所示,

其次还有一种方法,那就是Highlight和Dehighlight的使用方法,在布局、布线时可以人为特意将某些相同的Net高亮显示,这样可以对整个布局达到一目了然的效果。

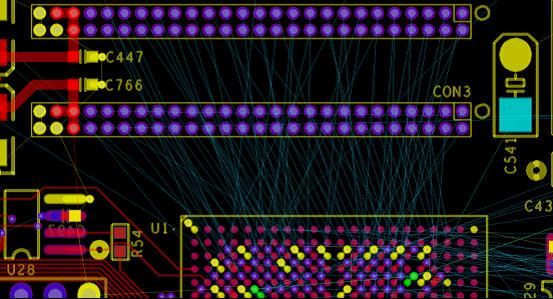

TROUBLE FIVE:由于Allegro自带的元件PACKAGE比较少,远远不能满足实际项目的需求。这么多的元件PACKAGE需要画,而且相当花费时间,有没有更好的办法来解决这个问题呢?

SOLUTION:方法是有的,现给出具体步骤,

首先,打开一个BRD文件,在Allegro界面环境下,点击File,选择Export,在下拉列表中,再选择Libraries,出现如下对话框,

然后设置导出封装库的路径,最后,点击Export就Okay了,接下来就可以免费享用别人画的PACKAGE了。“更狠”的做法就是:到一些大公司(比如ALTERA)的网站上去下载那些十几甚至几十层的REFERENCE BOARD的BRD文件,然后再EXPORT其中的封装信息,到那时,您将拥有享用不尽的元器件封装了!哈哈~~有点夸张。

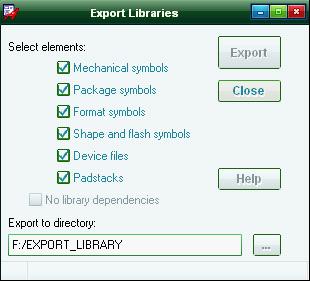

TROUBLE SIX:Generating Artwork时,能不能简化其步骤?

SOLUTION:之前在做一个板子,投出去后,PCB生产厂家反馈回一个问题,说是导出的ARTWORK文件有点小问题——有些元器件的VALUE值没有显示出来,如下图所示,

收到这个问题后笔者立即着手解决。后来发现了一个非常简便的方法,笔者自己也是对此意想不到,无意中发现的,呵呵。具体步骤如下:

在Allegro界面环境下,鼠标点击Add,选择其中的Text选项,Then,把Class和Subclass分别设置为Component Value和Assembly_Top(或者Assembly_Bottom),再点击所要添加VALUE值的相应Symbol,输入具体值就完事了。

其实这种方法可以有多方面的应用场合,尤其是ARTWORK文件生成。也许还有别的SOLUTION,但是按这种方法修改ARTWORK信息的话,应该是最简便的了。

小结:在使用Cadence16.2画板子的过程中确实遇到了比较多的问题,大部分的问题笔者都已经有效地解决了。由于文章篇幅所限,很多基础性的东西都没做涉及,只是针对软件的使用方法选取了其中6个离散的问题作了阐述,并没有涉及EMC相关的问题。今后有时间笔者将再针对PCB板级设计以及EMC方面的东西,写成博文和网友分享。