多功能调制芯片Stel-1109的原理及应用

2009-02-05

作者:李维英 张 睿 薛亦冰

摘 要: 对多功能调制芯片Stel-1109的功能、原理及内部结构做了较详细的介绍,并给出了在高速正交调制中的应用实例。在该系统中,应用Stel-1109的QPSK调制方式,实现了高速正交扩频编码和调制。

关键词: QPSK调制 扩频通信 多进制正交扩频

随着通信技术的快速发展,单一的调制方式和通信速度已经越来越不适应发展的要求。因此一些具有多种调制方式以及通信速率可变的芯片相继产生了。Stel-1109就是其中之一,它是一种高集成度、高灵活性、支持突发传输的高速全数字调制芯片,可实现BPSK、QPSK、16QAM等调制方式,主频高达165MHz,最高输出中频65MHz,数据速率可达10Mbps(BPSK)、20Mbps(QPSK)、40Mbps(16QAM)。该器件使用3.3V电压,但可接收5V的控制输入信号。内部有58个可读写寄存器,用来设置芯片的工作状态、调制方式、数据速率、编码方式等。自身带有10bit的D/A变换器,将调制之后的数字信号直接转换为模拟中频信号,使用十分灵活方便。

1 Stel-1109内部组成

图1给出Stel-1109的内部结构,主要由数据通路和控制单元组成。数据通路由比特编码、码元变换、两个数据滤波通道(I、Q)组成。每个通道都包含有Nyquist滤波器、内插滤波器和调制器。控制单元由总线接口单元(BIU)、时钟产生器和数控振荡器(NCO)组成。

1.1 数据通路介绍

1.1.1 比特同步模块

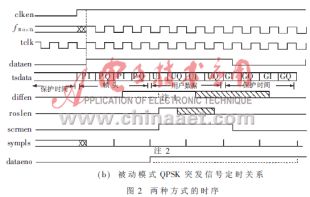

比特同步模块的作用就是锁定输入数据并使其与比特时钟同步。同步有两种方式:外部数据被Stel-1109内部比特时钟的下降沿锁定,称为主动方式;外部数据由外部时钟上升沿锁定,称为被动方式。当为主动方式时,fBitclk受clken控制,当clken为低电平时,fBitclk没有输出。图2给出两种方式的时序。

1.1.2 比特编码模块

比特编码模块接收来自比特同步输出的数据流,且由数据使能信号dataen控制数据流的输入。该模块可实现扰码(Scrambler)编码和R-S(Reed-Solomon)编码,并分别有两个使能控制信号scrmen和roslen控制编码的选择。这些使能信号既可由硬件产生,也可通过软件对相应寄存器配置来实现对编码功能的允许和禁止。扰码编码长度24位,由初始码和掩码两部分组成,根据系统要求确定生成多项式,并计算得到掩码的值。而初始码和掩码分别写入寄存器R30H~R32H和R33H~R35H。

1.1.3 码元变换单元

该单元如图3所示,包含比特变换、差分编码、码元变换。它将比特编码输出的串行数据比特变换成为码元,不同的调制方式每个码元的比特数不同。

比特变换单元将串行数据比特变换为码元比特,(每个码元包括四个输出比特I1、I0、Q1、Q0)。对于BPSK调制方式,输入的每比特b0对应的码元变换结果为I1=I0=Q1=Q0=b0,即四个比特相等。对于QPSK调制方式,则每两个比特(b1、b0)形成一个码元,变换结果为I1=I0=b0,Q1=Q0=b1或者为I1=I0=b1,Q1=Q0=b0两种组合。对于16QAM调制方式,每四个比特形成一个码元,根据I、Q的次序共有八种组合。而码元变换则根据选定的调制星座图把码元比特映射成为相应的星像点,这些选择都可通过配置相应的寄存器进行选择。

1.1.4 有限脉冲响应滤波器和内插滤波器

有限脉冲响应滤波器(FIR)的主要作用是使经过滤波器后的信号边带频谱最小。它是具有32个抽头的线性相位响应对称滤波器,根据系统带宽要求确定滤波特性,从而计算出滤波系数。有16个10bit的可编程系数寄存器,以2进制补码形式储存滤波系数值,范围为-512到+511。

内插滤波器是3阶可编程滤波器,它把信号采样速率提高到与主时钟频率相同,从而平滑数据信号,滤除寄生的频谱。通过编程可改变滤波器的内插因子和增益。

1.2 控制单元介绍

1.2.1 总线接口单元

总线接口单元包括58个可编程寄存器以及控制信号。rst是主复位信号,低有效,复位所有可编程寄存器。dsb、csel、wr控制信号完成存取操作,均为低有效。csel为片选信号,wr为读写控制信号,wr为低时是写寄存器状态,反之为读寄存器状态。dsb是写控制信号,当片选信号csel有效且写信号wr为低时,dsb信号由高变低之时,写过程开始,在它变高之时,写过程结束。

1.2.2 时钟产生单元

辅助时钟fAclk:在stel-1109内部,对于比特时钟(fBitclk),用时钟使能信号(clken)来控制,当clken为低时,fBitclk没有输出,因此需一个辅助时钟完成一些辅助操作,这一点在系统工作中很重要。其表达式如下:

其中,2≤N≤15,改变参数N可输出所需的频率。

比特时钟fBitclk:fBitclk是1109内部定时的标准信号,也可作为外部数据的定时信号,其表达式如下:

其中,3≤N≤4095。当为16QAM调制时,K=1;当为QPSK调制时,K=2;当为BPSK调制时,K=4。

数控振荡器:产生调制用的正交中频信号fCARR,由fcwsel[1..0]控制可产生三种频率信号。其表达式如下:

其中,FC是编程计数值。

以上简要介绍了Stel-1109的内部结构和重要参数的设置,有兴趣的读者请参考有关资料。

2 在多进制正交扩频编码和调制中的应用

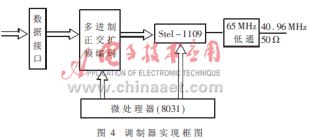

图4示出了多进制正交扩频编码和QPSK调制实现的原理框图。微处理器8031完成对系统的初始化,包括对Stel-1109芯片工作参数的配置和FPGA初始参数的装载。同时微处理器还实现发送时序的产生以及系统的控制。多进制正交扩频编码是由FPGA和EPROM实现的。

Stel-1109设置为QPSK调制方式,主频163.83MHz,fBitclk=8.192MHz,分频系数N=9,码元速率为4.096MHz,中频输出为40.96MHz。其地址和数据总线直接与系统控制单元接口,对其内部寄存器进行编程。可编程寄存器用于设置调制方式、码元速率、成形滤波器参数、内插滤波器因子及增益、输出中频频率等参数。数字信号经由D/A变换后输出中频模拟信号送至滤波器。Stel-1109接收来自数据终端的数据流并进行比特变换,将数据流比特b1和b0转换成为码元比特I[1:0]和Q[1:0]。码元转换单元将码元比特根据调制星座图变换为星象点。I[1:0]和Q[1:0]两支路数据经滤波后分别进行正交调制,合成QPSK调制信号,通过低通滤波器输出到电台中频输入口。

3 实验结果

该系统用于高速无线分组网中,扩频码片速率为4096kHz/s,图5示出多进制正交扩频码经过QPSK调制输出的中频波形包络及其频谱图。图5(a)所示为QPSK调制信号。该信号经过Stel-1109内部滤波器滤波后,包络有一定的起伏。图5(b)所示为其频谱,纵坐标每格10dB,模坐标每格2MHz。该信号经中频对接后用QPSK方式解调,已能正确解扩和解调,证明设计方案是正确可行的。

由于该系统应用了Stel-1109及FPGA等一系列新型器件,使得系统硬件大为简化。特别是高速调制电路和高速DAC,用单元电路的实现受目前器件速率的限制以及分布参数的影响,实现起来困难较大,因此在一些高速或者复杂系统中应用Stel-1109就显得更加方便有效。

参考文献

1 薛筱明,李建东.多进制正交码扩频系统的解扩和同步技术及其实现.电子学报1998(1):105~110

2 Stel-1109 Data Sheet. Stanford Telecom,1997