摘 要: PWM模拟DAC技术由于其价格便宜、技术简单在低成本嵌入式系统中应用广泛,然而其性能指标却无法与集成的DAC相比。建模讨论了影响PWM模拟实现DAC系统的性能的主要因素。仿真发现,滤波器环节对于PWM模拟DAC的性能参数是至关重要的,在不考虑PWM的位数限制时,滤波级数越高DAC精度越高,然而DAC的建立时间也会显著增加。分析发现,这两个主要参数分别取决于滤波系统对于高频成分的频率响应和对于直流分量的阶跃响应。具体应用中应该权衡DAC精度和转换速度,以确保应用PWM模拟DAC可以满足具体应用需求。

关键词: PWM;模拟DAC;系统响应分析;DAC精度;DAC建立时间

0 引言

随着电子信息技术的发展,越来越多的领域需要DAC(数模转换器)[1]。然而对于很多低成本的简单嵌入式系统而言,DAC的价格过于昂贵,因此使用PWM(脉冲宽度调制技术)模拟DAC成为很多对于DAC性能要求不高的低成本嵌入式系统的极好选择[2-3]。

PWM技术是通过对一系列脉冲的宽度进行调制,来等效地获得所需形状和幅度的波形。通过PWM,微处理器可以很方便地用数字输出来对模拟电路进行控制,因此PWM技术广泛应用在从测量、通信到功率控制与变换的许多领域中。

目前大部分微控制器都集成了PWM功能模块,PWM模拟DAC技术也已经比较成熟[4],然而对于PWM模拟的DAC性能参数却很少有人讨论,导致设计主要凭经验和仿真与实验。本文将重点讨论DAC的精度和建立时间这两个主要性能参数,建模仿真并分析影响这两个参数的因素,为PWM模拟DAC设计提供指导。

1 PWM模拟DAC的原理与实现

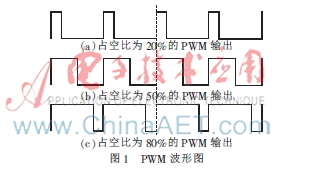

图1显示了3种不同的PWM信号。图1(a)是一个占空比为20%的PWM输出,即在信号周期中,20%的时间通,其余80%的时间断。图1(b)和图1(c)显示的分别是占空比为50%和80%的PWM输出。对PWM波形进行分解就可以发现它包括一个直流量、与PWM同频率的频率分量和大量偶次谐波,其中这个直流分量就是供电电压乘以PWM占空比。这3种PWM输出波形对应的直流分量的强度分别是供电电压的20%、50%和80%。例如,假设供电电源为5 V,占空比为50%,则对应的是一个幅度为2.5 V的模拟信号;占空比为80%,则对应的是一个幅度为4 V的模拟信号。占空比与输出电压形成一一对应关系,这样就实现了DAC的功能。

然而若想将这样的PWM波形转化成具有较高精度的直流模拟信号需要衰减交流成分。也就是说要在PWM输出的基础上加上合适的低通滤波环节,该滤波器截止频率显然要低于PWM频率,而滤波器的结构和参数的选择将成为PWM模拟DAC参数优劣的关键。

2 PWM模拟DAC系统结构仿真设计

为了重点分析滤波环节对于DAC参数的影响,在这里做了如下假设:PWM位数无限大,供电电源没有纹波。

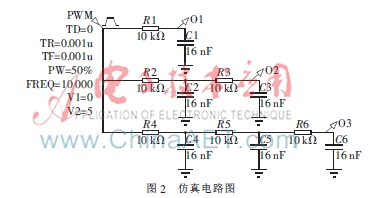

图2所示为3个PWM模拟DAC的仿真电路图,输出分别为O1、O2和O3,它们之间的单元结构都是相同的,区别仅在于单元级数依次递增。初期的实验表明PWM占空比为50%时输出的纹波基本达到最大,而整个波形稳定的时间没有明显地随占空比的不同而变化。因此在这里取PWM的占空比为50%,频率为10 kHz,上升时间和下降时间均取1 ns,高电平为5 V,低电平0 V,而相应的滤波电路的一个基本RC单元的截止频率约为1 kHz。

图3所示为3个滤波电路输出的瞬态波形。可见,O1的纹波呈现正弦波形,峰峰值780 mV,幅度390 mV,直流平均值为2.50 V,电压稳定时间约为1.0 ms;O2的纹波呈现正弦波形,峰峰值53 mV,幅度26.5 mV,直流平均值为2.50 V,电压稳定时间约为2.5 ms;O3的纹波呈现正弦波形,峰峰值4 mV,幅度2 mV,直流平均值为2.50 V,电压稳定时间约为5.5 ms。

DAC的精度(Accuracy)是指DAC的输出与理想情况的偏差。示波器显示纹波基本对称,可以得到各个电路对应的精度就是纹波的幅度,即O1的精度A1为390 mV,O2的精度A2为26.5 mV,O3的精度A3为2 mV。可见随着滤波级数的增加DAC精度显著改善。

在相应的精度条件下,若区分出相邻两个DAC阶梯电压的话必须满足精度小于LSB/2。由于电源电压为5 V,则PWM模拟DAC的电压级数可以表示为N=5 V/LSB≤5/(2 A)。由此可见:O1输出结果的电压级数N1≤6.4,可以等效一个2~3位的DAC;O2输出结果的电压级数N2≤94,可以等效一个4~5位的DAC;O3输出结果的电压级数N3≤1 250,可以等效一个10~11位的DAC。可见随着滤波级数的增加DAC的位数快速提高。

建立时间是DA非常重要的性能指标,定义为输入数字量发生变化时,输出模拟量稳定到标称精度内所经历的时间[5]。为了对比3种情况下的PWM模拟DA的性能,在这里LSB取最小值,也就是LSB=2 A,此时DAC的建立时间Tb就等于电压波形稳定到2.50 V+-LSB/2的时间,也就是上面提到的稳定时间,即O1的DAC建立时间Tb1=1.0 ms,O2的DAC建立时间Tb2=2.5 ms,O3的DAC建立时间Tb3=5.5 ms。可见随着滤波级数的增加DAC的建立时间明显变长。

3 仿真结果分析

从仿真结果可以看到,经滤波器输出的波形中含有大小不等的纹波成分,这主要是因为对于频率为10 kHz的PWM波形而言,其频谱主要包含直流分量和10 kHz基频成分,此外含有大量偶次谐波分量频率成分,低通滤波器为非理想滤波器,无法完全将高频成分滤除。为了更清晰地了解电路系统的行为,有必要分析系统对PWM波形的分量成分响应特性。

3.1 频率响应与DAC纹波的关系分析

由图3可以看到,3个不同级数的滤波器输出的波形中含有不同幅度的纹波,而纹波的频率为10 kHz,可见滤波电路对于10 kHz的响应是起决定作用的。图4所示为3个滤波电路的频率响应。由图4可以看到,虽然滤波器对10 kHz成分起到了一定的衰减作用,但是O1在10 kHz位置衰减只有-20 dB,O2在10 kHz位置衰减了-40 dB,O3在10 kHz位置衰减了-60 dB,后者比前者衰减多达20 dB,再考虑到对于其他的高频谐波分量的衰减三者差距更大,可以得出这样的结论:O1的纹波幅度大于10倍的O2纹波幅度,O2的纹波幅度大于10倍的O3纹波幅度。这与O1与O2的纹波幅度的倍数关系(390 mV/26.5 mV=14.7)和O2与O3的纹波幅度的倍数关系(26.5 mV/2 mV=13.25)是一致的,可见这是造成O2纹波显著低于O1而O3纹波又显著低于O2的原因。显而易见的是,如果增加同样的滤波结构的级数,是可以很明显地减小纹波的。

3.2 阶跃响应与DAC建立时间的关系分析

以上分析了滤波系统对于高频成分的频率响应,下面看一下系统对于直流分量的阶跃响应。在这里仍选择2.5 V阶跃响应,以2.5 V的阶跃函数作为激励源。系统阶跃响应输出如图5所示。

从图5可以看到,电路对于目标电压的阶跃响应曲线与PWM模拟DA输出曲线的轮廓重合,可以认为系统的阶跃响应和高频谐波频率响应决定了PWM模拟DA的输出响应曲线。而其中阶跃响应是决定DA建立时间的最关键因素,与之相比其他因素几乎可以忽略。

4 结论

本文建模讨论了PWM模拟实现DA系统的主要性能参数。仿真发现,滤波器环节对于PWM模拟DA系统的性能参数是至关重要的:在不考虑PWM的位数限制时,滤波级数越高分辨率也可以越高,然而DA的建立时间也会显著增加。分析发现,两个主要参数分别取决于滤波系统对于高频成分的频率响应和对于直流分量的阶跃响应。具体应用中应该权衡需求中的DA精度和转换速度,以确保应用PWM模拟的DA系统可以满足具体应用需求。

参考文献

[1] 张仁民,钱莹晶,伍清.一种手持式波形采集、存储及回放系统[J].微型机与应用,2013,32(3):85-87.

[2] MASUDA T, UEKI M. Digital-to-analog converter using pulse-width modulation: U.S. Patent 5,148,168[P]. 1992-9-15.

[3] 左现刚,张志霞.基于AVR单片机的数控直流稳压电源的设计[J].微型机与应用,2012,31(8):84-86.

[4] HIORNS R E, BOWMAN R G, SANDLER M B. A PWM DAC for digital audio power conversion: from theory to performance[C]. International Conference on Analogue to Digital and Digital to Analogue Conversion, 1991, IET, 1991: 142-147.

[5] 尹泽,庄奕琪.D/A转换器建立时间对输出信号质量的影响[J].计量学报,2005,26(2):181-184.