文献标识码: A

文章编号: 0258-7998(2015)02-0035-03

0 引言

人的视网膜感受光信号刺激后,将会诱发一系列源于视觉传导通路及枕叶视皮层的电生理活动,即视觉诱发电位(Visual Evoked Potential,VEP)[1]。在低刺激率(<3rev/s)下,会诱发暂态视觉诱发电位(transient VEP,tVEP)。而当刺激率提高(>7rev/s),视觉诱发电位会出现稳态反应(Steady-State VEP,SSVEP)[2]。Bobak的研究表明,tVEP和SSVEP是由大脑不同生理通道处理产生[3]。Herrmann认为,SSVEP反映了受刺激信号驱动的神经节律现象[4]。另外,SSVEP在神经视功能的评估方面有广阔的应用前景,是当前视觉诱发电位领域的研究热点。

在研究SSVEP的实验中,需要给予受试者一个高频率的视觉刺激信号,并保证刺激图像和触发信号的同步性与准确性。视觉刺激器产生用于VEP检查的视觉刺激信号,传统的刺激器主要有两种:(1)基于单片机的视觉刺激器,其原理是利用单片机输出刺激图像。其性能稳定,但单片机内部资源有限,变更刺激模式困难;(2)基于PC的视觉刺激器,是通过PC上的软件编程实现图像刺激。其优点是方便修改代码,能灵活地产生不同刺激模式。但因刺激器需运行在多任务操作系统下,其时间精度有赖于CPU性能及对硬件的调度。刺激器在产生高频图像刺激时,图像刺激和触发信号会出现延时[5],导致同步性变差。在本实验中采用MATLAB产生高于30 rev/s的图像刺激,出现图像失真和触发信号延迟。可见,单片机方式的不灵活和软件方式的同步性差不能满足目前SSVEP研究对刺激器的要求。

本文设计一种基于FPGA的高频视觉刺激控制器,从串口接收刺激模式命令,在由FPGA控制生成刺激图像的同时,向采集设备发送触发信号。测试结果表明,本文设计的高频视觉刺激器能灵活地变更不同的刺激模式,并确保了高刺激率下刺激图像和采集信号的完全同步。

1 系统整体设计

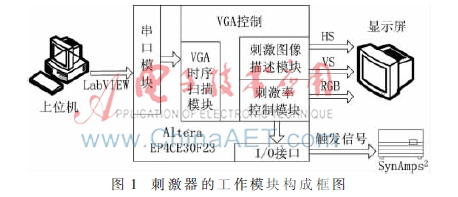

本文设计的高频视觉刺激控制器采用Altera公司的EP4CE30型FPGA芯片作为主控器件。整个视觉刺激器包括硬件和软件两个部分:(1)系统硬件部分,主要采用一块FPGA电路板,包括串口电路、VGA接口电路、按键电路及I/O口等外围电路;(2)系统软件部分,主要是由硬件描述语言设计的FPGA程序组成,包括串口通信模块、VGA时序扫描模块、刺激图像描述模块及刺激率控制模块。

刺激器工作原理如图1所示,视觉刺激器上电后,读取预置的配置文件完成硬件系统初始化。上位机通过LabVIEW编写的用户界面向串口发送刺激模式的选择信号至FPGA芯片。在串口模块解析完上位机的控制指令后, VGA控制模块按所选的刺激模式开始行扫描和场扫描,在刺激图像描述模块中生成所需的刺激图像,并在刺激率控制模块中产生相应的刺激率信号及触发信号,再将触发信号发送到FPGA板上I/O口,经并行接口送至诱发电位采集设备,并把RGB、行同步及场同步信号发送给VGA接口,通过接口上连接的显示器向受试者给予视觉诱发刺激。目前对于通过本刺激器所诱发的数据采集利用美国NeuroScan公司的SynAmps2系统,此系统需要接收一个来自刺激器的触发信号(脉冲信号),用于标记视觉刺激的开始位置。

2 系统核心控制模块

FPGA控制程序是本系统的核心部分,本文根据模块化设计方法把系统划分为串口通信模块、VGA时序扫描模块、刺激图像描述模块及刺激率控制模块四大模块。然后把实例化的子模块连接起来,组成一个完整的系统。

2.1 串口通信模块

上位机和刺激器间的通信通过串口通信模块实现。串口通信模块包括波特率发生器、发送器和接收器3个子模块。波特率发生器模块根据串口协议,负责对系统时钟(50 MHz)进行5 208个计数定时,分频得到读写波特率9 600 b/s(1×5 208/50 MHz≈1/9 600 s)。

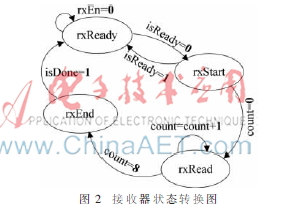

发送器和接收器属于串口通信模块,主要负责接收上位机的控制命令并根据协议反馈握手信号。本串口模块的帧数据每隔1个读写时钟读写1位,遵循读写次序为1位起始位、8位数据位、1位校验位与1位停止位[6]。模块采用状态机的方式来实现。以接收器为例,分别以rxReady、rxStart、rxRead、rxEnd标识 4个状态。图2为接收器状态转换图, 状态rxReady判断信号rxEn为低电平就决定状态机的开始,并进入rxStart状态,判断信号isReady为低电平就标记帧数据的起始位并进入状态rxRead,利用计数器count循环读取8位有效数据,最后状态rxEnd负责延时两个读写时钟信号而忽略校验位和停止位,并输出isDone接收完毕信号。数据接收完后,状态机重新进入rxReady状态等待下一个帧数据的接收。

2.2 VGA时序扫描模块

本模块中主要是通过对系统时钟进行PLL锁相倍频得到VGA的扫描时钟[7],再通过行同步和场同步信号控制CRT显示器的阴极射线枪发射电子束,按设定的时序打在涂有荧光粉的荧光屏上,产生红绿黄三基色,合成1个彩色像素。扫描从屏幕左上角顶点开始,从左往右,从上到下逐点扫描。每扫描完一行,电子束需要回到屏幕的左边下一行的起始点,此时就要用行同步信号对电子束消隐,避免电子束损坏屏幕图像;扫描完所有行,再由场同步信号进行消隐,让电子束重新回到屏幕左上角顶点,同时需要行消隐,准备下一场的扫描。VGA显示器有800×600@60 Hz、1 024×768@85 Hz等多种显示标准,以1 024×768@85 Hz说明VGA时序扫描的原理,此VGA标准下时序技术参数如表1所示[7]。

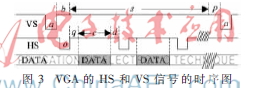

行同步信号HS和场同步信号VS的时序图如图3所示。HS先拉低96个脉冲周期(以o表示)后再被拉高,即行消隐时间;经过208个脉冲(以q表示)后,DATA数据有效,即显示器开始扫描1 024个列像素点(以c表示),扫描完成到下一次HS再次被拉低,中间经过48个时钟脉冲(以d表示)[8]。扫描一行的数据帧长为1 376。同样,VS类似HS的扫描方式。VS先拉低3个行周期(以a表示)后再被拉高,延迟36个行周期(以b表示)后行再被拉低,这样开始扫描这一帧的数据,经过1个行周期(以p表示),完成全帧扫描后VS再次被拉低重复上述过程。

2.3 刺激图像描述模块

本模块把显示屏看作一个直角坐标系,原点在屏幕左上角,通过列计数器Hcnt和行计数器Vcnt,定义扫描有效显示区域的行和列坐标变量Haddr和Vaddr,通过直接对不同坐标地址赋予不同的颜色值,产生视觉诱发电位实验所需刺激图像,如水平光栅、垂直光栅和棋盘格等。

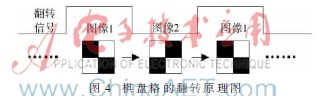

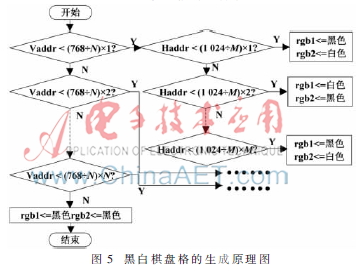

以棋盘格刺激图像为例,刺激器是通过生成同位置黑白相反的两幅棋盘格图像,按照翻转信号的高低电平变化将两幅棋盘格RGB信号轮流发送给VGA端口。如图4所示,翻转信号在高电平时显示图像1,反之,在低电平时显示图像2,因此实现两幅棋盘格翻转的效果。棋盘格生成流程如图5所示,图中M、N分别代表棋盘格的水平和垂直的格数,寄存器rgb1和rgb2分别负责寄存两幅棋盘格中不同位置的颜色值。

2.4 刺激率控制模块

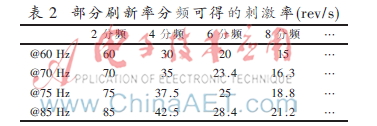

一个翻转周期(cycle)包括两个颜色相反的图像翻转,而翻转频率指每秒钟翻转(reversal)的次数(rev/s)。两者关系可以表示为1 Hz相当于2 rev/s[2]。本刺激器中刺激率指每秒的翻转次数,是通过对VGA时序扫描模块产生的场同步信号分频得到。场同步信号即VGA工业技术上的刷新率。如图6所示,翻转信号和触发信号产生原理是通过捕捉VS的下降沿时刻,本模块就按设定的分频数生成一个方波信号,即翻转信号。同时,在方波信号发生高低电平变换时刻,即图像每次翻转时同步产生一个脉冲信号,即触发信号。这样的实现方式保证了VS和翻转信号的时钟同源,从而确保刺激图像的正确显示。比如,60 Hz二分频得30 Hz(60 rev/s)。由VESA公布的VGA时序[7], 表2举例部分刷新率分频可得的刺激率。由表2可看出本刺激器已可实现高于30 rev/s的刺激率,并随着得到更高刷新率的时序技术参数,就能实现更高的刺激率。

3 刺激器测试结果

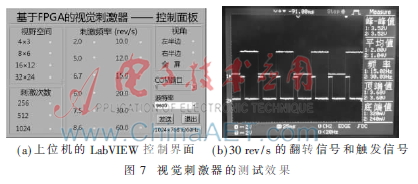

本文选择显示标准为1 024×768@60 Hz进行测试,通过JTAG口把编译成功的FPGA程序烧录到板上Flash芯片中,采用19寸CRT显示器(EIZO T761)作为刺激视屏。

测试结果如图7所示,图7(a)是上位机的控制界面,参数选择包括视角、视野空间、刺激次数和刺激率。图7(b)为高刺激率30 rev/s时示波器的检测情况,示波器通道1显示翻转信号波形,通道2显示触发信号波形,通道1高低电平切换时刻与通道2高电平开始时刻完全一致,这说明了图像刺激与触发信号完全保持同步性。

4 稳态视觉诱发电位测试实验

为测试本视觉刺激器在高刺激率下的有效性,本文进行了一个高刺激率的视觉诱发电位测试实验。

实验方法和步骤均严格按照视觉诱发电位实验标准要求[9],利用本刺激器生成20、30和60 rev/s等3个高频刺激信号,对1名受试者进行以上3个高刺激率的视觉诱发电位测试实验。文献[2]提到,SSVEP波形是一个类似正弦曲线的波形,且频率固定。利用MATLAB处理通过SynAmps2系统采集所得数据并分别画出SSVEP波形图,如图8所示。从图可清晰看出,3个SSVEP波形都是类似正弦曲线的周期性波形,即受试者在3个高刺激率下,视觉系统都有效地诱发出视觉稳态反应。

由刺激器测试结果和视觉测试实验证明,本文设计的基于FPGA的高频视觉刺激控制器能满足稳态视觉诱发电位的实验要求,不但顺利完成高刺激率下刺激图像的准确呈现及触发信号的同步发送,成功诱发出有效稳态觉诱发电位,并且具有操作方便、刺激模式丰富、可扩展性强的优势。

参考文献

[1] 黎宇飞,刘技辉,陈晓雷,等.不同刺激野的图形翻转视觉诱发电位[J].法医学杂志,2009,25(1):15-18.

[2] ALMUDENA C,PAULA P A,CAMPO P,et al.Steady-statevisual evoked potentials can be explained by temporal superposition of transient event-related responses[J].Plos One,2011,6(1):e14543.

[3] BOBAK P,FRIEDMAN R.Visual evoked potentials to multi-ple temporal frequencies.Use in the differential diagnosis ofoptic neuropathy[J].Arch.of Ophthalmol,1988,106(7):936-940.

[4] HERRMANN C S.Human EEG responses to 1-100 Hz flicker: resonance phenomena in visual cortex and their potential correlation to cognitive phenomena[J].Experimental Brain Research,2001,137(3-4):346-353.

[5] 程光辉,石锐,何庆华.Windows环境下脑机接口视觉刺激器的设计[J].计算机工程与应用,2006,42(13):175-177,193.

[6] 王永成,党源源,徐抒岩,等.基于cpld实现dsp的uart设计研究[J].电子器件,2008,31(3):1066-1068,1072.

[7] Video Electronics Standards Association.VESA and industry standards and guidelines for computer display monitor timing[Z].2004.

[8] 姜世杰,余红英,洪永学,等.基于FPGA的VGA接口驱动技术[J].电子测试,2012(12):29-32,71.

[9] ODOM J V,BACH M,BRIGELL M,et al.ISCEV standard for clinical visual evoked potentials (2009update)[J].Docu-menta Ophthalmolgical,2010,120(1):111-119.