文献标识码: A

文章编号: 0258-7998(2015)02-0075-03

0 引言

近年来,随着航空、航天、测控等技术的迅速发展,相关行业对数据采集系统的性能要求更加苛刻,要求能够同时采样的通道更多,采样的精度和速度要求更高,因此研制开发了一套高性能数据采集系统。该系统较以往开发的数据采集系统,在设计方案、操作界面等方面均有了较大改进,如该系统采用PCI总线,传输速率得以大大提高,系统软件运行于Windows操作系统下,较以往该领域的Dos系统,在操作上更方便,界面更友好。整个系统具有高精度、高采样速率以及多通道且通道数可变的突出特点,本文介绍了该数据采集系统的设计与研制方案。

1 系统的总体设计方案

系统具体工作要求:有62路通道可以供用户采集转换使用,具体采集1~62路中的任意多个通道及这些通道的编号分别是多少等信息由用户根据需要通过上位机传送给本系统,即本系统要根据上位机的具体信息完成用户的任务;另外为了达到相关指标的要求,A/D分辨率应达到14位。从要求可以看出本系统具有采集路数和路号可变、精度高、速度快的突出特点。针对这些特点,选用凌华公司的数据采集卡(DAQ-2010)作为采集和A/D转换器件,该板卡具有4个14位精度的同步A/D通道,通过扩展可以满足62通道的要求。另外,该板卡的4个独立A/D的转换速率可达2.2 Mb/s,满足了高速采集的技术要求。作为该板卡工作的控制器,选择使用CPLD,因为CPLD具有精度高、速度快、稳定性好的特点,从而可以满足需要。本系统与上位机的通信和控制器选择的是8051核单片机,其开发技术成熟,性能完全可以满足需求,并且价格低廉,可以很好地控制成本,它们的具体连接框图如图1所示。

系统工作时,首先由用户将要选通的具体通道编号和通道数目通过工控机传递给单片机,单片机将各通道编号作为数据存放于SRAM中,并且将具体的采样要求,诸如采样频率、采样总通道数等信息传给CPLD。而后CPLD独立输出SRAM的地址来轮巡所要采集的通道。每当一个通道开通,传感器和电压端子盒将被测系统的电流信号或电压信号汇集到信号控制箱,然后进入信号调理板和信号转换电路,将被测信号转换为标准测量电平后,通过转接适配器进入数据采集卡,DAQ-2010数据采集卡就采集转换一次,并将转换后的数据传回给上位工控机。工控机对电压、电流、功率、相位等信号参数进行数据分析、计算、显示和存储,并套用相关标准限制曲线图形,使标准规定的极限曲线与试验数据填充曲线进行对比,以此评估被测试系统设计的精度和误差,从而实现对被测系统的实时监控。

2 系统的硬件设计

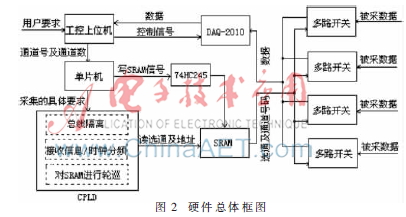

系统硬件的设计主要是围绕DAQ-2010数据采集卡进行的,诸如将数据采集卡的4个同步采样通道扩展为62通道,利用硬件描述语言开发CPLD,使其能够完成对62通道的轮巡以及总线隔离等功能。针对系统各通道要采集的电压、电流信号的不同,采用多种电压、电流传感器将原始信号转换成数据采集卡可以采集的统一形式的电信号,这样就可以为数据采集、信号处理打下有利的基础。硬件总体框图如图2所示。

2.1 通道扩展的实现

如前所述,本系统设计需要62个通道供用户使用,但DAQ-2010仅有4个独立同步A/D通道,于是采用4个16通道多路开关进行扩展,从而可以构造出64个通道可供使用,既满足了用户的要求,又可以留有两个通道作为应急或系统升级使用。

2.2 通道轮巡的实现

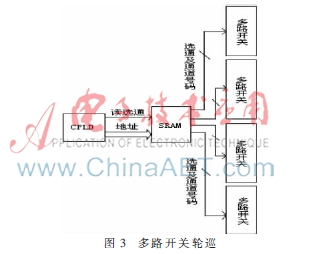

将通道扩展至62之后,如何选通通道这一任务的完成是通过对SRAM的数据进行读取实现的。具体思想是在系统开始工作时,用户根据自己的需求将需要测试的通道编号通过工控机传递给单片机,而后由单片机将通道编号作为数据写入静态存储器SRAM中,开始进行数据采集时,CPLD在内部时钟的控制下读取SRAM中的数据(即通道编号),这些编号就成为了多路开关的选通信号,随即实现了相应多路开关通道的开通,这样就完成了对所需通道的轮巡,其实现框图如图3所示。

2.3 CPLD程序设计

CPLD程序设计的任务是:

(1)接收单片机对系统工作要求的信息:如用户需要轮巡的通道数、分频数、复位信号等。

(2)对多路开关进行轮巡时,自动产生所要读取SRAM的选通信号以及它的地址信号,并根据时序要求实现轮巡。

(3)接收系统工作时钟,并且根据要求实现对系统时钟的分频。

另外值的一提的是,系统在工作时分为单片机向SRAM写数据并验证和CPLD读取SRAM中的数据两个步骤,而从单片机和CPLD引出的SRAM选通、读取、地址等控制或数据线都要与SRAM连接,这样就需要有隔离措施,使得在前一个步骤时,CPLD与SRAM间是高阻态,而当第二个步骤时,单片机与SRAM间处于高阻态。由于在硬件方面,为了控制PCB板的规格,所以CPLD与SRAM间的隔离需要编程实现。

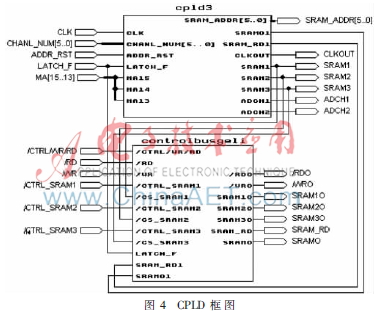

系统中最重要的时序是CPLD的工作时序,CPLD能否正常工作是整个系统的关键,要保证CPLD的工作时序清晰,不会产生混乱。CPLD选用EPM7128,使用Verilog HDL语言在MAX+PLUSⅡ环境下进行开发, CPLD的顶层程序设计模块见图4。框图左侧均为CPLD的输入管脚,包括时钟、控制读、写选通等信号,框图右侧均为CPLD的输出管脚,包括对SRAM的读信号和地址信号,其中SRAM1O、SRAM2O、SRAM3O、SRAMO、SRAM_RD等信号可以在单片机写SRAM时实现CPLD与SRAM的隔离。

正常工作时,系统的时序图如图5所示。

3 测试系统的软件设计

测试系统软件使用VC++开发,运行于Windows环境下,人机界面友好,包括系统测试软件和和系统校准软件。其中系统测试软件是在对被测系统进行测试时,具体实现对电压、电流、相位、功率、功率因数等参数的稳态和瞬态进行数据测试、数据分析和数据存储的执行软件,系统校准软件是对系统的精度进行计量的软件。

该软件包采用中文下拉菜单方式提示操作、显示、打印,自动记录和存储所有测试数据,以便于事后调出查询,观察分析,重新显示输出。测试数据套用相关标准限制曲线图形,标准规定的极限曲线与试验数据填充曲线的对比图形可同时显示打印,以便于判断测试结果是否满足设计要求。

4 结束语

本系统已经投入实际应用,经过实践证明这一系统完全满足多通道同时采样并且速度快、精度高的要求,稳定可靠,取得了很好的效果,说明了文章中所作的分析和讨论是合理和实用的。本系统可应用于高速、多通道且通道路数可变的工程应用领域。

参考文献

[1] 王育坚.Visual c++面向对象编程教程[M].北京:清华大学出版社,2003.

[2] 夏宇闻.Verilog 数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[3] 东方人华.MAX+PLUSⅡ入门与提高[M].北京:清华大学出版社,2004.

[4] 王金明,杨吉斌.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2002.

[5] BHASKER J.Verilog HDL硬件描述语言[M].徐振林,译.北京:机械工业出版社,2000.