文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.09.016

中文引用格式: 林俊明,郑耀华, 郑瑞青,等. 应用于移动手机的SOI线性射频功率放大器的设计[J].电子技术应用,2015,41(9):60-62.

英文引用格式: Lin Junming,Zheng Yaohua,Zheng Ruiqing,et al. Design of linear RF power amplifier for moblie phones based on SOI technology[J].Application of Electronic Technique,2015,41(9):60-62.

0 引言

随着信道容量急剧增加,通信系统采用多种调制方式相结合的非恒包络调制技术,这对功率放大器的线性度提出了更高要求,为了适应当前低功耗及高效率的功率放大器的要求,本文就负载线和传统功率放大器理论,设计了应用于1.95 GHz WCDMA发射机的线性功率放大器。

SOI(Silicon-On-Insulator,绝缘衬底上的硅)有着成为主流硅工艺的趋势。SOI是近十多年的新型微电子材料,可以有效解决高电压、高集成和低功耗的问题。SOI有着非常低的器件噪音和可以抑制浮体效应,对于像滤波器和选频电路等对噪音要求非常严格的电路来说,这无疑是更好的解决方案。SOI工艺可以通过将叠加MOS器件的形式来解决其耐压问题,而且它有着非常低的功耗和所有的器件都集成在一块相互绝缘的硅衬底上,并有很好的隔离作用,因此SOI工艺是实现单片射频功率放大器的一个很好的选择。

1 电路设计

功率放大器一般输出功率高而增益较低,为了输出较高增益和兼顾整体功率放大器的效率与线性度并且实现较低静态功耗,最终选择电路的拓扑结构为三级AB类放大器结构,如图1所示。

整个功率放大器除了输出匹配网络(OMN)和输入匹配网络(IMN),还有级间匹配网络(MMN),级间匹配网络可调整放大器之间的增益平坦度并使每级的效率最高。先设计输出级,最后设计输入级,且每级都必须无条件稳定。输出匹配网络将50 Ω变换成功率输出级最优阻抗的共扼,此时的匹配并不是传统的共扼匹配,因为最优输出阻抗并不是输出最大资用功率时的阻抗,这里的共扼只是为了消除MOS管的输出电容。输出匹配网络决定了放大器的输入反射系数,所以级间匹配将50 Ω的波源阻抗转换到根据式(2)计算出来的阻抗,输入级与波源共扼匹配而实现最大功率传输。第二级放大器的设计指标根据第三级的输入1 dB压缩点功率IP1 dB,3,设计本级的输出1 dB压缩点OP1 dB,2,要求满足关系为:

式(1)的目的是在第二级的线性范围内,保证第三级输出也在线性范围内,第二级的输出匹配与输入匹配思想与第三级的设计思路相同,这样就可以保证每级都能达到预定的1 dB压缩点输出功率。

1.1 MOS晶体管的选择与尺寸估算

MOS管的尺寸参数主要是栅宽与沟道长度,在能实现功能指标的情况下一般都选择其最小的沟道长度,这是因为MOS器件的发展趋势是每年按比例缩小的,因此设计也应该适应当前的MOS工艺。

传统功率放大器输出电流的基波项可为[4]:

式中Imax表示漏极允许通过的最大电流,Ion,max表示单位栅宽允许通过的最大电流,不过这里求得的栅宽是一个估算值,因此在设计过程中可以根据实际情况进行优化。

1.2 偏置电路设计

为了实现全集成电路设计,选择在片内集成偏置电路,本文采用的偏置电路如图2所示。通过合理调节MOS管M1和M2的宽长比,可以实现任意偏置电压,不过在设计中应该选择使功耗最小的设计方案。

对于图2所示的电路,可得其漏极电流表达式为:

由式(11)~式(12)可知,通过合理调节MOS管M1和M2的宽长比,可以实现任意偏置电压,不过在设计中应该选择使功耗最小的设计方案。

1.3 输出匹配电路

匹配电路的类型有L型、PI型和T型,在对Q值没特定要求的情况下,可以选用元件最小的L型匹配网络,通过使用双L型匹配网络还可以增加放大器的带宽,不过其缺点是降低了电路的Q值。由于功率放大器的输入端是调制信号,因此选取L型中高通匹配网络,而级间匹配采用双L型或者是T型匹配网络,输出匹配网络使用L型中的高通匹配网络,如图1(b)所示。

2 电路仿真与讨论

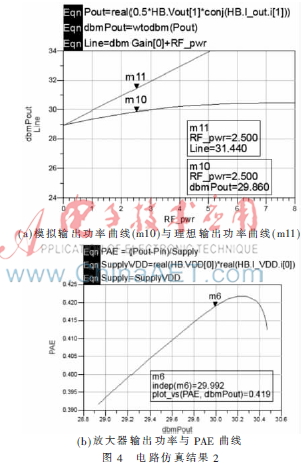

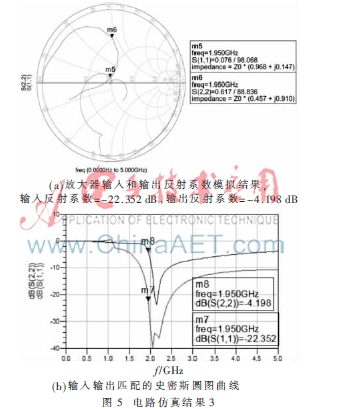

仿真软体采用Agilent公司的ADS2011,其仿真结果如下:放大器稳定性分析仿真结果如图3(a)所示,稳定因子在中心频率处K=4.6>1,因此整个功率放大器在中心频率处是无条件稳定的。对电路进行S参数仿真,如图3(b)所示,功率放大器的正向增益为27.7 dB。根据功率增加效率的表达式,可以描绘输出功率与PAE曲线,如图4所示。图4(a)中,标记m10和m11对应的输出功率分别为31.440 dBm,29.860 dBm,输入功率为2.5 dBm。结果显示在输出功率为30 dB时,PAE约为42%。功率放大器对输入反射系数要求较高,因为输出一般接的是天线,因此对输出反射系数要求有所下降,因为功率放大器一般要求输出大功率,这会造成输出不匹配现象。图5(a)显示本设计的整体电路的输入反射系数在中心频率处为-22.35 dB,输入和输出反射系数的史密斯曲线如图5(b)所示。

3 结束语

本文讨论了SOI工艺的物理特性及其在MOS器件中的应用情况,并结合LoadPull技术和IBM公司0.18 μm SOI CMOS工艺,设计一种应用于1.95 GHz的WCDMA全集成功线性率放大器。功率放大器采用三级AB类放大器级联结构,在工作电压为2.5 V的情况下,CMOS射频功率放大器无条件稳定,1 dB压缩点输出功率约为30 dBm,增益约为28 dB,最大功率附加效率(PAE)约为42%,最后通过仿真软件给出模拟结果。

参考文献

[1] LEE T H.CMOS射频集成电路设计(第2版)[M].余志平译.北京:电子工业出版社,2012.

[2] 林成鲁.SOI-纳米技术时代的高端硅基材料[M].合肥:中国科学技术大学出版社,2009.

[3] E.da Silva.High frequency and microwave engineering[M]. London:MPG Book Ltd,2001.

[4] CRIPPS S C.RF power amplifiers for wireless communica-tions[M].Second Edition.Artech House Publishers,2006.

[5] DAVIS W A,AGARWAL K.Radio frequency circuit design[M].Second Edition.United States of America:Wiley-IEEE Press,2001.

[6] RAAB F H,ASBECK P,CRIPPS S C,et al.Power ampli-fiers andtransmitters for RF and microwave[J].IEEE Trans-MTT,2002,50(3):822-824.