文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.10.005

中文引用格式: 陆振林,赵元富,兰利东,等. 基于可重构技术的DSP任务动态加载方法研究[J].电子技术应用,2015,41(10):24-26,33.

英文引用格式: Lu Zhenlin,Zhao Yuanfu,Lan Lidong,et al. Research on dynamic loading method of DSP task based on reconfigurable technology[J].Application of Electronic Technique,2015,41(10):24-26,33.

0 引言

随着微纳卫星、片上卫星的快速发展,对其电子系统的微小型化、低功耗的需求日趋明显。传统的多模块拼装的设计模式需要多个分离电路才能够构建完整的系统,显然,不能满足未来的发展需求。而集成微系统作为扁平化设计的新模式,将信息感知、数据处理、驱动控制等功能单元,采用MCM、SIP、TSV等封装技术,集成在一个芯片大小的封装体内,极大地提升了系统的集成度。

为了支撑微系统芯片对实时控制、高性能运算的要求。课题组提出了异构多核微系统的解决方案。其中,DSP作为协处理器,主要负责计算任务的执行。为了支撑运算任务类的灵活调度和映射的需求,DSP处理器的任务动态加载技术已成为急需突破的关键技术之一。

文献[1]通过SN74LVT16245A(双向三态收发器),将ARM总线和DSP处理器HPI接口进行互连,构建了ARM与DSP之间视频数据可靠传输通道,实现了大数据量的搬移,文献[2]面向实时图像处理的运算需求,通过DSP HPI接口,构建PowerPC处理器与DSP处理器的通信;文献[3]设计了ARM与DSP HPI的通信接口,通过162245总线隔离器进行数据总线的互连,完成了ARM对DSP程序的动态加载。还有其他的研究人员开展过相似的研究[4-7]。

以上的研究成果表明,通过HPI接口能够实现ARM处理器与DSP的数据交互,但设计方案都需要额外增加总线隔离器件来解决处理器与DSP的总线干扰问题。针对微系统而言,该方法存在以下问题:首先,该方法增加了芯片设计、测试的复杂度,带来系统体积和功耗的增加;其次,ARM处理器的总线时序与国产处理器并不相同;最后,研究中对数据总线进行了隔离,但是ARM的地址线、总线控制信号等与HPI直连的方式,在DSP处理器出现异常时,将有可能造成对主处理器总线信号的影响,导致主处理器无法正常工作。

因此,本课题提出了一种“基于可重构技术的DSP任务动态加载技术”的方法。该方案针对芯片级微系统对任务动态加载的需求,基于可编程逻辑器件自身资源,采用可重构技术,通过突破并行配置接口设计、数据动态加载等关键技术,解决异构多核芯片中DSP处理器的动态加载的问题。

1 基于可重构技术的注入通路设计

异构多核微系统芯片集成了国产SPARC V8处理器、FT-DSP处理器、FPGA、SDRAM、SRAM等器件。为了实现SPARC V8处理器向DSP处理器动态注入程序,并可控制其进行启动。文中利用了FT-6713的HPI接口(Host Port Interface)。HPI是一个并行端口,是外部主机(host)与DSP系统进行数据交换以及host配置各个外设寄存器的接口,可实现高速、并行的数据通信。FT-6713的HPI是16位宽的并行接口,V8处理器可通过HPI直接访问FT-6713的存储空间和外围设备。HPI接口信号如表1所示。

在通过HPI接口对DSP存储空间的访问时,需要解决如下问题:

(1)V8处理器与HPI接口互联的设计:由于V8处理器不存在与HPI接口相匹配的接口,需要采取合适的互连方法,以满足HPI操作的时序要求;

(2)HPI总线与V8总线串扰问题:在接口互连时,需要将总线信号、控制信号与HPI接口进行连接,当总线都进行操作时,将无法避免地带来数据的串扰,甚至导致任务执行崩溃。

本文结合HPI接口时序和V8处理器的总线时序,提出了如下的互连方案:

(1)V8处理器具有独立的地址和数据总线,因此,DSP的HPI接口的HAS由外部上拉至高电平。

(2)V8处理器的读使能信号(OEN)、写使能信号(Writen)、IO空间片选信号(CS)分别连接到DSP的HPI接口上3个触发信号HDS1、HDS2和HCS,而HDS1、HDS1、HCS共同产生HPI使能触发信号。

(3)V8处理器的地址线ADDR[7:6]与HPI的控制信号HCNTL[1:0]互连,以决定对HPI接口进行操作的目标寄存器,如HPIC、HPIA或HPID。

(4)V8处理器的地址线ADDR[4]与HPI的控制信号HHWIL互连,以此来指示当前数据总线传输的字节顺序。

(5)V8处理器的地址线ADDR[5]与HPI的HR/W互连,用于控制当前操作是在对DSP的HPIA、HPIC、HPID寄存器执行何种操作。

(6)V8处理器的Brdyn信号上与HPI的HRDY互连,用于表明HPI是否已准备好传输数据。

(7)V8处理器的外部中断与HPI的HINT信号互连,向主机发出中断信号。

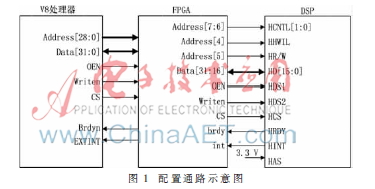

为了避免额外增加隔离芯片所带来的各种弊端,本课题提出了基于芯片内部FPGA的可重构实现方案。在需要进行DSP加载时,通过动态重构技术,在FPGA中加载并实现DSP HPI互联隔离逻辑,构建DSP的配置通路,当V8处理器完成对DSP程序加载后,V8处理器控制FPGA对隔离逻辑进行再次重构,断开DSP HPI接口与V8处理器的总线互联通路,以保证DSP处理器的异常不会对V8处理器造成影响。其连接示意图和FPGA内部逻辑如图1所示。

2 DSP任务的动态加载

2.1 动态启动模式

通过HPI接口对FT-6713处理器的程序注入和启动,需要持续对FT-6713处理器的3个寄存器进行操作,即HPI控制寄存器(HPIC)、HPI地址寄存器(HPIA)、HPI数据寄存器(HPID)。

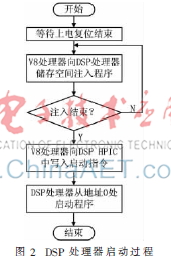

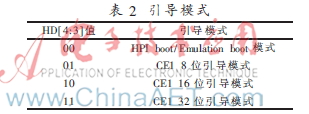

图2显示了HPI的启动流程。系统上电复位后,首先采样HPI接口的HD[4:3]的状态确定启动方式(即引导模式),如表2所示。为了能够动态加载和启动,本方法选择HPI启动模式,即HD[4:3]上电时默认为低电平。

FT-6713上电后,芯片外设控制器首先启动,内核处于挂起状态;此时外部主机通过HPI接口对DSP进行配置, 通过HPI初始化DSP的CPU core和EMIF,并向DSP加载程序和数据,将代码和数据加载到DSP的内存中,在这期间DSP内核保持挂起状态不变;当主机完成程序加载后,主机向HPIC寄存器中的DSPINT位写1,向DSP发出中断;DSP收到中断后,DSP内核从挂起状态唤醒,从0地址处启动,开始执行程序。

2.2 基于软件驱动的程序加载

V8处理器向DSP处理器注入程序,通过HPIC、HPIA、HPID和16位数据线与DSP进行数据交换和中断控制。DSP处理器程序注入的实现流程如图3所示。

(1)初始化HPIC

HPIC寄存器用于控制HPI的握手信号使能HRDY、字节传输顺序控制等。初始化该配置寄存器后,使HPI控制器进入V8所需的工作模式。

(2)初始化HPIA

通过向该地址寄存器写入待注入数据的地址,以便HPI控制器将相应的数据输出到相应的存储区。

(3)向HPID写入数据

HPID用于暂存由V8处理器注入的配置信息,写入方式具有自增写入模式和固定写入模式。由HCNTL[1:0]信号控制。本文选择自增写入模式。

(4)HPI启动

当数据全部写入DSP所属存储空间后,需要再次访问HPIC,并向其DSPINT位写入1来唤起DSP内核的启动和程序的加载。

在程序启动过程中,DSP会从0地址处开始执行。对于DSP的任务程序来说,是从c_int00处开始执行,需要使得程序跳转到_c_int00处。

在生成和编译DSP待注入程序,以及通过FPGA对HPI接口操作时,需要注意如下事项:

(1)由于项目中使用HPI16模式,因此对HPI任何一个寄存器的访问,主机都需在HPI总线上进行2次半字存取。

(2)DSP的程序在下载的同时需要链接初始化的变量,因此需要在.cmd文件中使用-cr选项。

(3)FT-6713 DSP编译器生成的文件为.out文件,构建动态加载数组时,对.out文件中有效配置信息进行提取。

3 测试

为了验证所提出的动态加载方法的功能和性能,进行相关测试。V8处理器系统时钟为80 MHz,DSP处理器内核运行时钟为96 MHz。

3.1 功能测试

本文采用TEKtronix TLA7012逻辑分析仪对HPI接口的信号时序进行了跟踪,采样频率为200 MHz。如图4所示,左侧两个椭圆圈定的32 bit数据将写入到HPIC寄存器,右侧两个椭圆圈定的第二个32 bit数据将写入到HPIA寄存器中。从测试数据可知,在HPI接口获取了正确加载的数据和时序。

3.2 性能测试

为了获取V8处理器发起DSP任务数据注入至DSP处理器正确启动的时间,设计了测试用例:V8发起程序注入后,拉高GPIO,DSP处理器在正确启动后,所属GPIO信号由低到高,两个GPIO信号间的间隔即可认为DSP程序注入及启动时间。如图5所示为2个GPIO信号电平变化的情况。

V8处理器通过FPGA连接到DSP的HPI接口,并向其注入了大小为280 KB的程序数据,从图中可见,整个动态加载和DSP运行时间仅为135 ms。

4 结论

针对系统级异构多核芯片的特点,协同工作的设计要求,提出了“基于可重构技术的”实现方法。该方法在无需增加总线隔离芯片和外部集成电路的情况下,通过构建的映射通路,V8处理器能够将任务正确的注入到DSP处理器存储空间,并启动DSP处理器内核,完成任务的动态加载。

测试结果表明,对于一个大小为280 KB的代码,从代码注入到DSP内核启动完成,所需时间仅为135 ms,能够满足系统的实时性要求。本文提出的方法满足了系统级芯片任务动态映射的需求。

参考文献

[1] 张力,刘正熙.ARM与DSP之间视频数据可靠传输的设计与实现[J].计算机应用,2009(29);198-200.

[2] 余跃,孟庆东,李兆麟.一种面向实时图像处理应用的基于非共享存储的多DSP系统设计[J].电子技术应用,2009,35(3):29-32.

[3] 赵建波,胡文若,习勇,等.基于ARM的TMS320C6455-DSPHPI的动态程序加载设计与实现[J].电子技术应用,2013,39(6):14-16.

[4] OU S H,LIN T J,DENG X S,et al.Multithreaded copro-cessor interface for multi-core multimedia SoC[C].Design Automation Conference,2008.Asia and South Pacific,2008:115-116.

[5] Yao Yiyong,Zhao Liping,Li Xin,et al.Dual-core embeddedreal-time inspection and analysis platform for field quality control and application[M].Intelligent Robotics and Applica-tions.Springer Berlin Heidelberg,2008.

[6] FAN H,CHEN W,LIU J,et al.The application of HPI in laser scanning system based on dual-DSP[C].4th IEEE Conference on Industrial Electronics and Applications,2009:484-488.

[7] SHANG Q,DU C.A novel measurement system of electric power parameters based on DSP and ARM[C].2009 Inter-national Conference on Measuring Technology and Mecha-tronics Automation,2009:353-356.