文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.11.009

中文引用格式: 王善明,严迎建,郭朋飞,等. 基于国产SOC的数据加密存储系统设计[J].电子技术应用,2015,41(11):34-37.

英文引用格式: Wang Shanming,Yan Yingjian,Guo Pengfei,et al. Design of data encryption and storage system based on domestic SOC[J].Application of Electronic Technique,2015,41(11):34-37.

0 引言

现在市面上有很多的数据加密产品,按照加密方式主要分为软件加密和硬件加密。软件加密的特点是:成本低、效率低、安全性低。硬件加密的特点是:成本高、效率高、安全性高。但是很多硬件加密产品的可扩展性比较差、没有丰富的外围接口。另外,如果要将数据加密产品应用于军事、政府等敏感部门,国外的产品不可信,而国内产品可选择范围又比较小。

由于经济和政治等多方面数据安全的重要性,最近几年国家大力支持国产IC的研发与推广。在此背景下,本单位研发了一款具有自主知识产权的密码SOC(System On Chip)芯片HX680。该芯片最主要的特点是内部集成了一个具有完全自主知识产权的协处理器,具有对称和非对称密码服务功能。该芯片还有相对比较丰富的外围接口,可以进行扩展和外部通信。

SD卡作为存储设备,具备很多其他存储设备没有的特点,如体积小、功耗低、容量大等[1],其应用范围日益扩展,因此在本设计中使用SD卡作为存储设备。FatFs是一个为小型嵌入式系统设计的通用FAT系统模块,具有开源、不依赖于平台、易于移植、代码和工作空间非常小等特点,作为本设计的文件系统是一个很好的选择[2]。

主控芯片内部没有集成实时时钟(Real-Time Clock,RTL),需通过外挂时钟芯片DS3231来解决文件系统获取时间信息的问题。主控芯片没有时钟芯片DS3231需要的I2C通信接口,需通过GPIO口的模拟来实现。

1 系统硬件设计

HX6801具有完全的自主知识产权,集成了国产32 位RISC结构嵌入式处理器CK520[3],具有专用软件集成开发环境和可扩展指令。协处理器具有硬件资源可配置、功能单元可重构、高性能、二次开发简便灵活等特点,HX6801适用于数字签名与身份认证、存储保护、数据传输、嵌入式控制等多种领域。系统采用HX6801作为主控芯片,SD作为存储设备,由DS3231提供文件系统需要的时间信息。HX6801芯片总体架构如图1所示。

1.1 DS3231接口电路

DS3231是一款高精度I2C RTC器件,具有集成的温度补偿晶体振荡器(TCXO)。该器件包含电池输入端,断开主电源时仍可保持精确计时。集成的晶体振荡器可提高器件的长期精确度。DS3231的寄存器能保存秒、分、时、星期、日期、月、年和闹钟设置等信息。少于31天的月份,可自动调整月末日期,包括闰年补偿。时钟的工作格式为24小时或带AM/PM指示的12小时格式。DS3231与主控芯片通过I2C双向串行总线传输地址与数据。DS3231的年误差小于1分钟[4]。

主控芯片HX6801没有I2C接口,所以使用GPIO口模拟I2C的时序,DS3231接口电路如图2所示,图中工作电压VCC的工作范围是2.3 V~5.5 V,典型的工作电压为3.3 V,TR表示信号SDA和SCL的上升时间,CB表示总线负载电容。

1.2 SD卡接口电路

SD卡支持SD模式和SPI模式两种通信模式。在综合考虑速度和设计复杂度的基础上,本设计选用SPI通信模式。SPI通信模式只需要将片选引脚、数据输入引脚、数据输出引脚、时钟引脚与主控芯片上对应的引脚连接即可[5]。

2 软件设计

软件部分采用了分层设计。主要包括4个部分:应用层、加/解密层、文件系统层、硬件驱动层(包括DS3231驱动程序和SD卡驱动程序)。应用层用来产生需要加密及解密的数据;加/解密层主要依据密码算法编程手册及编程工具,采用专用的密码指令编写相应的密码算法并配置协处理器;文件系统层主要实现FatFs文件系统的移植;硬件驱动层主要实现对最底层硬件的控制。层次结构如图3所示。

2.1 加解密层

可重构安全算法协处理器遵循了超长指令字的计算机体系结构,针对密码运算,提取了密码算法共性逻辑,提出并设计具有指令级可重构能力的专用指令系统和具有指令级并行处理能力的协处理器体系结构。该协处理器具有对称和非对称密码服务功能;具有专用密码处理指令,支持密码算法软件编程,能够灵活实现分组密码、序列密码与对称密码算法;可动态加载算法程序、参数,实现密码算法的重构与更换。下面以高级加密标准(Advanced Encryption Standard,AES)算法为例,介绍完整的算法处理流程,如图4所示。

2.2 文件系统层

FatFs是一个专门为小型嵌入式系统而设计的Fat文件系统,完全兼容ANSIC,而且不依赖于任何的平台。 FatFs的设计像很多软件一样采用了分层设计[6],最顶层的应用层为用户提供了操作底层硬件的API接口函数;中间层实现FatFs文件系统的协议;最底层是和具体的硬件相关的模块,需要用户编写代码。

FatFs移植包括SD卡disk I/O编写,RTC时钟函数编写,interger.h文件中数据类型和工程中数据类型的匹配,ff.h中条件编译的配置[6]。

FatFs支持Fat12、Fat16、Fat32文件系统。Fat32文件系统将SD卡划分为4个连续的逻辑结构:主引导记录、磁盘操作系统引导记录、文件分配表、数据区。

主引导记录(Master Boot Record,MBR)让硬盘具备可以引导的功能。

分区表(Disk Partition Table,DPT)用来表示磁盘可以分多少个分区。DPT部分共有64 B,DPT1~DPT4代表4个分区,每个分区16 B。

磁盘操作系统引导记录(DOS Boot Record,DBR)包含了文件系统相关的详细信息。

磁盘分区的数据区空间是以簇为单位寻址的。簇的大小一般是2N个扇区(本设计中N=3),一个文件可以占用多个簇,有可能同一个文件占用的簇是不连续的,这就体现了FAT的价值。FAT就是用于存储文件占用的所有簇的序号。Fat32和Fat12、Fat16的一个重要区别就是根目录(File Directory Fable,FDT)是数据区的一个子集,被当成文件对待[7]。

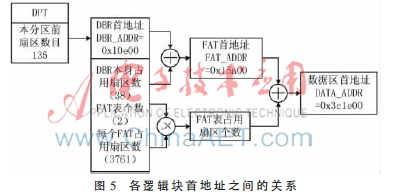

DPT、DBR、FAT及数据区四个区域首地址之间存在一定的逻辑关系,如图5所示。逻辑推导过程如下:

DBR_ADDR=135sector*512byte/sector=0x10e00

FAT_ADDR= DBR_ADDR +38sector*512

byte/sector=0x15a00byte

DATA_ADDR=FAT_ADDR+2*3761sector/FAT*512byte/

sector=0x3c1e00byte

数据区第3簇首地址

DATA_CLUSTER_ADDR=DATA_ADDR+(3-2)*8sector/cluster*512byte/sector=0x3c2e00byte

文件、文件分配表、文件目录、数据区的簇之间的关系决定了文件的存储方式。如图6所示,两个文件对应FAT表中两个链表0x00000004-0x00000007-0x00000001-0xFFFFFFFF(file1)和0x00000005-0x00000003-0x00000008-0xFFFFFFFF(file2)。

2.3 DS3231驱动

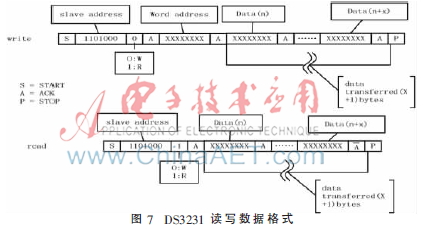

DS3231芯片采用I2C作为通信接口,设计中用GPIO口模拟I2C时序。I2C总线上传输的地址帧长度为9位,它包括7个地址位、1个R/W位和1个应答位。如果R/W为1,则执行读操作,如果R/W为0,则执行写操作。I2C总线上传输的数据帧长度为9位,它包括8个数据位,1个应答位。

DS3231寄存器地址为00H~12H,数据在寄存器中的存储格式为BCD码,每个存储单元大小为1 B。DS3231的寄存器00H~06H存储时间信息[8],存储格式如表1所示。DS3231的操作主要包括时间的读和写如图7所示。

FatFs系统中时间对应的数据结构存储在一个32位的无符号整数当中,数据存储格式如表2。时间信息从DS3231存储格式到FatFs存储格式要经过从BCD码到十进制数的转换。

2.4 SD卡驱动

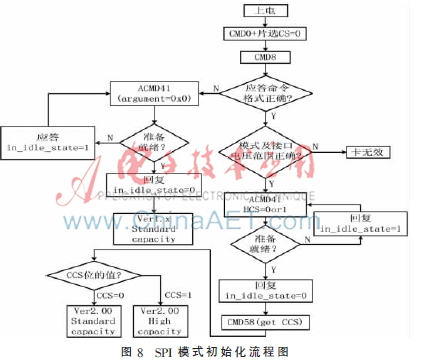

SD卡经过多年的发展,经历了好几次升级,如果驱动程序要兼容各个版本,就要考虑到各个版本的特殊性,从初始化流程图可以看出版本1.x和2.0在初始化阶段的不同点。SD卡根据容量的大小可分为不同的等级,2 GB以内(包括2 GB)称为标准卡,大于2 GB小于等于32 GB称为大容量卡,不同等级的卡操作细节也不尽相同。SD卡在初始化阶段会判断是否支持大容量卡[4]。

SD卡的驱动主要包括SD卡的初始化及数据块的读写等几个部分。SD卡的SPI模式初始化流程如图8所示。

从流程图可以看出,该设计对SD卡2.0版本向上兼容,同时支持大容量SD卡。SD卡上电的时候默认的是SD模式,当主控芯片发送复位命令(CMD0)的时候,保持片选信号足够的时钟周期(74个以上),SD卡可以进入SPI模式。CMD8命令向SD卡发送接口状态(主控芯片提供的电压是否满足SD卡的需求),ACMD41向SD卡发送主控芯片支持的SD卡容量并获取相应的回复。CMD58命令获取SD卡操作状态寄存器(Operating Condition Register,OCR)的值并读取CCS位(Card Capacity Status)判断是否支持大容量的SD卡。

SPI模式支持块读(CMD17)和多块读(CMD18)操作。SD卡接受到有效的读取命令后,要回复一个应答信号和相应的数据。需要注意的是,标准容量的卡读取的数据长度可以通过CMD16来设定(大小为1 B到512 B之间),大容量卡的数据长度固定为512 B。SPI模式同样支持块写(CMD24)和多块写(CMD25)操作,数据长度要求同读要求相同。每个数据块开始都应该有1个块起始位(大小为1位)。其中读操作采用的是命令(主机)-应答(SD卡)-数据(SD卡)的模式读取数据。写操作采用的是命令(主机)-应答(SD卡)-数据(主机)-应答(SD卡)的模式。

3 测试结果

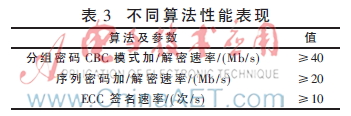

协处理器的性能及接口的速度是影响本设计的关键,鉴于各种密码算法自身的特点,处理器表现的性能有所差别,经测试以下几种算法性能如表3所示。

在将主控芯片的外设总线(Advanced Peripheral Bus,APB)设为40 M的情况下,加密并存储10 MB的数据需要的时间为3.4 s,读取并解密10 MB的数据需要的时间为3.9 s。

4 结论

经过多方面的理论分析和实验验证,本设计可以很好的实现数据的加/解密及数据的存储。在试验中可注意到,系统在处理大批量数据的时候效率不是太理想。所以为了进一步优化性能,下一步将研究如何优化加密算法,在SD卡及主控芯片允许频率范围内,尽可能提高APB时钟频率。

参考文献

[1] 苏义鑫,程敏,何力.基于AT89C52单片机的SD卡读写设计[J].世界电子元器件,2008(5):65-68.

[2] 陈祖爵,蒋仕俊.智能遥控器SD卡文件系统的设计与实现[J].计算机工程与设计,2007(10):4716-4718.

[3] 阳晔.面向嵌入式处理器的代码压缩研究[D].杭州:浙江大学,2007.

[4] DS3231 Extremely Accurate I2C-IntegratedRTC/TCXO/.[DB/OL].http://www.Maximintegrated.com/cn/prod-ucts/digital/real-time-clocks/DS3231.html#popuppdf.

[5] 葛建,董浩斌,郑海兵.嵌入式SD卡存储器的设计[J].电子技术应用,2010(5):139-142.

[6] 程小燕.嵌入式STM32F107VCT6微处理器接口模块开发及应用研究[D].合肥:合肥工业大学,2012.

[7] 刘思伽.基于SD卡的数据恢复技术研究[D].成都:电子科技大学,2010.

[8] Secure digital card product manual revision 1.7 9/2003[DB/OL].http://wenku.baidu.com/view/9d1fb307cc175527072208e7.html.