摘 要: 针对信号处理数据量大、实时性要求高的特点,从实际应用出发,设计了以双DSP+FPGA为核心的并行信号处理模块。为了满足不同的信号处理任务需求,FPGA可以灵活地选择与不同的DSP组成不同的信号处理结构,同时为满足大数据存储要求设计了可方便网络控制的数据存储模块。模块之间可以通过自定义LVDS接口实现互联,组成一个系统。

关键词: 实时性;双DSP+FPGA;数据存储

0 引言

随着科学技术的飞速发展,在无线通信、军事、工业、图像和医疗等领域高速大数据采集已经成为信号处理系统中不可或缺的部分,这就意味着在现代实时信号处理领域,在有限的时间内,需要处理和存储的数据量更大,同时为达到实时性,还要求信号处理系统具有多任务并行处理能力,这就对信号处理系统的处理能力提出了更高要求。与此同时,无论是雷达信号目标识别还是可见光的目标识别,都需要采集大量数据加强数据库建立,从而用来分析目标识别算法的性能,这无疑对数据存储提出了挑战。针对这些问题,本文采用两片ADI公司的ADSP TS201设计了多DSP松耦合的并行数字信号处理模块,并以两片Xilinx公司的Spartan3AN系列中的XC3S1400AN和TI公司的DP83865为核心设计了高速大容量、可以通过网口进行控制的数据存储模块,模块之间通过链路口桥接构成一个系统。

1 芯片选型

1.1 FPGA选择

FPGA选择Xilinx公司的Spartan3AN系列中的XC3S1400AN,此芯片含有502个I/O管脚[1]可以灵活地与DSP互联,同时可配成227对差分对,扩展成LVDS总线用于高速数据传输。选择此芯片的另一个优点是片内Flash达到16 Mbit,可将程序直接固化到片内,简化了外围结构。

1.2 信号处理芯片选择

ADSP TS201是ADI公司推出的一款性能极高的静态超标量处理器,对大的信号处理任务和通信结构进行了优化,具有适合多DSP并行处理的突破性体系结构,可广泛应用于大存储量、高性能、高速度的信号处理和图像处理系统中[2]。TS201的主要性能指标如下:

(1)最高工作主频可达600 MHz,指令周期为1.67 ns,可支持单指令多数据(SIMD)操作;

(2)6位定点处理能力达4 800 MMAC/s,是C64X的1.6倍;浮点处理能力是C67X的2.6倍;

(3)DSP之间LINK口通信可以达到单向最大速率为600 MB/s,双向1.2 GB/s;

(4)独立的片内总线(4条128位数据总线,4条32位地址总线)可提供4 GB的寻址空间;

(5)可通过共享总线提供无缝连接以用于片内集成总线的仲裁控制;

(6)片上SDRAM控制器和片上DMA控制器可提供14条DMA通道。

2 信号处理体系设计

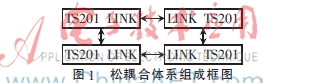

信号处理器可非常方便地构建简单的处理系统,也可以利用其多处理器接口和资源方便地构建多处理器系统。由于TS201特有的链路口具有强大的数据传输能力,在构成多处理器系统时,既可以构建总线共享的多处理器系统(紧耦合系统),又可以构建链路口耦合系统(松耦合系统)。以此为基础还可以构建总线共享和链路口耦合相结合的混合耦合系统[3-4]。松耦合系统是典型的链路口共享的多处理器体系结构。其系统组成框图如图1所示。

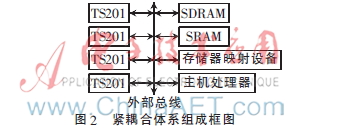

紧耦合多处理器系统是一种典型的总线共享的多处理器体系结构,其系统组成框图如图2所示。

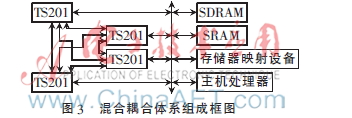

混合耦合多处理器体系结构,其系统组成框图如图3所示。

与其他两种耦合相比,松耦合系统无需总线仲裁,所以编程控制较为简单,另一方面由于松耦合系统结构简单,PCB实现较容易,本文根据实际需求选择松耦合系统体系。

3 系统硬件设计

高速数据并行处理与存储系统在标准的CPCI板卡上,按功能区域划分设置2片TS201,2片XC3S1400AN,1片DP83865芯片和6片MT29F256G08AUCAB,实现多处理器综合处理的超强处理和存储能力,系统框图如图4所示。

3.1信号处理单元硬件设计

信号处理单元的运算结构具有灵活性和可裁减性,FPGA可以灵活地选择与不同的DSP组成不同的计算结构,满足不同运算量的需求。对于运算量较小的任务,可以只使用FPGA和DSP1完成信号处理任务;而FPGA和两个DSP组合在一起可以完成运算量更大的任务;同时为保证系统数据传输的实时性,本硬件平台在各级流水之间提供高速灵活的数据传输通道。FPGA与2片DSP采用高速通用总线和链路口互连。2片DSP之间采用LinkPort互连。

DSP本身就带有24 Mbit内存,为了进一步提高硬件平台的存储能力,使之能够进行一些复杂的数据处理,为DSP配置了高速SDRAM。硬件平台的另一大特点是配置的灵活性。DSP1作为主DSP通过Link口完成第二片DSP的程序加载,由于本系统采取标准的CPCI板卡设计,便于不同处理系统的级联,不同的系统之间若要求时序统一,则可以通过Link口统一加载程序。

3.2 存储单元硬件设计

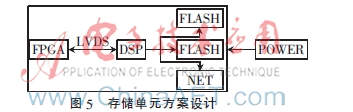

存储单元控制采用千兆以太网接口,可以方便地与普通计算机互连。方案如图5所示。

DSP处理的数据通过Link口发往存储单元,在FPGA内将Link口协议转换成相应的位数据写到NAND FLASH存储起来。可根据实际存储需求配置不同容量和数量的FLASH芯片[5-6]。

千兆以太网模块既完成存储器与上位机通信的功能,又作为数据输出接口。千兆以太网接口的物理层由物理层芯片DP83865实现,物理层以上协议在FPGA内部实现。数据传输采用UDP协议,上位机应用程序使用网络编程与FPGA进行通信,发送相应的控制命令。主机可以通过发送上传命令将存储的信息读出来。

4 系统软件设计

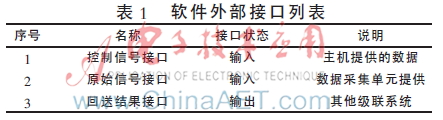

软件的外部接口主要有3种,如表1所示。

系统上电以后信号处理单元以接收链路口中断为触发事件,驱动DSP处理器完成实时信号处理任务,并在处理完成后将处理结果通过DSP链路口回送至信号源端由其他系统执行相应操作。

在信号处理的同时对信息数据及处理中间结果数据进行存储,以便进行数据库的建立及算法的分析改进。信号处理与存储系统软件工作调度流程图如图6所示。

5 结论

本文针对高速数据并行处理与存储中存在的一些问题提出了高速信号并行处理与存储系统。本系统采用ADI公司的TigerSHARC处理器,每片DSP处理器在600 MHz时钟下提供3.6 GFLOPS的32位浮点运算能力,2片处理器的计算能力为7.2 GFlops@600 MHz。

在Xilinx公司的芯片XC3S1400AN上实现了TS201和FPGA的LVDS接口互连设计。

最终结果表明,在本文所提出的关键设计的要求下,LINK口通信能够实现DSP之间互连,板内Link口的传输带宽可以达到800 MB/s,板间Link口的传输带宽可以达到600 MB/s,由于本文要处理的数据不会大于20 MB/s,所以完全可以满足数据传输要求。

扩展LVDS总线主要用于信号处理单元向数据存储单元收发信息,数据传输速率最大为20 MB/s,而LVDS总线的传输速率可以达到250 MB/s,且通信数据传输无误码、稳定。该结果说明了以FPGA为核心的数据存储单元有效地提高了数据存储的可靠性,实现了高速、稳定的数据传输。

参考文献

[1] Xilinx. Spartan-3 generation FPGA user guide[EB/OL].(2007-04-09)[2015-03-10]. http://www.xilinx.com.

[2] ADSP-T S201 TigerSHARC process or hardware reference[Z]. ADI, 2004.

[3] 冯小平,曹向海,鲍丹.TigerSHARC处理技术及其应用[M].西安:西安电子科技大学出版社,2010.

[4] 武岳.基于多DSP的硬件平台设计与调试[D].成都:电子科技大学,2007.

[5] 晏敏,龙小奇,章兢,等.开放式大容量NAND Flash数据存储系统设计与实现[J].微电子学与计算机,2009,26(11):13-16.

[6] 赵军伟,李宏穆,庄阿龙,等.NandFLASH和NorFLASH接口设计和驱动开发[J].嵌入式技术,2009(14):40-43.