摘要:PCIe总线是第三代I/O总线的代表,提供高性能、高速、点到点的串行连接,支持单双工传输,通过差分链路来互连设备。该设计由Xilinx公司的Virtex6 FPGA平台和PC机组成,为了实现PFGA与CPU之间的高速通信,开发了基于FPGA IPcore 的PCIe总线 DMA数据传输平台。通过硬件测试表明,该接口设计方案成本低,传输速率可以达到 15 Gb/s。

关键词:PCI-Express总线;FPGA;DMA

0引言

随着电子行业的飞速发展,人们对数据处理能力和存储速率的要求越来越高,并行数据传输的PCI总线技术逐渐成为系统整体性能提升的瓶颈[1]。尤其在接收机的设计中,总线架构关系到系统的整体性能。串行点对点的PCIe总线克服了PCI总线在系统带宽、传输速度等方面固有的缺陷,有效地提高了系统的整体性能。目前实现PCIe总线功能有两种方法:采用FPGA实现PCIe的功能[2];使用PCIe桥接芯片。由于通过FPGA实现PCIe接口要比使用PCIe桥接芯片更加灵活,成本更低,可靠性更好,所以采用前者完成FPGA与PC机之间的信息的交互。

1PCIe总线的简介

PCI Express 体系结构采用分层结构,共分为四层:物理层(Physical Layer)、数据链路层(Link Layer)、处理层(Transaction Layer)和软件层(Software Layer),这样利于跨平台的应用。软件层发出的读、写请求,使用基于数据包、分段传输的协议,通过处理层,传输至链路层。在链路层,数据包可以添加序列号和循环冗余校验(CRC),从而创建一个更高度可靠的数据传输机制。基本的物理链路层包括两个单一通道,即两个低电压的AC耦合差分信号对(一个传输对和一个接收对)。通过增加信号对形成多信道,可以组成x1,x2,x4,x8,x16以及x32的链路模式,串行数据传输采用工业标准的8b/10b编码实现数据恢复[3]。

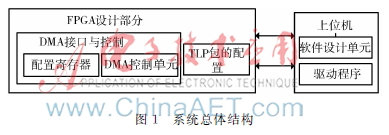

本文基于非协作接收机的验证平台进行研究,系统整体框图如图1所示。

2PCIe接口及应用层设计

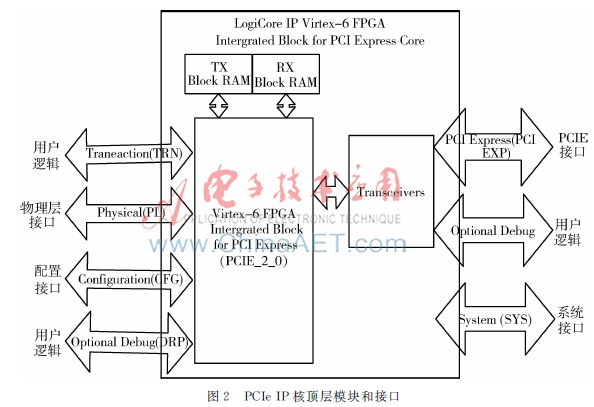

本设计采用Xilinx公司Virtex-6系列的FPGA,芯片为xc6vlx240t,集成了PCIe的IP核,该PCIe遵循V2.0的规范。首先使用Core Generation 生成PCIe的硬核模块,生成的PCIe子模块的链路宽度支持x1,x2,x4,x8四种模式。生成核的过程中主要需要配置的参数有:参考时钟、链路宽度、设备ID、基址寄存器、TLP的大小、对应的Xilinx的开发板等[4]。该核完全符合PCI Express的分层结构[5],提供了系统接口(SYS)、外部传输接口(PCI EXP)、配置接口(CFG)、事务接口(TRN)和物理接口(PL)。PCI Express的顶端功能模块与接口如图2。

用户逻辑接口:该接口为用户设计提供一个产生和消耗TLPs的机制;

物理层接口:该接口允许用户设计去查看链路状态和对方链路的控制及状态;

配置接口:主机通过该接口对IP核进行配置或读取状态;

系统接口:这里只包括时钟和复位;

PCIe接口逻辑:由若干对差分信号线组成,分为接收和发送信号线。

3DMA控制器的设计与实现

设计中为提高CPU的运行效率,在系统中引入了DMA控制器,该控制器是在PCIe IP核的基础上实现的,数据的传输不占用CPU的时间,提高了系统的运行效率。

本节主要介绍DMA中的TLP数据包结构、DMA相关寄存器的设计和PCIe接口的DMA读写操作核心状态机的设计。

3.1TLP数据包结构

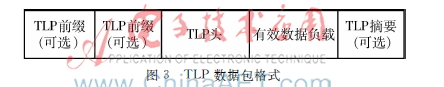

PCIe总线以数据包形式传送信息,本设计主要关注事务层数据包TLP。一个完整的TLP如图3所示,其中只有TLP头和数据有效负载需要由用户使用FPGA程序实现,其他都由PCIe核自动生成并加到帧结构中[6]。

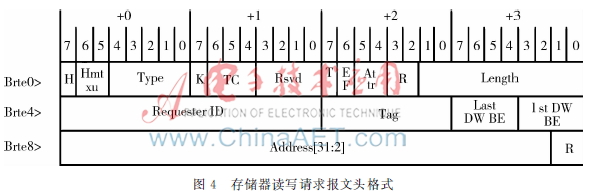

TLP头是TLP中最重要的部分,主要包含当前TLP的总线事务类型、路由信息等。一个TLP中的数据有效负载的长度是可变的,本设计中选用的最大负载长度为512 B。PCIe 核支持32 bit和64 bit地址空间的操作,其中32 bit地址空间读写操作的TLP头格式如图4。请求者根据自己的需要填写TLP头中的信息,并将数据放在TLP头的后面发送给接收者,接收者解析出正确的数据放入到自己的地址空间中。

DMA写操作使用的TLP格式与存储器写操作TLP格式相同,DMA读操作需要使用存储器读请求与存储器读完成两种TLP格式。当接收到存储器读请求时,设备需要发送CPLD(带数据的完成报文)。带数据的完成报文与读写请求报文不同。

32DMA操作寄存器的定义

PCIe IP核提供6个32 bit基地址寄存器BAR0~BAR5,也可以作为3个64 bit基地址寄存器,可以根据实际需要进行配置。设计中使用BAR0存储各种寄存器地址,使用BAR1作为内存操作基地址空间。在BAR0中各寄存器地址定义如下:

(1)偏移地址0x00(DCR2)是控制DMA开始的寄存器,当写入0x01时,DMA操作开始,上位机开始接收数据。

(2)偏移地址0x04是中断服务寄存器。当DMA数据包传输完毕时,写0x01到该寄存器,产生一个中断,上位机会进入中断服务进程。

(3)偏移地址0x08是DMA传输的目的地址。该目的地址是PC机端的内存首地址。DMA传输开始之前,将该地址写到该偏移地址。当DMA操作时,将FPGA板卡上的数据传到PC机端该地址处。

(4)偏移地址0x0C是DMA传输的数据长度。设计中定义了每个包的数据长度是512 B,由该值可得到需要传输的数据包个数,用于控制DMA操作的结束时刻。

33DMA控制器

在整个设计中,DMA控制状态机是核心部分,主要包括Tx Engine和Rx Engine。Tx Engine负责接收上位机存储器读写操作、单字发送及DMA发送。Rx Engine主要负责存储器读写操作、单字接收及DMA接收。实现PCIe的DMA读写操作的主要方法是正确填写TLP包头中的各个字段,并将数据按照64 bit并行放在TLP包头中。对于DMA写,将数据传输给PCIe硬核,由硬核将数据发送到物理端口,最后传输到PC机的物理地址中;对于DMA读,主机将数据包发送到硬核,最后Rx Engine解包,将数据输出。

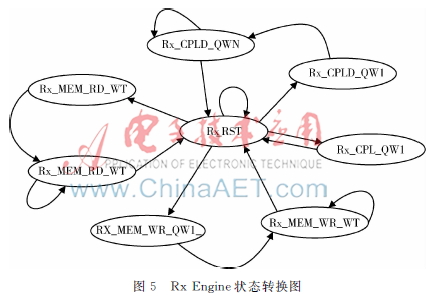

Tx Engine和Rx Engine是使用状态机来设计的,Rx Engine状态转移图如图5所示。

Rx Engine开始时处于Rx_RST状态,当Rx Engine收到数据包时,首先解析数据包,根据TLP包头分辨数据包类型,进入不同的状态。当接收到的是存储器读时,进入Rx_MEM_RD_QW1状态,发送信号通知Tx Engine,由Tx Engine发送CPLD数据包;当接收到的是存储器写时,进入Rx_MEM_WR_QW1,处理收到的TLP数据并更新配制寄存器;当收到的是CPLD时,进入Rx_CPLD_QW1状态,解析数据包,将数据存储到相应的存储器中;若信号trn_reof_n(传输结束信号,低电平有效)低电平没有到来,则Rx Engine从Rx_CPLD_QW1进入到Rx_CPLD_QWN状态,根据寄存器中存有的DMA数据长度来判断数据是否已经接收完成,若没有完成则不断在该状态循环,直到数据接收完毕,状态机回到复位状态。

Tx Engine状态转换图如图6所示。

Tx Engine状态机同Rx Engine基本一样,这里不再赘述。

DMA传输开始之前需要对DMA的相关寄存器进行配置,表1是写DMA的操作步骤,写DMA控制和状态寄存器中定义了TLPs的地址、大小、个数、负载内容。

其中DCR1和DCR2是设备控制寄存器,控制选择FPGA型号、接口数据带宽、读/写DMA开始/结束以及中断服务的开启。WDMATLPA是写DMA的TLP低32位地址表1写DMA操作步骤步骤操作寄存器操作值1发起初始化复位写DCR10x000000012取消初始化复位写DCR10x000000003写DMA的PC端口地址写WDMATLPAPC端地址4写DMA TLP大小写WDMATLPS事务包大小5写DMA TLP个数写WDMATLPC事务包个数6TLP数据包中payload值写WDMATLPP数据值7写DMA开始写DCR20x000000018等待中断TLP9写DMA执行结果读WDMAPERF

寄存器,WDMATLPS是写DMA事务包的大小、事务包TC字段。WDMATLPC是写数据包个数寄存器。WDMATLPP是写数据包类型及32位有效负载寄存器。WDMAPERF是写DMA执行寄存器,表示完成DMA传输所用到的接口时钟周期数。

读DMA与上述过程一致,只是在DMA中的传输方向的寄存器值不同。

4仿真及测试结果

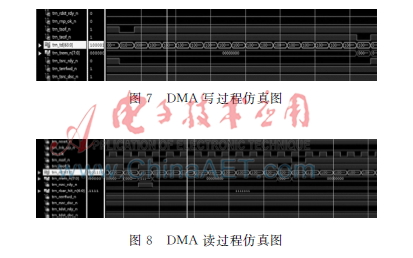

完成FPGA的程序编程后,用Modlesim对程序进行仿真。硬件测试时,使用ChipScope抓取数据,主要分析DMA控制器产生的PCIe总线传输信号时序是否满足要求。同时,通过软件测试了DMA传输速率。

图7是DMA写过程的仿真图,功能是由FPGA板卡将数据上传至PC机,图8是读过程的仿真图,功能是由PC机到FPGA板卡的数据传输。由测试数据可以估算出PCIe Gen1x8写操作速度可以达到15 GB/s。

由图7可以看到数据包传输开始于trn_tsof_n低电平之后,结束于trn_teof_n。数据传输期间trn_tsrc_rdy_n和trn_rdst_rdy_n必须有效。

由图8可以看到数据包传输开始于trn_rsof_n低电平之后,结束于trn_reof_n。数据传输期间trn_rsrc_rdy_n和trn_tdst_rdy_n必须有效。从图中可以看到,若DMA传输没有结束,在该数据包结束之后,会有新的数据包出现在链路上。

由仿真图可知该设计能完成DMA读写功能并保证数据的正确传输。

实验结果可得,DMA写数据的速率可达15 GB/s,读数据的速率可达147 GB/s,数据速率有大幅的提高。

5结论

本文在PCIe硬核基础上,设计了DMA控制器,使传输速度大幅度提高。经实际测试,该方案的数据传输速度在15 GB/s左右,可以满足工作需要。PCIe是目前总线中传输速度最快的一种,此方案为高速的数据传输提供了一个参考,具有很好的参考和应用价值。参考文献

[1] 王齐.PCI Express 体系结构导读[M].北京:机械工业出版社,2010.

[2] 雷雨,任国强,孙健,等.基于PCIE 的高速光纤图像实时采集系统设计[J].电子技术应用,2013,39(10):136-142.

[3] 魏芸.基于FPGA的PCIe总线DMA平台设计[D].武汉:武汉理工大学,2013.

[4] 陈刚,张京,唐建.一种基于FPGA的PCIe总线及其DMA的设计方法[J].兵工自动化,2014,33(5):75-77.

[5] LogiCORETM IP Virtex6 FPGA Integrated Block Data Sheet[R].Xilinx,2009.

[6] 李木国,黄影,刘于之.基于FPGA的PCIe总线接口的DMA传输设计[J].计算机测量与控制,2013,21(1):233-235.