王慧英1,曹志锋2

(1.吉首大学 张家界学院,湖南 张家界 427000;2.国防科技大学 机电工程与自动化学院仪器系,湖南 长沙 410004)

摘要:设计了一个基于PCI-E总线的高速光纤数据采集系统。对高速光纤数据的处理、传输、存储和WDM驱动程序的开发做了论述。经测试表明,该系统能够对处理后的2路2.5 Gb/s SDH光纤信号连续采集近3小时不丢帧,采集的数据量达6 TB,稳定的存盘速率高达600 MB/s,具有很好的应用价值。

关键词:PCI-Express总线;高速采集;光纤数据;磁盘阵列;DMA

0引言

高速采集系统中的数据具有数据速率高、数据量大的特点,要对高速数据进行实时长时间存储,必须克服高速数据的传输与存储的技术难题。本设计采用PCI Express总线技术对高速数据进行传输,用高速磁盘阵列技术对高速数据进行存储。

PCI Express[12],简称PCIE,是用来互联诸如计算机和通信平台应用中外围设备的第三代I/O总线。PCIE总线每个通道的单向速率不低于2.5 Gb/s,可以根据用户的需要灵活配置成x1、x4、x8、x16的工作模式。

冗余磁盘阵列[3],简称RAID,是一种由多块廉价磁盘构成的冗余阵列,主要由阵列控制卡和多个硬盘组成。数据分布在阵列的各个磁盘中, 磁盘数据的读写由多个磁盘并行完成,非常适用于高速大容量数据的存取。

1系统总体设计概述

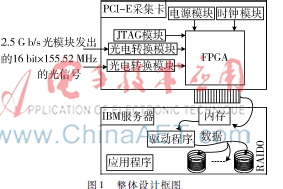

本高速采集系统由PCIE采集卡、上位机、PCIE驱动和应用程序组成,如图1所示。PCIE采集卡以FPGA为核心,FPGA外围有光电转换模块、电源模块、时钟模块和JTAG模块。

FPGA用于对高速数据的处理和PCI-E总线的控制,电源模块为FPGA和光电转换模块供电,时钟模块为FPGA提供高精度的差分(LVDS)时钟信号,JTAG模块用于FPGA的调试和程序下载。

驱动程序负责把上位机数据缓存区内的数据搬运到磁盘阵列中,并对FPGA中的DMA寄存器赋初值[4];应用程序用于人机交互,控制PCIE采集卡的采集与停止,并提供一些相关的状态信息。

2PCI-E采集卡设计

PCI-E采集卡用于对高速光纤数据的处理和传输。

2.1硬件构成及性能分析

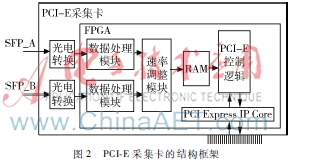

本设计选用Altera公司的Stratix II GX系列EP2SGX90FF1508C3N芯片来实现PCIE总线功能,并用其对数据进行处理。该芯片内部有4 520 448 bit的RAM资源,16对处理速度高达6.375 Gb/s的Transceiver通道,片内的PCIE IP核(软核)支持PCIE 1.0a和1.1规范,通道可配置成x1、x4或x8的类型。在本设计中,把PCIE的IP配置成x4模式。x4 IP除去8b/10b编码的开销,有效数据带宽为8 Gb/s,可以满足接入2路2.5 Gb/s信号的传输。PCIE采集卡的光电转换模块选用武汉电信器件公司的RTXM192450,该器件的速率为2.488 32 Gb/s,输出的信号可直接给FPGA处理。PCIE采集卡的结构框架如图2所示。

2.2数据处理机制

SDH信号[5]的一帧数据有9行270×N列,共9×270×N字节,大体分为3个主要的区域:段开销(SOH),管理单元指针(AU PTR)和净荷区域。其中段开销又可分为再生段开销(RSOH)和复用段开销(MSOH)。图3为STM-N的帧结构。

在本设计中,接入的SDH信号为STM16,且只对其净荷进行存盘。故接入的信号要进行帧同步、解扰(解扰多项式为x7+x6+1)、净荷提取等处理。

为了使采集卡能适应2路不同源SDH信号的输入,还需对接入的信号进行速率调整。速率调整机制为:在片内开2个位宽为64 bit、容量为64 KB的FIFO,分别命名为FIFO_A、FIFO_B,FIFO_A和FIFO_B分别用于缓存SFP_A和SFP_B的接入数据,当有FIFO半满时,交替地从2个输出位宽为64 bit的FIFO中读出32 KB的数据,另外加入64 bit的线路标识,以便存盘时进行数据分离,这样向RAM写一次的数据量就为32 KB。

2.3DMA传输机制

对于高速数据流, 必须用DMA传输方式才能保证数据在采集卡和上位机之间通信时不丢失[6]。

在本设计中,一次DMA传输的大小为双口RAM的容量。双口RAM快写满时开始DMA,每次DMA完成后,向上位机发中断信号通知驱动去上位机数据缓存区搬数据写盘。为了克服Windows操作系统响应PCIE中断的非实时性和相对不确定性[7], 同时考虑FPGA存储资源的限制, 双口RAM 的容量选取256 KB,位宽为64 bit。

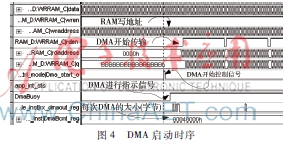

64位双口RAM的地址范围是0~7FFFh,且向双口RAM写一次的数据量为32 KB,为了保证每次启动DMA传输时双口RAM中都有256 KB的数据,且不引起读写冲突,设定RAM的写地址等于7100h时启动DMA传输,即向RAM中写入了226 KB的数据,此时第8个32 KB的数据块已经向RAM中写了2 KB。DMA的启动时序如图4所示。

3系统存储机制

该采集系统的存储部分由上位机、PCI-E驱动和应用程序构成。

3.1上位机配置

在本设计中,上位机选用IBM公司的System x3650 M3服务器。该服务器采用英特尔至强5600系列六核处理器,主频为3.33 GHz,内存配置为20 GB,内部存储由16块型号为42D0752的硬盘组成RAID 0阵列,总存储容量为8 TB。

3.2WDM驱动程序开发

本设计选用Visual C++ 6.0 、DriverStudio和DDK来进行WDM驱动程序开发。

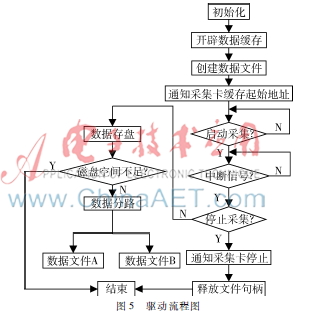

由于Windows操作系统的非实时性和写磁盘阵列的瞬时速度的不稳定性,有时不能实现将写入内存缓冲区的数据立即存储在硬盘上,因此为了连续不断地接收光纤数据,必须在内存中分配一块大的连续内存作为DMA的数据缓冲区,这个缓冲区的大小一定要大于一次DMA传输的数据量,并采取环行存储结构[8]。经在上位机上调试,在保证系统工作稳定的前提下,数据缓存可开到512 MB,即可缓存2 048次DMA的数据。采集数据时,驱动收到一次中断就进行一次256 KB的写磁盘操作。驱动程序的工作流程如图5所示。

4性能测试与分析

为测试系统性能,设计一个已知格式的类STM16信号源:帧长为16 bit×19 440=311 040 bit,帧头为48个F6,48个28,其余段开销和管理单元指针全填充0;净荷区域,第1行前4个字节为帧序号,帧序号后为2个字节的数据标识,SFP_AS、FP_B的数据标识分别为CCCC和DDDD,其余位置填充数据为0~18 788(0~4964h),第1行的前144个字节在发送时不加扰。

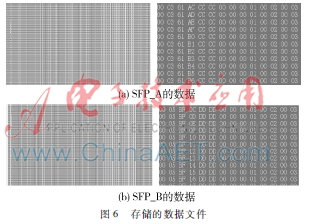

由于只存储了STM16的净荷数据,因此在查看采集的数据时,把每行数据大小设为16 bit×18 192 bit,这时看到的数据就如图6所示。图中左边为数据文件的缩小图,右边为数据文件的放大图。如果存储文件的帧序号是连续的,且数据是对齐的,则证明数据没有丢帧。

5结论

本系统能够对2路2.5 Gb/s的STM16信号进行实时长时间存储,保证连续存储6 TB的光纤数据不丢帧,可连续存储近3小时,稳定的存储速率高达600 MB/s。该系统测试完后已移交给用户使用。该系统还具有良好的适应性并具有极大的升级空间,对FPGA代码稍作修改并更换相应速率的光电转换模块,该系统就可以采集STM1和STM4速率的SDH光纤数据;如果把PCIE的IP配置成x8模式,并使用高性能的服务器和固态硬盘,该系统每秒的存储速率可以达到GB级。该系统的研制,对于光通信设备的研发和光传输系统特性的测试具有重要的意义。

参考文献

[1] BUDRUK R, ANDERSON D, SHANLE T.PCI Express系统体系结构标准教材[M].田玉敏,王崧,张波,译.北京:电子工业出版社,2005.

[2] PCISIG. PCI Express base specification revision 3.0[S].2010.

[3] 丁泾莉,朱春红,成雪莉.RAID磁盘阵列技术及应用[J].石油工业计算机应用,2006,14(2):3941.

[4] 温宇辰,李明伟,陈玉龙.PCIE总线光纤接口卡的设计[J].电子技术应用,2014,40(4)126129.

[5] ITUT. ITUT Recommendation G.707/Y.1322 Network node interface for the synchronous digital hierarchy (SDH) [S].2007.

[6] 杨阿锋,吴帅,刘凯,等.PCIe接口高速数据传输卡的驱动程序开发[J].中国测试技术,2008,34(2):6768.

[7] 吕喜在,张宝文,赵德鑫,等.基于PCI Express总线的高速海量光纤数据记录仪的设计[J].计算机测量与控制,2010,18(9):22032206.

[8] 周立国,梁淮宁,谢冬冬,等.基于PCI Express总线的数据传输卡的设计与实现[J].电子测量技术,2007,30(11):2831.