王文萱,翟正军

(西北工业大学 计算机学院,陕西 西安 710129)

摘要:1553B总线在航空、航天、舰船等嵌入式高可靠实时通信领域占有重要地位。分析了1553B总线终端的组成,归纳比较了DDC公司研制的多款1553B总线处理器的发展变化的特征,应用该公司集成度最高的1553B总线处理器,设计了小型化的1553B总线终端,与采用集成度较低的1553B处理器完成的设计方案进行了比较。结果表明,所设计的终端在体积、功耗、重量方面降幅均超过60%。

关键词: 1553B总线;总线终端;通信处理器

0引言

数字式时分制指令响应型多路传输总线1553B标准最初是由美国为研制联合式航空电子系统制定的通信标准。由于1553B总线在航电系统上的应用大大提高了飞机的性能,因而逐步扩展到舰船、航天等高可靠通信领域。虽然1553B总线已发展应用了30年,但由于1553B总线具有集中控制简单、实时响应、容错可靠、便于维护、技术成熟等优势,因此在航空、航天、舰船等嵌入式高可靠实时领域1553B总线依然占有重要的地位。以最新型的欧洲宽体客机A350XWB为例,在机载局域网中采用了1553B总线实现联网通信。

嵌入式高可靠实时系统功能与性能发展的同时,对系统的体积、功耗、重量等要求也愈来愈高,在基于1553B总线互联的系统中,每个设备都需要1553B终端才能接入到总线中,因此1553B总线终端在系统中占有相当的比重。在满足系统通信要求下,降低1553B总线终端的设计复杂度,减少体积、功耗、重量,成为1553B终端设计人员的一项重要的追求目标。

美国数字设备公司(DDC)[1]在1553B总线器件研发、制造及应用方面占有重要的地位,本文以其不断推新发展的1553B总线处理器芯片为研究对象,分析归纳了DDC公司将原来与1553B终端实现相关的外围器件不断集成到1553B总线通信处理器中,而且不断扩展1553B总线通信处理器内部可编程能力的趋势,使读者了解1553B总线通信处理器功能不断增强、集成度不断提高的特点,为设计人员选择合适的1553B总线通信处理器提供参考,以满足系统1553B总线功能要求的同时,也能满足对1553B总线终端的体积、功耗、重量的指标约束条件。

11553B总线终端构成

1553B总线传输速率为1 Mb/s,传输媒介为屏蔽双绞线,可接入32个终端,终端共有三种类型:总线控制器(Bus Controller,BC)、远程终端(Remote Terminal,RT)和总线监视器(Bus Monitor,BM)。BC是总线上唯一能组织数据消息传输的终端;RT是接受总线上BC控制,完成消息发送或接收的终端;BM是接收总线上消息并能有选择记录的终端,其仅“监控”总线上信息传输但不参与总线的通信。在嵌入式高可靠实时系统中,1553B总线为双余度拓扑结构,所有1553B总线终端设备通过变压器耦合方式挂接在总线网络上[2]。

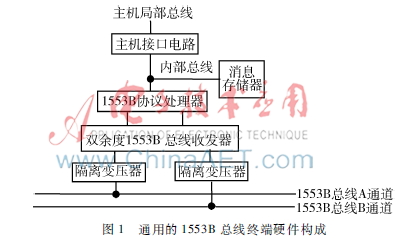

采用变压器耦合方式的1553B总线终端硬件包括:主机接口电路、消息存储器、1553B协议处理器、双余度总线收发器和隔离变压器。通用的1553B总线终端硬件构成如图1所示。

主机接口电路、实现主机地址、数据及控制总线到终端内部总线的缓冲隔离及控制。消息存储器支持主机与终端内部1553B协议处理器对1553B总线消息数据的存储、读写访问,需要设计消息存储器共享互斥访问控制电路,以达到两者可正确访问。

1553B协议处理器按照1553B协议要求,首先完成1553B的ManchesterⅡ码编译码、数据串并转换与并串转换、数据字同步头的产生与检测、奇校验;其次根据主机规定,作为BC、RT或BM完成总线传输中的任务。作为BC,组织消息的发送与正确性判断;作为RT,完成对指令字的识别、状态字的自动响应;作为BM,完成对所有或部分要求监控的消息监控并记录。1553B协议处理器是终端的控制核心,不仅要访问消息存储器完成1553B消息数据的收发及相应状态的修改,而且要与双余度1553B总线收发器连接,将串行数据发送到发送器或从接收器接收串行数据,还要提供主机可编程接口能力,由主机控制终端的角色、运行或读取终端的实时状态,在主机通信软件管理下完成1553B总线传输任务。双余度1553B总线收发器能够将TTL电平的串行Manchester码与双极性的Manchester码相互转化。两路隔离变压器,源端与双余度1553B总线收发器连接,次端与1553B总线的两条主电缆耦合器分别相连。

21553B通信处理器的变化分析与比较

从上面1553B总线终端构成可见,为完成1553B总线通信任务,需要至少五部分功能单元电路。

在2000年前,1553B总线生产厂家如UTMC、NHI等公司的1553B协议处理器、总线收发器、变压器等均是独立的器件,因此设计1553B总线终端需要十多个元器件,硬件模块体积大、重量重、功耗大。

DDC公司首先认识到集成的必要性和发展趋势,于1995年推出了集成度大幅度提高的1553B先进通信引擎(ACE)器件[3],是高集成度的1553B总线通信处理器。 ACE单一器件包含了子系统(设备)主机接口隔离电路、消息存储器、1553B协议处理器、双余度总线收发器,实现的主要功能包括:

(1)BC/RT/BM协议一体化设计,由软件配置工作角色;

(2)主处理器接口,灵活多样,支持8/16 bit模式,可零等待或插入等待;

(3)消息存储器,64 KB RAM,包含主机与内部协议访问的互斥访问控制;

(4)内置双余度总线收发器,单5 V供电;

(5)增强BC功能的特征:支持自动重试、可编程间隔时间、帧自动重复、可编程响应超时时间;

(6)增强RT功能的特征:可编程命令非法化表,可选择单消息缓冲、双缓冲、环形缓冲和全局环形缓冲,独立的方式命令中断,可根据子地址进行忙位编程;

(7)增强BM功能的特征:选择消息监控特征,提供可编程触发选项。

随着半导体微电子工艺水平的发展和提高,在对1553B终端设计要求不断提高的外界需求推动下, 以ACE为基础,通过集成外部器件提高集成度、改变封装缩小体积、增强内部新的功能扩展通用性等措施,DDC公司在1999年、2004年、2011年和2013年分别推出了MiniACE、MicroACE、TotalACE、TotalACEXtreme四款产品。下面分别说明这四款典型处理器的主要特点。

(1)MiniACE将ACE的DIP封装改为“Flat Pack”封装,体积压缩为25.4 mm×25.4 mm×3.3 mm。相比ACE仅有的CPU局部总线接口,扩展提供了一种PCI总线的接口,为1553B终端作为PCI总线的从设备提供了无缝连接。但需要外接两个隔离变压器。(2)MicroACE在MiniACE基础上,不仅增强了BC的编程能力,包括十余种总线表判定、分支、循环操作码等,方便了用户对总线的控制,而且改为BGA封装,体积压缩到20.7 mm×20.7 mm×3.3 mm。提供CPU局部总线接口或PCI总线接口。需要外接两个隔离变压器。(3)TotalACE在MicroACE之上,内部集成了两个隔离变压器,是BGA封装,体积为27.9 mm×15.2 mm×4.7 mm,也提供CPU局部总线接口或PCI总线接口。不需要外接两个隔离变压器。(4)TotalACEXtreme在TotalACE基础上,增强了能同时做多个RT的功能。采用更小的BGA封装,体积缩小为16 mm×16 mm×4.7 mm;提供CPU局部总线接口或PCI总线接口。不需要外接两个隔离变压器。

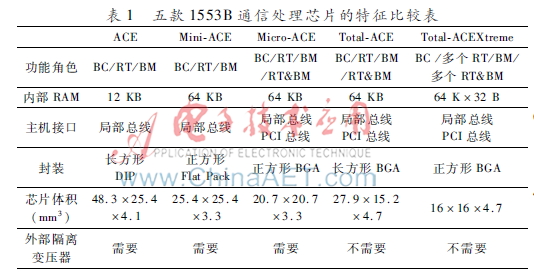

总结DDC公司以上五款1553B通信处理芯片的特征,比较如表1所示。

31553B总线终端设计

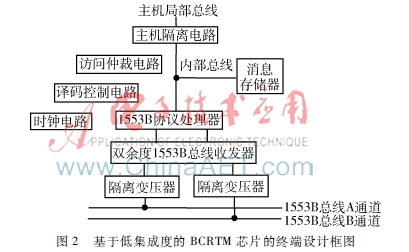

采用UTMC公司低集成度1553B协议处理芯片BCRTM为核心器件[45],需要增加外部存储器、双余度收发器、两个隔离变压器、主机接口隔离电路、仲裁电路、译码电路、时钟电路等,需要至少10多个功能器件,才能实现一个1553B总线终端,如图2所示。

图2基于低集成度的BCRTM芯片的终端设计框图

而采用最新的Total-ACEXtreme高集成度芯片[6],因其内部集成了绝大多数电路,只需要再增加时钟、简单的主机接口访问译码电路即可构建一个比UT1553B BCRTM方案功能更全(支持多个RT同时工作、RT&BM模式等功能)的1553B总线终端,如图3所示。

图3基于高集成度TotalACEXtreme的终端设计框图对比采用集成度较低的UT1553B BCRTM芯片与采用集成度最高的TotalACEXtreme芯片构建1553B总线终端的两种设计方案,后者占用电路板的面积节省了70%,重量减轻约60%,功耗降低约60%,因而大大降低了1553B总线终端的体积、功耗、重量,为系统设计节省了宝贵的资源。

4结论

本文介绍了1553B总线终端的功能单元构成,通过分析DDC公司推出的五款1553B总线处理器的技术特征和发展趋势,说明随着集成电路水平的提高,1553B总线通信处理器集成的功能电路数量不断增加、完成的功能愈来愈强大、体积越来越小;同时与主设备的接口趋向简单化、服务趋向透明化,从而为1553B设计人员降低1553B总线终端硬件设计复杂度,减少体积、功耗与重量的目标奠定了基础。

参考文献

[1] MILSTD1553B Designer′s Guide[Z].Data Device Corporation.

[2] 张浩.嵌入式1553B总线通信卡的设计与研究[D].南京:南京理工大学,2008.

[3] BU65170/61580 Advanced Communication Engine (ACE) Data Sheet[Z]. Data Device Corporation.

[4] UT1553B BCRTM manual[Z]. United Technology MicroElectrical Corporation.

[5] 刘士全,黄正,蔡洁明,等.1553B总线应用竞争访问时序分析[J].微型机与应用,2015,34(1):6971.

[6] TotalAceXtremeTM BU67301B Data Sheet[Z]. Data Device Corporation.