文献标识码: A

DOI:10.16157/j.issn.0258-7998.2016.08.005

中文引用格式: 王超,刘欢艳. 如何在先进工艺节点利用Virtuoso Check/Assertion Flow[J].电子技术应用,2016,42(8):28-32.

英文引用格式: Wang Chao,Liu Huanyan. How to use Virtuoso Check/Assertion Flow in advanced node IC design[J].Application of Electronic Technique,2016,42(8):28-32.

0 引言

随着集成电路设计和先进工艺技术的飞速发展,电路规模越来越大,电路越来越复杂,电路设计过程中,如何尽可能地避免潜在问题,遇到问题时, 如何尽快有效地定位和解决,成为电路设计工程师普遍关注的话题。电路仿真工具在提供大容量以及快速仿真能力的同时,如果能支持器件级别及电路级别的各种检查机制,对于有效地避免问题,定位问题和解决问题,会有帮助。电路设计平台(Virtuoso)如果支持方便灵活地设置、看结果以及对结果进行后处理, 会使流程更顺畅,使用更方便,工程师更容易上手,从而提高设计效率。

Assert又称Device Checking,是Spectre/APS提供的主要用于器件级别的检查机制,主要用于检查电路中的器件电压、电流、工作点、模型参数及自定义表达式等;Circuit Check 是Spectre/APS/XPS 提供的主要用于电路级别的检查机制,主要用于检查特定的电路设计问题,最常见的包括检查电路中的悬空输入点、高阻点、低压MOS管接到了高电压域等。IC617/IC122的Virtuoso 环境支持在VSE XL图形界面进行Assert和Circuit Check的设置,Check的结果和其他仿真结果一起直接在ADE XL界面显示,可以方便地对Check/Assert 的结果进行各种后处理,并将有Violation的器件及路径直接反标到schematic。该流程可以覆盖电路设计常用check需求,完全不依赖脚本,图形界面让工程师更容易上手,基于瞬态仿真的Dynamic Check相比其他工具更具优势。有效利用Check/Assert flow, 可以帮助避免或及早发现设计中的一些常见问题,从而减少设计迭代,该流程在TSMC 16 nm和Intel 14 nm实际项目上得到应用,很大程度地提高了设计效率。

1 Circuit Check

Circuit Check分为Static Check和Dynamic Check,前者主要基于电路拓扑结构进行检查,后者主要基于瞬态仿真结果进行检查。

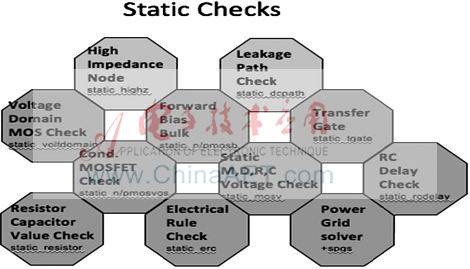

Spectre/APS/XPS支持的Static Check主要包含如图1所示的几个类型, Static Check主要在电路解析阶段基于电路拓扑结构和电压传递信息进行分析,不需要设置任何仿真类型,因此速度快,对于仿真速度几乎没有影响。

图1 Static Check

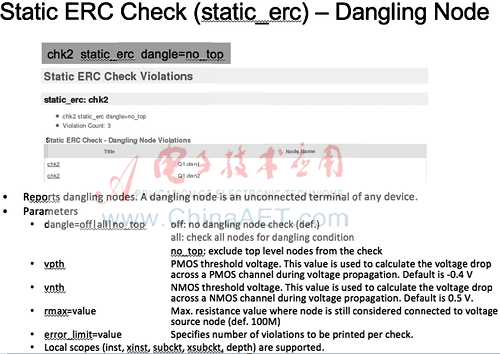

其中,static_erc 可以说是最简单实用的Static Check类型,可以用来检查dangling node,floatgate,floatbulk以及hotwell 等。Floatgate和floatbulk比较容易理解,dangling node是指任意器件的unconnected terminal;hotwell是指没有连接到电源或地的bulk node。这些都是常见的可能引入问题的连接关系或拓扑结构,如果是仿真或测试结果出错再去查,往往费时费力而且会影响产品交付周期,如果在电路设计前期能及时或尽早地发现,会很有意义。

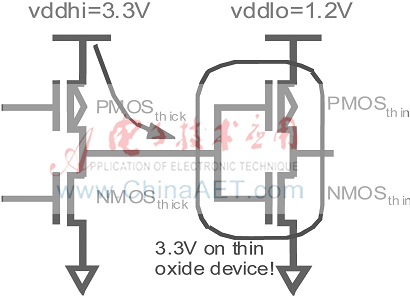

另外两个常用的Static Check是static_highz 和static_voltdomain. Static_highz从静态的角度找出到电源和地之间没有任何导电通路的节点,也就是所谓的high impedance node,如图2所示圆形节点,这是电路设计中引入不确定电位从而导致漏电的一类常见问题。Static_voltdomain从静态的角度找出电压域连接出错的问题,最常见的是低阈值电压的MOS管接到了高电压域,容易导致击穿失效的问题。如图3所示。

图2 static_highz 示例

图3 static_voltdomain示例

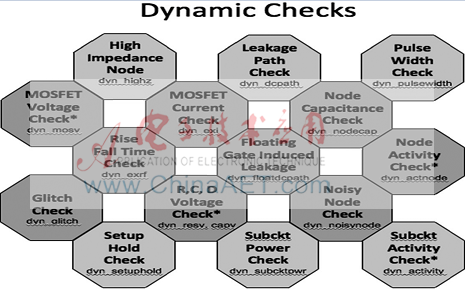

Spectre/APS/XPS支持的Dynamic Check 主要包含如图4所示的几个类型,Dynamic Check主要在电路瞬态仿真阶段基于瞬态仿真结果进行分析,检查结果和所加激励有关。

图4 Dynamic Check

前面提到的关于high impedance node的检查,除了有static_highz, 也有对应的dyn_highz, 前者是静态的,后者是动态的。

除dyn_highz以外,另外两个常用的dynamic check分别是dyn_exi 和dyn_setuphold. Dyn_exi 帮助找到在指定时间窗口内,电流超过某个指定门限的器件,这对于debug掉电模式时的漏电流问题会非常有帮助。Dyn_setuphold可以帮助检查时序问题,对于时钟和数据之间setup time或hold time不满足指定要求的会报错。关于这两个Dynamic Check,后面我们会用实际项目中用到的例子作进一步详细介绍,这里先不展开。

2 Virtuoso Check/Assertion Flow

仿真器提供仿真和上述的Circuit Check功能,Virtuoso提供设计环境,可以在不熟悉check语句语法的情况下,轻松完成整个流程,具体流程图如图5所示。使用该流程的过程会涉及VSE XL(Virtuoso Schematic Editor XL)中的Checks and assertions assistant, 以及ADE XL (Analog Design Environment XL),后面我们会用实际用例介绍具体设置和看结果的详细过程。

图5 Virtuoso Check/Assert 流程示意图

3 Dyn_setuphold 在Virtuoso Check/Assert流程中的具体应用

我们的实际项目中经常会涉及到一些custom digital设计,时序检查对这一类型的设计非常重要,最典型的就是时钟和数据之间的setup time和hold time需要满足一定的要求,dyn_setuphold check正好可以满足这一类的检查需求。下面以图6所示的最简单的DFF链路的例子来详细阐述dyn_setuphold在Virtuoso Check/Assert流程中的具体应用。

图6 Dyn_setuphold testbench 示意图

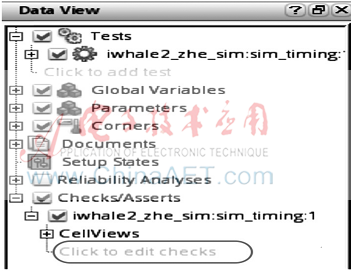

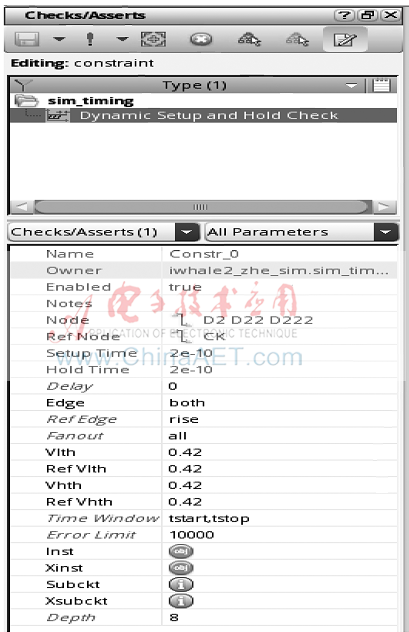

如图7所示,在ADE XL中点击‘Click to edit checks’, 会自动跳转到VSE XL界面,并打开 Checks/Asserts Assistant, 在Checks/Asserts Assistant选择并设置好dyn_setuphold check,如图8所示。

图7 Click to edit checks in ADE XL

这个例子,时钟信号是CK, 数据信号包括D2, D22 和D222,时钟周期为800 ps,设置setup time和hold time都不能小于200 ps, 如果不满足应报错。

图8 Checks/Asserts Assistant in VSE XL

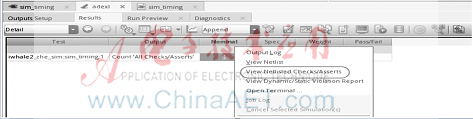

图9 View Netlisted Checks/Asserts

如图9所示,可以在ADE XL中选择‘View Netlisted Checks/Asserts’直接看到生成的Check语句,如图10所示。

图10 Netlisted Checks/Asserts

图11 Dyn_setuphold check结果

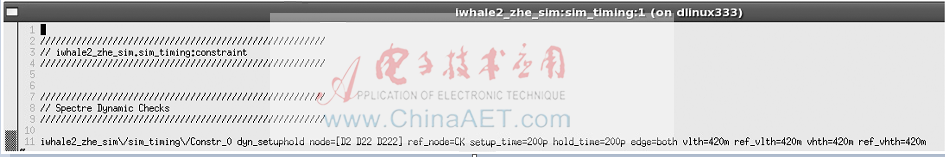

设置并进行正常的瞬态仿真,仿真结束以后,在ADE XL不仅可以看到正常的仿真结果和波形,同时还可以看到Checks/Asserts的结果,如图11所示,可以很清楚地看到信号D22有hold time violation,信号D222有setup time violation,而且可以看出每个violation发生的具体时间点,对应上升沿还是下降沿等具体信息。如图12所示,可以选择只看setup violation或只看hold violation。

如图13所示,D22和CK之间的hold time只有132.0 ps,不满足200 ps的要求,D222和CK之间的setup time只有67.94 ps,也不满足200 ps的要求,从而进一步验证了图11和图12显示的结果。

图12 Dyn_setuphold check结果—— setup violation

图13 Dyn_setuphold check结果波形

图14 Dyn_setuphold check结果波形

图15 缺省的Violation Filter

在图11和图12中点击任意一个信号,如D2,会直接跳转到VSE 窗口,放大并点亮D2 信号,如图14所示,这是ADE XL和schematic之间的cross-probing功能,方便快速找到有violation的信号。

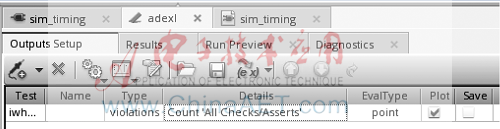

在ADE XL中,可以添加一类新的表达式,名为‘Violation Filter’,通过这种表达式,可以很方便地对Checks/Asserts的结果进行统计,如图15所示,新添加的Violation Filter表达式缺省统计所有的Checks/Asserts violation一共有多少个,可以很方便地对统计内容进行调整。

4 Dyn_exi 在Virtuoso Check/Assert流程中的具体应用

接下来,我们继续讨论在另一个项目中,如果利用dyn_exi debug解决power down模式的漏电流问题。

问题现象是电路前仿真结果正常,后仿真在power down模式会有异常的漏电流,电路设计工程师花了很长时间都没有找出这个漏电流是如何引起的。

对于这一类问题,有一个很方便的方法,就是通过dyn_exi check找出在指定的时间窗口,哪个或哪些器件的电流超出了定义的门限,找到这个或这些器件之后,trace其端口电压,可以很快找出问题的原因。

Dyn_exi check具体的设置语句如图16所示。

图16 Dyn_exi 设置语句

通过设置dyn_exi check,找到漏电的器件,并trace其端口电压之后,我们发现图17所示电路图中信号ca1有异常。VDDESD是2.8 V,但是后仿结果中ca1是0 V。

图17 Dyn_exi 示例局部电路原理图

根据上述线索,电路设计工程师提供简化的test case重现问题,然后我们发现图17中的电阻R0在后仿真用到的rcc extraction view中出现了连接关系断掉的情况。如图18所示,63个串联电路由于串联节点出错没有彻底连通,从而导致出错。

图18 Dyn_exi 示例局部网表

这是抽取工具引起的,找到原因以后,通过抽取工具得到了及时有效地解决。

5 Static_erc在Virtuoso Check/Assert流程中的具体应用

下面我们再举另一个实际项目的例子,关于如何利用static_erc check debug后仿真结果不正确的问题。

问题现象也是电路前仿真结果正常,后仿真结果异常,电路设计工程师怀疑后仿网表有问题, 经过一段时间debug以后,发现图19中的in(input pin)后面接的反向器I0的输出out1有错,in 为0电平时,out1仍为0电平,反向器没有正常工作。

图19 Static_erc 示例局部电路原理图1

我们在这个项目上采用了static_erc check, 试图找出后仿网表中是否存在dangling node。

用static_erc找dangling node的check设置如图20所示。

图20 Static_erc—dangling node设置

如图21所示,通过static_erc check, 我们很快找到后仿网表中存在dangling node,反向器gate端的寄生电阻导致PMOS 和NMOS的gate和input pin(in)都没有连通,从而导致出错。这个也是抽取工具的问题,定位具体原因以后,也很快通过抽取工具得到了及时有效的解决。

图21 Static_erc—dangling node示例局部电路原理图2

6 总结

本文简单介绍了Spectre/APS/XPS 支持的Circuit Check类型及其原理,以及Virtuoso Checks/Asserts 完整流程,通过dyn_setuphold, dyn_exi 和static_erc 3种最常用的check类型,详细阐述了如何设置Circuit Check,如何看check 结果,以及如何方便地对check结果进行后处理。通过这3个例子,我们可以清楚地看到Circuit Check如何在具体项目中得以应用,并分别适用于解决哪些类型的问题。可以看出,该流程能够覆盖电路设计常用check需求,完全不依赖脚本,图形界面让工程师更容易上手,基于瞬态仿真的Dynamic Check相比其他工具更具优势。有效利用Check/Assert flow, 可以帮助避免或及早发现设计中的一些常见问题,从而减少设计迭代,该流程在TSMC 16nm和Intel 14nm实际项目上得到应用,从而很大程度地提高了设计效率。