蔡洁明,魏敬和

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

摘要:提出了一种适用于高速1553总线的分立器件收发器电路设计方法,解决了传统1 MHz 1553收发器无法与10 MHz协议处理器接口的问题。与其他方案相比,由于采用的是分立器件搭建,不改变原有的总线结构,不用改换线缆及接口方式,节省了大量成本与时间,实现起来灵活方便,同时具有很好的通用性和强大的可扩展性。

关键词:分立器件;高速1553总线;LDMOS;滤波器;比较器

中图分类号:TN710文献标识码:ADOI: 10.19358/j.issn.1674 7720.2016.20.009

引用格式:蔡洁明,魏敬和. 高速1553总线分立器件收发器设计[J].微型机与应用,2016,35(20):34 36.

0引言

MIL-STD-1553数据总线因其高可靠性特诸多优点被广泛应用于航空、航天等多个领域。在过去的半个多世纪,它实现了传感器、武器等各种电子装备的信息共享与传输。但随着更快处理器的诞生以及封装的小型化和软件技术的革新,1553B仅仅1 Mb/s的数据传输速度无疑成为了信息数据传输的瓶颈,一种更快速度的传输方式应运而生[1-2]。1553总线历经了1553A、1553B再到1553C的三个重要的发展阶段,传输速度也从最先的1 Mb/s变成了10 Mb/s甚至更高。目前国外已经有了较为成熟的1553C产品,但我国在高速1553总线方面的研究尚处于起步阶段。由于国外在高速1553总线上采取技术封锁,因此国内只能在研究1553B总线的基础上开发自己的1553C产品。

除了支持高速数据处理的1553C协议处理器外,相应的高速收发器电路由于与外部总线相连,其稳定性和可靠性至关重要,因而成为整个1553C总线电路设计的关键[3]。目前高速1553收发器的研制开发单位主要集中在部分科研院所和大学,但由于国内尚未出台针对高速1553收发器的标准,尽管有高速1553收发器电路问世,但各家产品的性能指标不尽相同。从实现形式上大致可以把目前开发出的1553高速收发器分为两类:一类是基于原低速1553收发器进行设计参数的调整,使其工作于10 MHz甚至更高速率;另一类是采用市场上其他通用型收发器替代1553收发器,如485总线收发器等,其速率也可以达到10 MHz[4]。但两种方案均存在一定的缺陷:采用更改设计参数的方式由于受到原电路设计的局限,调整幅度不能太大,电路通常需要进行全套改版,需要投入的成本很高。采用其他通用型收发器的方案尽管芯片本身不用重新设计,但原来的传输介质都需要更换,整个系统需要重新布局,投入的成本也不容小觑。

本文设计的1553总线收发器克服了上述两种方案的缺陷,采用市场上常用的分立器件进行搭建,价格较低且容易采购,可以利用原系统进行通信,无需作任何调整,兼顾了电路设计与后期重新布局的成本。此外,该设计还具有很好的可扩展性,当收发器参数需要进行调整时,只需简单更换型号不同的分立器件即可,既方便了调试,又降低了成本。

1电路组成及原理

本文设计的分立器件收发器的典型工作速率为10 MHz,由发送器与接收器两部分组成。

发送器与协议处理器衔接,完成10 MHz曼彻斯特码的发送,它由电压转换驱动器电路、高速功率晶体管LDMOS(NMOS)及一定阻值和容值的电阻电容构成。

电压转换驱动器电路采用TI公司的SN74LVC2T45,它是一款双向带三态输出的电压转换驱动器[5]。由于协议处理器送给发送器的为3.3 V信号,为了保证数据高速传输时LDMOS的漏端有足够大的电流,需要将栅极的电压抬高。SN74LVC2T45可以将10 MHz、3.3 V的电平信号转换为10 MHz、5 V的信号。同时,其中一个电源端口VCCA可以用作发送器的使能端,用于控制发送器是否进入工作状态。

LDMOS采用NXP公司的高速功率晶体管BLF6G21-10G,其开关速度可达2 200 MHz,开启电压1.9 V,且在栅源电压达到5.65 V时,漏极电流可达3.1 A,输入输出电容在几pF到十几pF之间[6],可以满足发送器设计要求。

隔离变压器采用国内某研究所定制的10 MHz变压器。该变压器专为高速1553收发器设计,经过长期的寿命及可靠性试验,各项参数指标满足高速1553总线传输要求。要注意的是,由于输出端采用的是NMOS,变压器输入端的中间抽头(2脚)必须接+5 V的电源。

发送器的原理框图如图1所示。

如图1所示的分立器件发送器,协议处理器产生一对差分信号Txa、Txa_n送至SN74LVC2T45的A1、A2端口,SN74LVC2T45的电源端VCCA通过跳线选择3.3 V电源或GND,以控制发送器的开启与关断,电源端VCCB接5.0 V电源,这是由于协议处理器采用3.3 V标准的端口电压,为了保证LDMOS有足够大的电流以驱动下一级,将协议处理器输出的信号经过电平转换器件转换至5 V电压。方向控制端DIR接高电平,使数据信号由A端送至B端。接地端GND与电路板的地端相连。经过电平转换后的信号通过10 Ω电阻以减少信号反射。接着两路差分信号被分别送至两个LDMOS管的栅极(Pin2),源极(Pin3)跟衬底连在一起接到地,漏极(Pin1)作为输出并串接2 Ω电阻至变压器的初级端(Pin1、Pin3),LDMOS的栅极与漏极跨接100 pF的反馈电容用于调整信号的阶梯现象。信号经过隔离变压器至次级,负载接于隔离变压器的引脚5与引脚7之间。发送器的工作原理如下。

当Txa对应的曼码为高电平时,Txa_n对应的曼码应为低电平,这时,图1中的第一功率MOS管导通,于是变压器1号抽头被拉至地,电流从中间抽头(Pin2)往1号抽头流,在变压器输入端的3号抽头与中间抽头之间耦合产生方向相反的电流,这样1、3号抽头之间就形成了正负电平的曼码;同理,当Txa_n对应于曼码为高电平时,Txa对应的曼码应为低电平,这时,第二功率MOS管导通,于是变压器3号抽头被拉至地,电流从中间抽头往3号抽头流。在变压器输入端的1号抽头与中间抽头之间耦合产生相反的电流,这样1、3号抽头之间同样形成了正负电平的曼码。

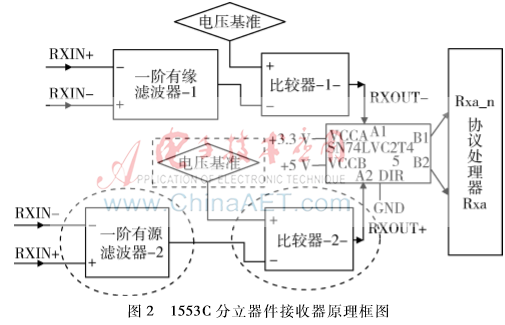

接收器部分从1553总线上接收10 MHz的曼彻斯特码,通过滤波、比较、电平转换产生与协议处理器匹配的TTL电平信号。接收器原理框图如图2所示。

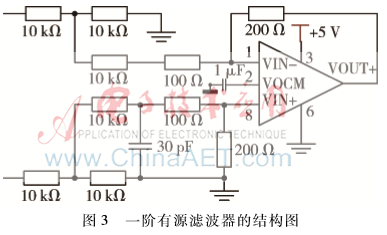

滤波器采用TI公司的高速运算放大器THS4521搭建的一阶有源滤波器。THS4521带宽可以达到145 MHz,转换速率达到490 V/μs[7],可以满足要求。一阶有源滤波器的结构如图3所示。

发送器输出的差分信号经1/2分压后连接至其差分输入端(Pin1、Pin8),以降低共模电压信号使运放能够正常响应。电源Vs+(Pin3)接+5 V,Vs-(Pin6)接地,共模电压输入端VOCM(Pin2)接0.1 μF电容到地,以降低管脚上的耦合噪声。

对于一阶有源滤波器,其截止频率为:

通过选取合适的R、C值可以使一定频率范围内的信号通过。为了避免高频噪声信号对正常曼码的影响,在这里选取: 代入式(1)有:

代入式(1)有:

计算得到截止频率为fC=53 MHz,可以满足五次谐波分量通过,更高频率的谐波(大多是噪声)被滤走。

为了能够使比较器有较高的灵敏度,需要将滤波器的输出信号进行放大,这里选择放大倍数为6。因此,在运算放大器的正输出VOUT+(Pin4)与负输入端VIN-(Pin1)跨接反馈电阻RF。

运算放大器的放大倍数由下式决定:

有源滤波器的输出被接至比较器,比较器采用ADI公司的超快速比较器AD8611,该器件输入端的频率可以达到100 MHz,且在5 V工作电压下有4 ns的延时[8]。比较器中的电压基准采用NS的LM4120-1.8,它能提供稳定的1.8 V输出电压基准[9]。比较器的门限定为1.8 V,因此当滤波器输出波形的电平高于1.8 V时,输出电平为高(+5 V),输出电平低于1.8 V时,输出电平为低(0 V)。这样,经过总线传输之后的曼彻斯特码就被滤波整形,防止噪声信号使协议处理器产生误操作。

最后,输出的5 V信号要经过电平转换电路,将其转换为协议处理器可以接收的3.3 V电平信号。输入端A1、A2分别接RXOUT-、RXOUT+,与发送器中的电压转换驱动器接法不同的是,接收器不需要使能控制,故VCCA接固定的3.3 V电平,DIR接地,以使数据信号由B端送至A端。输出的信号B1、B2被分别送至协议处理器的Rxa_n、Rxa端口。

2电路验证及测试结果

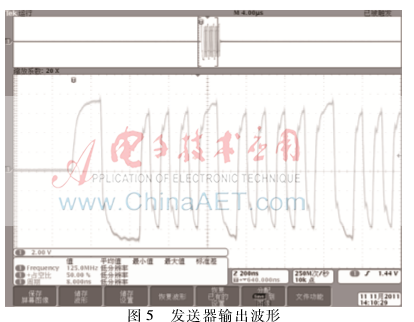

在变压器的差分输出端串接55 Ω电阻,再跨接35 Ω负载,如图4所示。根据规范要求,在直接耦合的情况下,负载两端电压Vpp值Uout应在7~9 V之间[10]。

发送器的输出波形如图5所示。

经过比较器之后的波形如图6所示。

3结束语

本文提出了一种针对10 MHz 1553总线协议处理器的接收发送电路,解决了1 MHz 1553收发器无法与10 MHz协议处理器接口的问题。由于采用的是分立器件搭建,省去了昂贵的流片费用,实现起来灵活方便,即便是以后需要更高速度的收发器,也只需要调整滤波器的滤波电阻电容就可以满足要求,具有很好的通用性和强大的可扩展性。它不改变原有的总线结构,不用改换线缆及接口方式,节省了大量成本与时间。随着更快处理器的诞生、封装的小型化以及软件技术的革新,信息的高速传输与实时共享已经成为一种必然趋势,采用分立器件的高速1553收发器电路无疑将代替传统的收发器以适应快速发展的总线传输需求。

参考文献

[1] 熊华钢.1553B总线通信技术的应用与发展[J]. 电子技术应用,1997,23(8):27-28.

[2] 刘士全,黄正,蔡洁明,等. 1553B总线应用竞争访问时序分析[J]. 微型机与应用,2015,34(1):69-71.

[3] 李海军,牟俊杰,孙海文. 高速1553B总线控制器通信管理系统设计[J]. 现代电子技术,2014,37(17):16-18.

[4] KELLER J. Rebirth of the 1553 databus[EB/OL].(2006-02-01)[2016-04-29]http://www.militaryaerospace.com/index.html.

[5] TI. Dual bit dual supply bus transceiver with configurable voltage translation and 3 state outputs[Z]. 2007.

[6] NXP. BLF6G21 10G, power LDMOS transistor product data sheet[Z]. 2009.

[7] TI. Very low power, negative rail input, rail to rail output, fully differential amplifier[Z]. 2010.

[8] ADI. Ultrafast, 4 ns Single Supply Comparators[Z]. 2006.

[9] NS. Precision micropower low dropout voltage reference[Z]. 2005.

[10] DDC. ACE/mini ACE series BC/RT/MT advanced communication engine integrated 1553 terminal user’s guide[Z]. 2008.